存储系统的制作方法

本发明构思的实施例一般地涉及半导体集成电路,更具体地,涉及能够直接访问主机的处理器高速缓存的存储系统。

背景技术:

1、一个或更多个半导体存储器件可用于各种具体化的数据存储设备中。一些数据存储设备包括一个或更多个固态驱动器(ssd)。与包括一个或多个硬盘驱动器(hdd)的设备相比,这种数据存储设备展现设计和/或性能优势。在这方面,包括ssd的数据存储设备不具有移动机械部件,提供了更高的数据访问速度同时具有提高的稳定性和耐久性,和/或需要降低了的总功耗。对于包括ssd的数据存储设备存在许多当代和新兴的应用,例如,个人计算机、膝上型计算机、交通工具(如汽车、卡车、飞机和无人机)、电器、个人数字平台、通信系统节点、医疗设备等。

2、本领域技术人员将认识到用于在系统、组件、设备(如输入/输出(i/o)设备、存储器和/或高速缓存)之间传送(例如,发送和/或接收)数据的各种方法或方法论。这些方法的现成示例例如包括直接存储器存取(dma)、直接高速缓存访问(dca)和数据直接i/o(ddio)。

技术实现思路

1、本发明构思的实施例提供了能够直接且更有效地将主机请求的数据写入中央处理单元(cpu)高速缓存的存储系统。

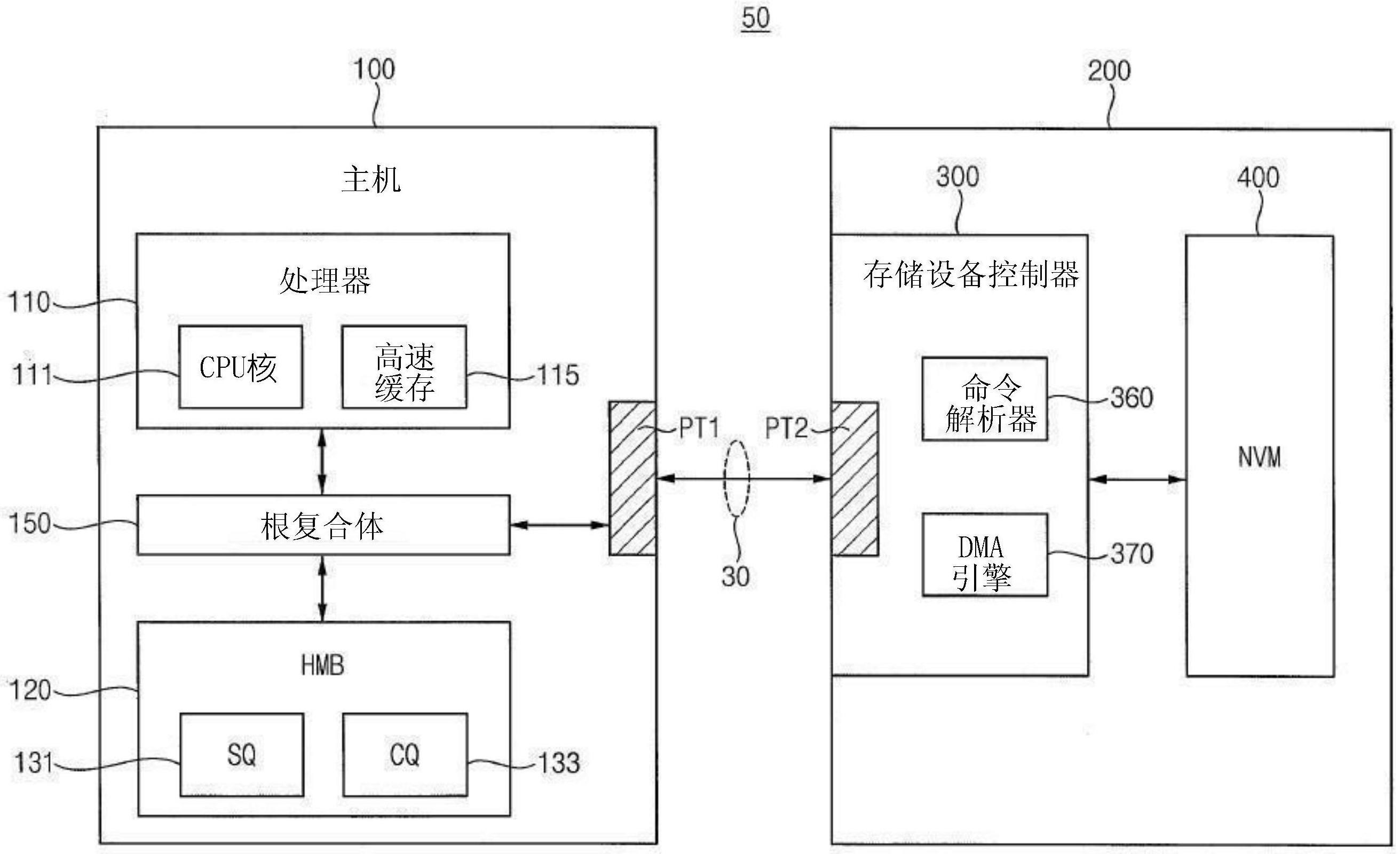

2、根据一些实施例,一种存储系统包括:主机,其中所述主机包括主机处理器和主机存储器缓冲器,所述主机处理器包括控制所述主机的操作的中央处理单元(cpu)核和专供所述cpu核使用的高速缓存,并且所述主机存储器缓冲器包括提交队列和完成队列,以及存储设备,所述存储设备通过链路连接到所述主机,使用事务层分组(tlp)与所述主机通信,并且包括至少一个非易失性存储器件(nvm)和控制所述至少一个nvm的存储设备控制器。所述主机被配置为向所述提交队列写入指示目的地的快速非易失性存储(nvme)命令,以及所述存储设备控制器被配置为:从所述nvm读取数据,响应于与所述目的地相关联的目的地信息直接访问所述高速缓存,并将所读取的数据存储在所述高速缓存中。

3、根据一些实施例,一种存储系统包括:主机,以及,存储设备,所述存储设备通过链路与所述主机连接,其中所述存储设备使用事务层分组(tlp)与主机通信。所述主机包括:主机处理器,所述主机处理器被配置为控制所述主机的操作,所述主机处理器包括中央处理单元(cpu)核和专用于所述cpu核的高速缓存,其中所述高速缓存以高速缓存行为单位进行交换,以及,主机存储器缓冲器,所述主机存储器缓冲器包括提交队列和完成队列。所述存储设备包括:至少一个非易失性存储器件(nvm),所述至少一个nvm被配置为存储数据,以及存储设备控制器,所述存储设备控制器被配置为控制所述至少一个nvm的操作,其中,响应于从所述主机接收到的与请求所述高速缓存的部分更新的读取命令相对应的快速非易失性存储(nvme)命令,所述存储设备控制器被配置为从所述nvm读取相应数据,向所述高速缓存提供所读取的数据中的与要被更新的数据相对应的目标数据,并且向所述主机存储器缓冲器提供所述读取的数据中的除了所述目标数据之外的非目标数据。

4、根据一些实施例,一种存储系统包括:主机,以及存储设备,所述存储设备通过快速外围组件互连(pcie)链路与所述主机连接,其中所述存储设备使用事务层分组(tlp)与所述主机通信。所述主机包括:主机处理器,所述主机处理器被配置为控制所述主机的操作,其中所述主机处理器包括中央处理单元(cpu)核和专用于所述cpu核的高速缓存;主机存储器缓冲器,所述主机存储器缓冲器包括提交队列;以及,根复合体,所述根复合体连接到所述主机处理器和所述主机存储器缓冲器。所述存储设备包括:至少一个非易失性存储器件(nvm),所述至少一个nvm被配置为存储数据;以及,存储设备控制器,所述存储设备控制器被配置为控制所述nvm,其中,响应于从所述主机接收到的快速非易失性存储(nvme)命令以及对应于所述高速缓存的与所述nvme命令相关联的目的地,所述存储设备控制器被配置为:从所述nvm读取数据,通过所述根复合体访问所述高速缓存,并将所读取的数据存储在所述高速缓存中;以及,响应于指示存储在所述高速缓存中的数据的要被更新的高速缓存未命中,或者响应于未存储在所述高速缓存或所述主机存储器缓冲器中的新数据被请求,所述主机处理器被配置为在所述nvme命令的一部分中设置与所述目的地相关联的目的地信息,并将所述nvme命令存储在所述提交队列中。

5、根据一些实施例,在存储系统中,当存储在cpu高速缓存中的数据要被更新或新数据要被存储在cpu高速缓存中时,存储设备可以将与要更新的数据或新数据相关联的目的地信息包括在tlp中,并且主机可以更新存储在高速缓存中的数据的至少一部分或者通过直接访问所述高速缓存将新数据存储在高速缓存中以增加高速缓存命中率并提高性能。此外,当存储在主机存储器缓冲器中的数据要被更新或新数据要被存储在主机存储器缓冲器中时,存储系统可以对要被更新的数据或新数据进行dma,以防止存储器带宽的使用的增加和等待时间的增加。

技术特征:

1.一种存储系统,所述存储系统包括:

2.根据权利要求1所述的存储系统,其中,所述存储设备控制器还包括:

3.根据权利要求2所述的存储系统,其中,所述tlp包括分组报头,并且所述分组报头包括:指示前缀是否存在的格式字段、指示所述tlp的类型的类型字段、指示是否存在tlp处理提示的提示字段和处理提示字段,以及

4.根据权利要求2所述的存储系统,其中,所述tlp包括分组报头,并且所述分组报头包括:指示前缀是否存在的格式字段、指示所述tlp的类型的类型字段、指示是否存在tlp处理提示的提示字段和处理提示字段,以及

5.根据权利要求4所述的存储系统,其中,所述主机接口还被配置为将所述引导标签字段包括在存储器写入请求报头的第一字节到第八字节中的第七字节中。

6.根据权利要求1所述的存储系统,其中,所述存储设备控制器还被配置为:通过门铃信令通知从所述主机接收与所述命令相关联的通知,从所述提交队列取出所述命令,执行与取出的所述命令相对应的读取操作,将完成命令写入所述完成队列,并向所述主机发送中断信号。

7.根据权利要求6所述的存储系统,其中,所述存储设备控制器还被配置为通过向所述主机发送存储器读取请求并从所述主机接收所述命令来取出所述命令。

8.根据权利要求6所述的存储系统,其中,所述主机还包括连接到所述主机处理器和所述主机存储器缓冲器的根复合体,以及

9.根据权利要求1所述的存储系统,其中,所述主机处理器被配置为响应于高速缓存未命中或响应于新数据要被存储,在所述nvme命令的一部分中设置目的地信息,并将所述nvme命令存储在所述提交队列中,其中所述高速缓存未命中指示存储在所述高速缓存中的数据要被更新,其中所述新数据未被存储在所述高速缓存中或所述主机存储器缓冲器中,

10.根据权利要求9所述的存储系统,其中,所述nvme命令是nvme读取命令,并且

11.一种存储系统,所述存储系统包括:

12.根据权利要求11所述的存储系统,其中,所述存储设备控制器包括:

13.根据权利要求12所述的存储系统,其中,所述tlp包括分组报头和用于存储所述读取的数据的有效载荷,

14.根据权利要求13所述的存储系统,其中,所述主机接口还被配置为将所述引导标签字段包括在存储器写入请求报头的第一字节到第八字节中的第七字节中。

15.根据权利要求12所述的存储系统,其中,所述主机还包括连接到所述主机处理器和所述主机存储器缓冲器的根复合体,

16.根据权利要求15所述的存储系统,其中,所述高速缓存包括多个高速缓存行,以及

17.根据权利要求15所述的存储系统,其中,所述高速缓存包括多个高速缓存行,

18.根据权利要求11所述的存储系统,其中,所述存储设备控制器还被配置为:通过门铃信令通知从所述主机接收与所述nvme命令相关联的通知,从所述提交队列取出所述nvme命令,响应于所取出的nvme指令执行读取操作,将完成命令写入所述完成队列,并向所述主机发送中断信号。

19.根据权利要求11所述的存储系统,其中,所述存储设备控制器还被配置为使用nvme接口与所述主机通信,以及

20.一种存储系统,所述存储系统包括:

技术总结

本申请公开了一种存储系统。该存储系统包括主机和存储设备。主机包括主机处理器和主机存储器缓冲器,其中主机处理器包括控制主机的操作的CPU核和专供CPU核使用的高速缓存。主机存储器缓冲器包括提交队列和完成队列。存储设备通过链路连接到主机,并使用事务层分组(TLP)与主机通信。存储设备包括非易失性存储器件(NVM)和存储设备控制器,其中主机将指示目的地的快速非易失性存储(NVMe)命令写入提交队列,存储设备控制器从NVM读取数据,响应于与目的地相关联的目的地信息直接访问高速缓存,并将读取的数据存储在高速缓存中。

技术研发人员:崔赫埈,李正浩,刘永健,郑园燮

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!