超导量子比特自电容小型化设计方法及超导量子比特自电容

本发明属于超导量子计算,特别涉及一种超导量子比特自电容小型化设计方法及超导量子比特自电容。

背景技术:

1、超导量子比特自提出以来受到广泛关注,被认为是未来实现大规模实用化量子计算的最佳候选体系之一。当前的超导量子比特设计采用大的共面平行板电容器,用于稀释非晶界面电介质的能量参与。该电容结构存在以下问题:1、大尺寸的单量子规模以及微波设计的复杂性。平行板电容之间的寄生电容耦合会导致杂散量子比特耦合,增加相干误差,又影响到量子比特的保真度。2、超导量子比特芯片集成度受限。容错量子计算需要数量庞大的物理比特实现,在可预见的将来,超导量子芯片中的比特数目将迅速增加,因而对超导量子芯片的集成度要求更高。由于目前单一芯片上的量子比特受限,量子比特的尺寸也因此受到限制。3、集成度增加带来的问题:电荷噪声、电路串扰、损耗,影响着超导量子比特的性能表现。

技术实现思路

1、为此,本发明提供一种超导量子比特自电容小型化设计方法及超导量子比特自电容,在保持超导量子比特相干时间的同时来实现对自电容的小型化设计来满足当前超导量子比特芯片集成中的应用。

2、按照本发明所提供的设计方案,提供一种超导量子比特自电容小型化设计方法,包含如下内容:

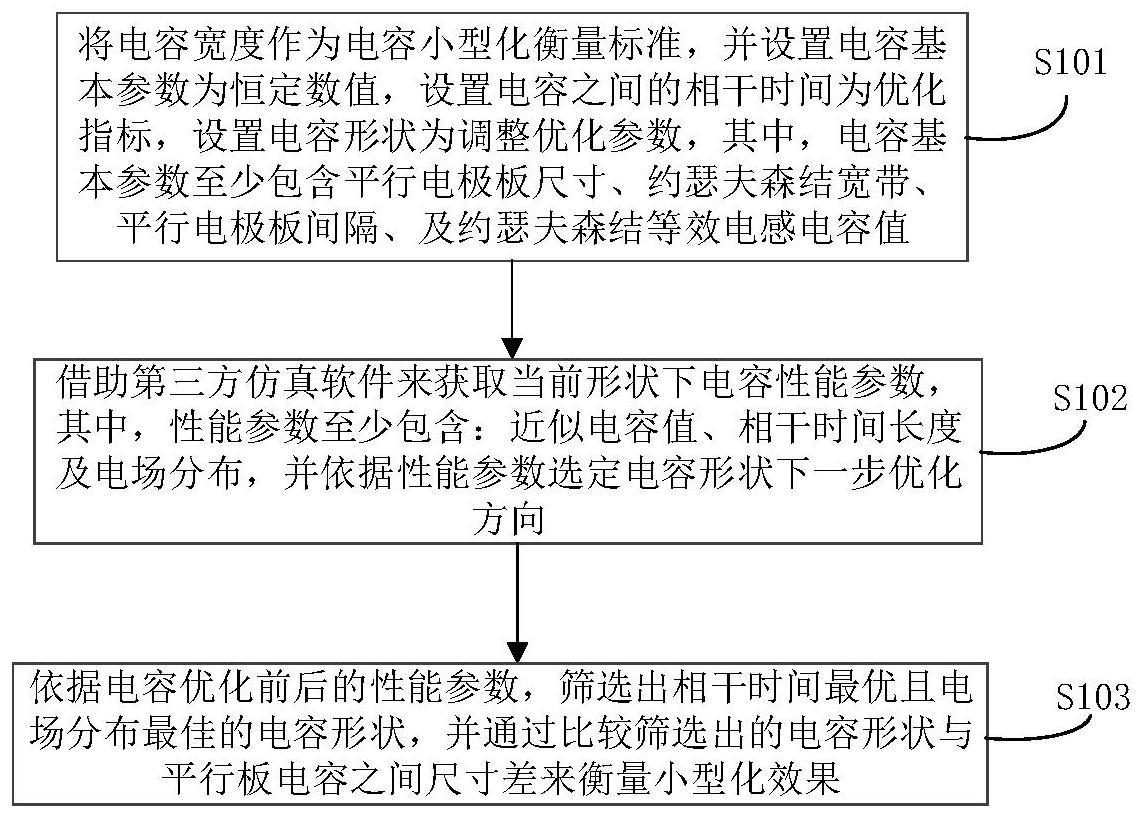

3、将宽度作为电容小型化衡量标准,并设置电容基本参数为恒定数值,设置电容之间的相干时间为优化指标,设置电容形状为调整优化参数,其中,电容基本参数至少包含平行电极板尺寸、约瑟夫森结宽带、平行电极板间隔、及约瑟夫森结等效电感电容值;

4、借助第三方仿真软件来获取当前形状下电容性能参数,其中,性能参数至少包含:近似电容值、相干时间长度及电场分布,并依据性能参数选定电容形状下一步优化方向;

5、依据电容优化前后的性能参数,筛选出相干时间最优且电场分布最佳的电容形状,并通过比较筛选出的电容形状与平行板电容之间尺寸差来衡量小型化效果。

6、作为本发明中超导量子比特自电容小型化设计方法,进一步地,借助第三方仿真软件来获取当前形状下电容性能参数中,通过调整电容形状来改变超导量子比特性质,并借助q3d模型仿真获取当前电容形状下的麦克斯韦电容矩阵,依据电容矩阵和lom超导量子比特仿真得到近似电容值和相干时间长度;通过建立电场仿真图来分析当前形状下电容的电场分布和介电损耗。

7、作为本发明中超导量子比特自电容小型化设计方法,进一步地,电容形状优化方向包含:平行电极板板宽尺寸缩减及形状调整。

8、作为本发明中超导量子比特自电容小型化设计方法,进一步地,电容形状优化方向还包含:平行电极板之间凸起数量及形状调整。

9、进一步地,本发明还提供一种超导量子比特自电容,采用平行板电容结构,利用上述的方法来实现设计,包含:第一电极板,第二电极板,位于第一电极板和第二电极板之间的电介质,及设于第一电极板和第二电极板上的控制线,在第一电极板和第二电极板两者的内侧中央部位设置有相互对称交织并用于防止电容缺失的扩展凸起组件;所述扩展凸起组件包含分设在第一电极板内侧面和第二电极板内侧面上且相对应设置的凸起和凹槽。

10、作为本发明超导量子比特自电容,进一步地,所述凸起采用截面为弧状的凸起结构。

11、作为本发明超导量子比特自电容,进一步地,第二电极板上的凸起设置在第二电极板内侧面中间,第一电极板的凹槽设置在第一电极板内侧面中间,且第二电极板上的凹槽沿第二电极板的凸起中心线对称设置,第一电极板的凸起沿第一电极板凹槽中心线对称设置。

12、作为本发明超导量子比特自电容,进一步地,所述扩展凸起组件上还包含:分别设置在第一电极板和第二电极板两者内侧面上用于增加消相干时间的三角形电容凸起。

13、作为本发明超导量子比特自电容,进一步地,所述三角形电容凸起分设在第一电极板内侧面中间凹槽中心和第二电极板内侧面中间凸起中心,或分别设在第一电极板内侧面中间凸起中心和第二电极板内侧面中间凹槽中心。

14、作为本发明超导量子比特自电容,进一步地,所述三角形电容凸起采用截面为等腰三角形的结构。

15、本发明的有益效果:

16、本发明保证超导量子比特性质的前提下,通过改变电容形状,在大的共面平行板里添加圆角、三角结构等,通过对电容形状小型化设计来改变超导量子比特的性质,满足超导量子比特芯片集成中的应用;小型化设计出来的超导量子比特自电容,在保证电容性能的前提下,能够通过扩大平行板电容表面尺寸,较小介电损耗,并在一定程度上增大电容值,便于量子芯片集成中的应用。

技术特征:

1.一种超导量子比特自电容小型化设计方法,其特征在于,包含如下内容:

2.根据权利要求1所述的超导量子比特自电容小型化设计方法,其特征在于,借助第三方仿真软件来获取当前形状下电容性能参数中,通过调整电容形状来改变超导量子比特性质,并借助q3d模型仿真获取当前电容形状下的麦克斯韦电容矩阵,依据电容矩阵和lom超导量子比特仿真得到近似电容值和相干时间长度;通过建立电场仿真图来分析当前形状下电容的电场分布和介电损耗。

3.根据权利要求1或2所述的超导量子比特自电容小型化设计方法,其特征在于,电容形状优化方向包含:平行电极板板宽尺寸缩减及形状调整。

4.根据权利要求3所述的超导量子比特自电容小型化设计方法,其特征在于,电容形状优化方向还包含:平行电极板之间凸起数量及形状调整。

5.一种超导量子比特自电容,采用平行板电容结构,其特征在于,利用权利要求1所述的方法来实现设计,包含:第一电极板,第二电极板,位于第一电极板和第二电极板之间的电介质,及设于第一电极板和第二电极板上的控制线,在第一电极板和第二电极板两者的内侧中央部位设置有相互对称交织并用于防止电容缺失的扩展凸起组件;所述扩展凸起组件包含分设在第一电极板内侧面和第二电极板内侧面上且相对应设置的凸起和凹槽。

6.根据权利要求1所述的超导量子比特自电容,其特征在于,所述凸起采用截面为弧状的凸起结构。

7.根据权利要求1所述的超导量子比特自电容,其特征在于,第二电极板上的凸起设置在第二电极板内侧面中间,第一电极板的凹槽设置在第一电极板内侧面中间,且第二电极板上的凹槽沿第二电极板的凸起中心线对称设置,第一电极板的凸起沿第一电极板凹槽中心线对称设置。

8.根据权利要求1所述的超导量子比特自电容,其特征在于,所述扩展凸起组件上还包含:分别设置在第一电极板和第二电极板两者内侧面上用于增加消相干时间的三角形电容凸起。

9.根据权利要求8所述的超导量子比特自电容,其特征在于,所述三角形电容凸起分设在第一电极板内侧面中间凹槽中心和第二电极板内侧面中间凸起中心,或分别设在第一电极板内侧面中间凸起中心和第二电极板内侧面中间凹槽中心。

10.根据权利要求8所述的超导量子比特自电容,其特征在于,所述三角形电容凸起采用截面为等腰三角形的结构。

技术总结

本发明属于超导量子计算技术领域,特别涉及一种超导量子比特自电容小型化设计方法及超导量子比特自电容,将电容宽度作为电容小型化衡量标准,并设置电容基本参数为恒定数值,设置电容形状为调整优化参数;借助第三方仿真软件来获取当前形状下电容性能参数,其中,性能参数至少包含:近似电容值、相干时间长度及电场分布,并依据性能参数选定电容形状下一步优化方向;依据电容优化前后的性能参数,筛选出相干时间最优且电场分布最佳的电容形状,并通过比较筛选出的电容形状与平行板电容之间尺寸差来衡量小型化效果。本发明在保持超导量子比特相干时间的同时,能够实现对自电容的小型化设计,以满足当前超导量子比特芯片集成中的应用。

技术研发人员:张潮洁,王卫龙,单征,刘福东,赵炳麟,王立新,穆清,费洋扬,孟祥栋,孙回回,王淑亚,杨天,何昊冉,袁本政

受保护的技术使用者:中国人民解放军战略支援部队信息工程大学

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!