一种CSA进位共享加法器及其实现方法与流程

本发明涉及数字电子器件,具体是指一种csa进位共享加法器及其实现方法。

背景技术:

1、高速计算是加法器领域追求的发展方向,通过减少逻辑单元数量,减少门延迟可以提升加法器的计算速度。

技术实现思路

1、本发明要解决的技术问题是目前的加法器逻辑结构设计存在冗杂的问题,国际通用的逻辑表达式处于逻辑门设计层面,仅使用2种信号进行运算,无法解决深入mos架构后出现的大量新情况,存在功耗极大、晶体管电平不稳,并最终烧毁器件的隐患。

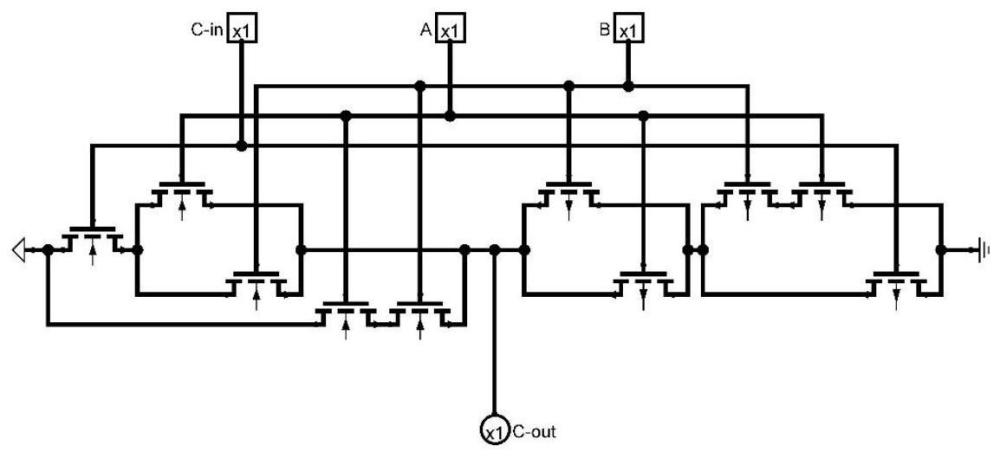

2、为解决上述技术问题,本发明提供的技术方案为:一种csa进位共享加法器及其实现方法,包括进位器、全加器和整合:

3、进位器,进位器逻辑步骤如下:1)将公式cout=cin*(a+b)+a*b转化为新公式,得到公式:

4、

5、并导出新逻辑门,且在n次公式嵌套后可导出第n+1位进位门;

6、2)将高低电平反置,得到公式:

7、

8、3)低位的进位信息隐含于更高位的进位门其当中,由于公式的形式为嵌套公式,低位的进位公式被完整的保留在高位公式当中,故低位进位信息可从高位进位门之中引导出来;

9、4)在结果为1时对某一信号进行阻断;

10、5)因为不可抗的进位指示信号,故在时应对l*(cin*(a1+b1)+a1*b1)进行阻断。由于l*(cin*(a1+b1)+a1*b1)和信号共联形成输出节点,故在阻断时应将此2个信号视为一个结构,并将阻断结构与其串联,阻断结构为的反结构,得到公式:

11、

12、6)将阻断结构的控制信号输入改为反码形式,反码可由触发器或寄存器中直接获取;

13、全加器,全加器的异或运算表达式:

14、

15、改为新公式:

16、

17、展开,得:

18、

19、合并,得:

20、

21、最后导出逻辑门;

22、整合,将进位器逻辑门与全加器逻辑门进行整合,全加器的进位接收为反码形式。

23、本发明与现有技术相比的优点在于:本方案由超前进位加法器优化而来,第一位晶体管数量为20,此后每一位为22,总延迟为2t,输入端下方为一进位生成门,设计思路来源为超前进位加法器的进位生成机制,并由公式加入特殊情况阻断设计而得,全加器为自主设计的全新多位并行异或器反a1之类即为反码,由触发器或寄存器直接提供,续位方式为直接向后连接单元,由于现有方案(超前进位加法器)的晶体管数量表达式为k倍n的平方,而本方案为k倍n,故每扩展一位都可以节省平方级数的晶体管数量比原有的技术方案减少了一半的晶体数量,增加了运算速度。

技术特征:

1.一种csa进位共享加法器及其实现方法,其特征在于包括进位器、全加器和整合:

技术总结

本发明公开了一种CSA进位共享加法器及其实现方法,包括进位器、全加器和整合。本发明与现有技术相比的优点在于:本方案由超前进位加法器优化而来,第一位晶体管数量为20,此后每一位为22,总延迟为2T,输入端下方为一进位生成门,设计思路来源为超前进位加法器的进位生成机制,并由公式加入特殊情况阻断设计而得,全加器为自主设计的全新多位并行异或器反A1之类即为反码,由触发器或寄存器直接提供,续位方式为直接向后连接单元,比原有的技术方案减少了一半的晶体数量,增加了运算速度。

技术研发人员:方泽鑫

受保护的技术使用者:方泽鑫

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!