一种面向异构计算环境的FPGA虚拟化实现方法与流程

本发明涉及嵌入式计算,具体涉及一种面向异构计算环境的fpga虚拟化实现方法。

背景技术:

1、目前,机载信息处理系统面临的数据量成指数爆发,所需的计算能力也持续增长,当前同构多核的通用处理系统已无法完成大量信息编解码、卷积、快速傅里叶变换以及人工智能识别等任务。而具有硬件灵活、高吞吐、低功耗等特点的fpga器件,被越来越广泛应用于众多计算密集型任务中,作为协处理器实现大规模的并行加速处理,并与cpu组成异构计算系统,进一步丰富和补充了机载分布式体系结构。

2、fpga的部分可重构技术将fpga内部划分为多个区域,在运行时单独对这些区域进行配置,实现逻辑在线更新,且不影响其余区域的功能,这使得fpga能够在时间和空间两个维度进行多任务的动态切换。然而目前的部分可重构技术仅针对单一fpga器件,面对大型计算任务时,单个器件无法满足吞吐率和实时性需求,机载信息处理系统通常将任务拆分为多个子任务分发到不同的计算节点。因此,为了扩展算力,需要级联多个fpga器件,形成fpga资源池,并通过虚拟化技术对逻辑资源进行抽象,实现统一的资源管理和调度。而在开发方面,传统基于硬件描述的fpga开发模式需要应用开发者掌握领域特定的底层硬件知识,难以适应异构计算系统的软件指令编程,给应用开发带来很大挑战。面对装备快速迭代升级的实际应用需求,必须为应用开发人员提供一套统一的软硬件开发框架,使应用开发与硬件解耦,利用虚拟内存的资源管理机制实现跨多用户、多应用的fpga资源高效共享。

技术实现思路

1、有鉴于此,本申请实施例提供一种面向异构计算环境的fpga虚拟化实现方法,本发明以fpga部分重配置技术为核心,能够灵活地实现用户逻辑的时空分复用,支持多应用并发运行和动态切换,整体提升了fpga异构计算平台的开发效率、资源利用率和部署灵活性。

2、本申请实施例提供以下技术方案:一种面向异构计算环境的fpga虚拟化实现方法,包括:

3、fpga虚拟化硬件架构设计:将fpga逻辑资源分为静态区域和动态区域,所述静态区域为不可配置区域,所述动态区域为多个可动态重构的vfpga区域;

4、主机cpu端软件设计:通过用户应用程序api进行应用部署、fpga资源管理,以及与vfpga区域通信;通过运行时管理器在空间和时间上实现应用的调度;通过驱动程序实例化该多个可动态重构的vfpga区域,分别为vfpga区域设置所需数据结构,并为应用程序创建虚拟内存映射,以通过pcie总线与fpga进行通信。

5、根据本申请一种实施例,单个vfpga区域包含用户逻辑和动态封装器两部分。

6、根据本申请一种实施例,所述用户逻辑是经综合和系统验证的比特流,用户可使用包括hls、verilog、vhdl、opencl的语言开发应用;所述动态封装器为用户逻辑提供标准接口,使应用可跨vfpga运行。

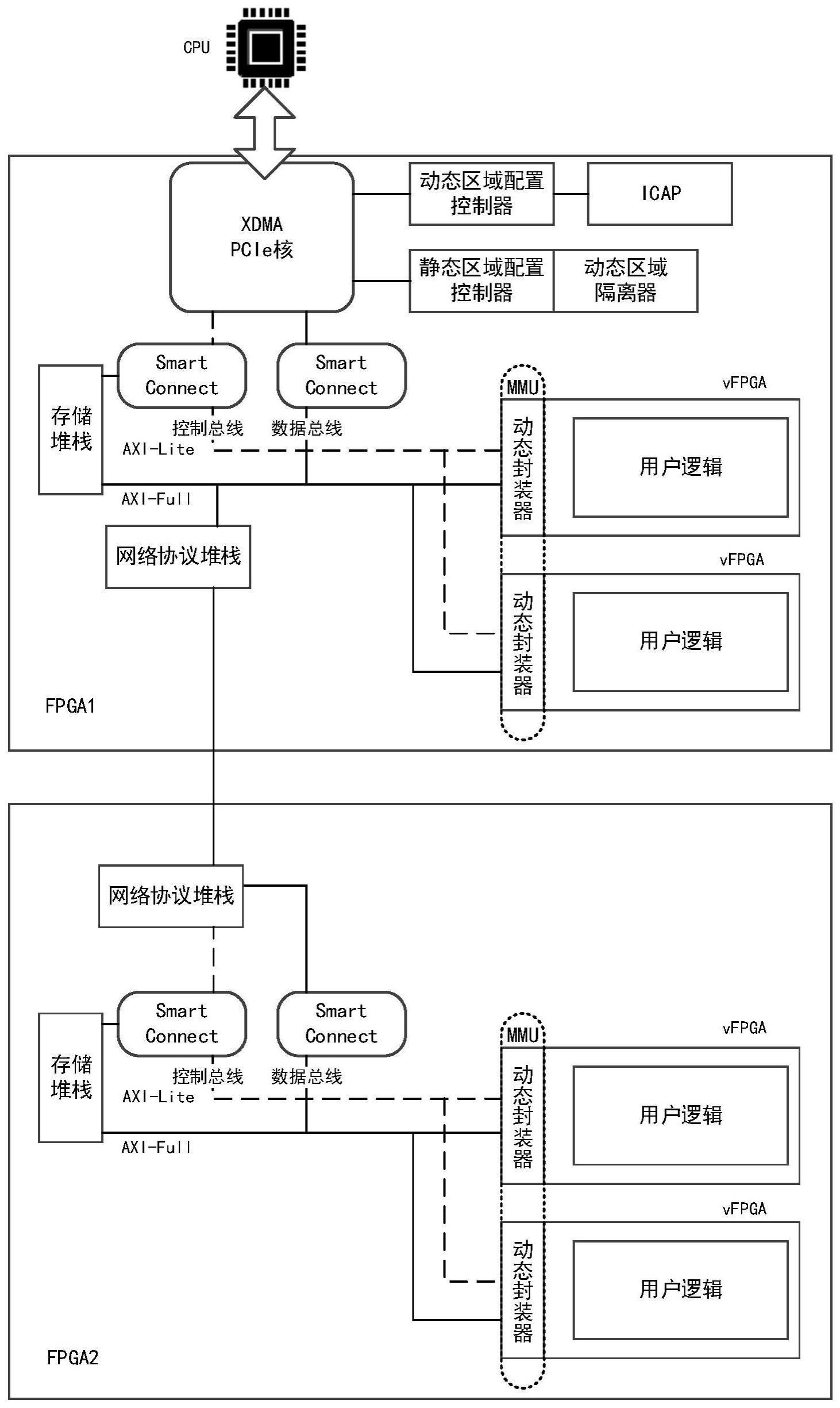

7、根据本申请一种实施例,所述fpga虚拟化硬件架构包括以下功能模块:

8、xdmapcie核,用于实现fpga与主机cpu之间的dma数据传输;

9、动态区域配置控制器和动态区域隔离器:动态区域配置控制器用于使用pcie总线和内部配置访问端口icap直接将配置数据写入vfpga区域中,实现部分重配置功能;动态区域隔离器用于确保部分重配置阶段,vfpga区域与静态区域逻辑信号解耦;

10、存储堆栈,用于支持xdma pcie核实现cpu与fpga之间的数据搬运,以及跨vfpga的本地ddr资源共享;

11、网络协议堆栈,用于利用以rocev2网络协议为基础的rdma通信方法,互连fpga计算节点,实现跨fpga的数据传输,形成fpga资源池;

12、动态封装器,用于为用户逻辑提供统一的对外接口,以及通过内置tlb的mmu单元,实现虚实地址转换。

13、根据本申请一种实施例,所述vfpga区域的所有数据通信均通过地址转换变为物理地址,本地存储请求直接发送至fpga,非本地请求交由所述网络协议堆栈模块处理。

14、根据本申请一种实施例,在主机cpu端软件设计过程中,采用模块的方式实现驱动程序,具体包括初始化设备模块、数据读写与控制模块、中断处理模块、设备打开、释放和卸载模块。

15、本发明提出一种面向异构计算环境的fpga虚拟化框架,硬件层面以fpga部分可重构技术为基础,通过部署在fpga上的网络协议堆栈,互连多个fpga器件,形成fpga资源池,实现多fpga的多个可重构区域间的高速互连和算力融合;软件层面利用虚拟化框架,对所有fpga资源进行抽象和分配调度管理,为应用程序提供统一的资源访问接口,实现应用程序的fpga部署与底层硬件的解耦。

16、本发明抽象了具体的fpga体系结构和硬件资源,使应用开发与硬件逻辑解耦;以fpga部分重配置技术为核心,为用户应用程序提供了统一的执行环境,能够灵活地实现用户逻辑的资源时空分复用,支持多应用并发运行和动态切换,整体提升了fpga异构计算平台的开发效率、资源利用率和部署灵活性。

技术特征:

1.一种面向异构计算环境的fpga虚拟化实现方法,其特征在于,包括:

2.根据权利要求1所述的面向异构计算环境的fpga虚拟化实现方法,其特征在于,单个vfpga区域包含用户逻辑和动态封装器两部分。

3.根据权利要求2所述的面向异构计算环境的fpga虚拟化实现方法,其特征在于,所述用户逻辑是经综合和系统验证的比特流,用户可使用包括hls、verilog、vhdl、opencl的语言开发应用;所述动态封装器为用户逻辑提供标准接口,使应用可跨vfpga运行。

4.根据权利要求3所述的面向异构计算环境的fpga虚拟化实现方法,其特征在于,所述fpga虚拟化硬件架构包括以下功能模块:

5.根据权利要求4所述的面向异构计算环境的fpga虚拟化实现方法,其特征在于,所述vfpga区域的所有数据通信均通过地址转换变为物理地址,本地存储请求直接发送至fpga,非本地请求交由所述网络协议堆栈模块处理。

6.根据权利要求1所述的面向异构计算环境的fpga虚拟化实现方法,其特征在于,在主机cpu端软件设计过程中,采用模块的方式实现驱动程序,具体包括初始化设备模块、数据读写与控制模块、中断处理模块、设备打开、释放和卸载模块。

技术总结

本发明提供了一种面向异构计算环境的FPGA虚拟化实现方法,包括:FPGA虚拟化硬件架构设计:将FPGA逻辑资源分为静态区域和动态区域,所述静态区域为不可配置区域,所述动态区域为多个可动态重构的vFPGA区域;主机CPU端软件设计:通过用户应用程序API进行应用部署、FPGA资源管理,以及与vFPGA区域通信;通过运行时管理器在空间和时间上实现应用的调度;通过驱动程序实例化该多个可动态重构的vFPGA区域,分别为vFPGA区域设置所需数据结构,并为应用程序创建虚拟内存映射,以通过PCIe总线与FPGA进行通信。本发明整体提升了FPGA异构计算平台的开发效率、资源利用率和部署灵活性。

技术研发人员:李晨卉,刘作龙,程岳,韩伟,余冠锋,潘妍

受保护的技术使用者:中国航空工业集团公司西安航空计算技术研究所

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!