一种基于多通道二级缓存的模块验证方法

本发明属于芯片验证,具体涉及一种基于多通道二级缓存的模块验证方法。

背景技术:

1、在芯片领域,一款芯片的设计有诸多环节,其中最耗时的无非是设计和验证两个过程。芯片验证的效率将决定该芯片是否能够按期交付,在全球缺芯的大背景下,芯片的按时交付对于各大芯片厂商的无疑是十分重要的。

2、目前业界对于如何验证多通道二级缓存模块缺乏一个高效的验证方式,含有多通道二级缓存模块的芯片的开发流程被大大延长,一直是芯片企业面临的难题。

3、相比于普通的少通道二级缓存,每多一条通道意味着发送的激励的情况将有指数级的增加,这会为我们的验证环境带来很大的考验。在多通道的基础上如果二级缓存自身还带有仲裁机制,那么上述场景将会变得更加复杂。传统的验证方案将二级缓存的数据对比以及二级缓存的仲裁机制的检查放在同一套环境里,一条通道的增加,不光要考虑到数据接收还能否顺利完成,还要考虑到仲裁机制是否进行更新从而处理这新增的一条数据量,每增加一条通道都要同时完成这两件事,阻碍了进度。这样做不仅大大提升了验证环境的复杂度,还消耗了大量的人力物力,并且由于测试场景过于复杂,无法保证模块验证的完备性。

技术实现思路

1、为了解决相关技术中存在的上述问题,本发明提供了一种基于多通道二级缓存的模块验证方法。本发明要解决的技术问题通过以下技术方案实现:

2、本发明提供一种基于多通道二级缓存的模块验证方法,应用于验证平台,包括:

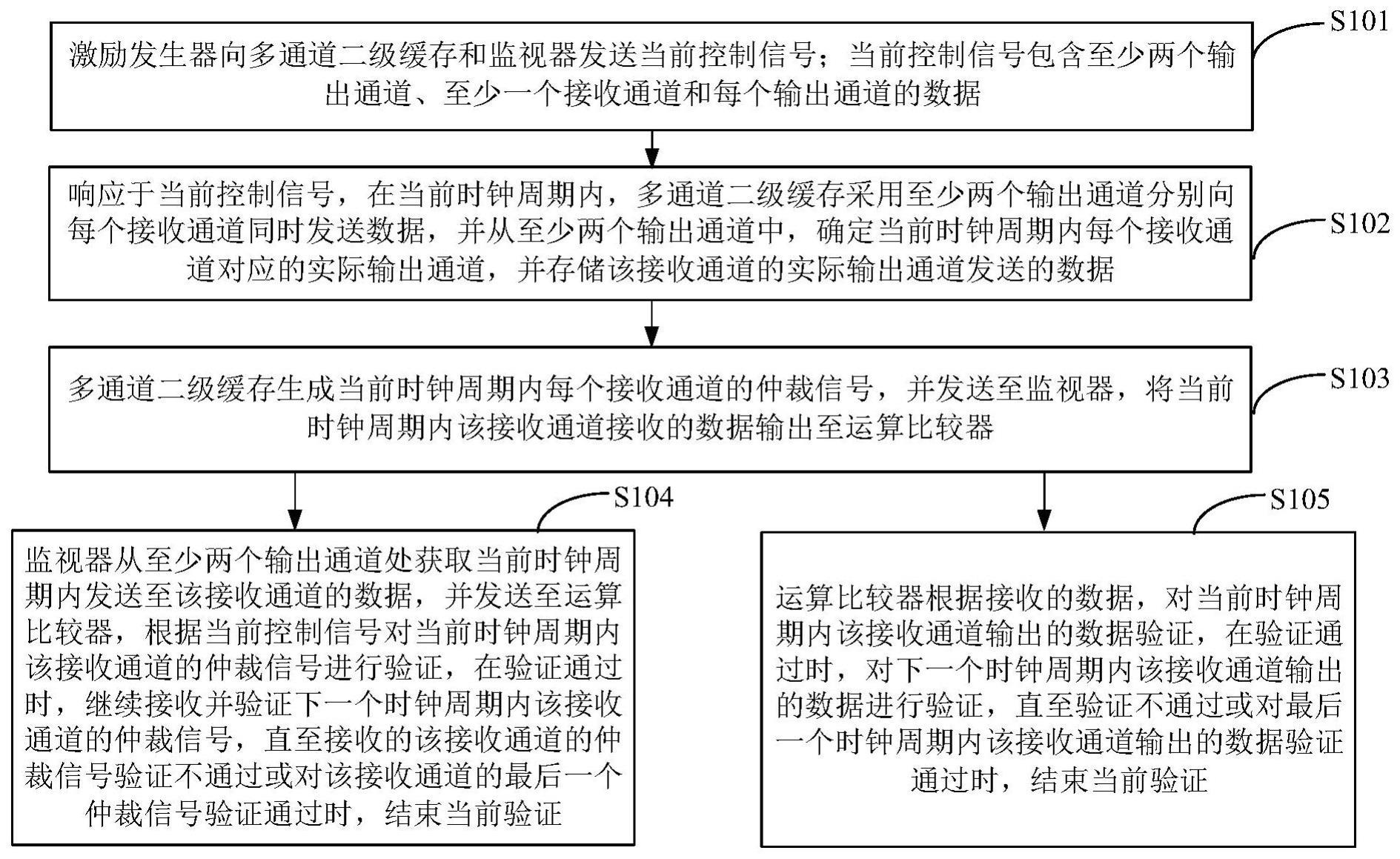

3、激励发生器向多通道二级缓存和监视器发送当前控制信号;所述当前控制信号包含至少两个输出通道、至少一个接收通道和每个输出通道的数据;

4、响应于所述当前控制信号,在当前时钟周期内,所述多通道二级缓存采用所述至少两个输出通道分别向每个接收通道同时发送所述数据,并从所述至少两个输出通道中,确定当前时钟周期内每个接收通道对应的实际输出通道,并存储该接收通道的实际输出通道发送的数据;

5、所述多通道二级缓存生成当前时钟周期内每个接收通道的仲裁信号,并发送至监视器,将当前时钟周期内该接收通道接收的数据输出至运算比较器;

6、所述监视器从所述至少两个输出通道处获取当前时钟周期内发送至该接收通道的数据,并发送至运算比较器,根据所述当前控制信号对当前时钟周期内该接收通道的仲裁信号进行验证,在验证通过时,继续接收并验证下一个时钟周期内该接收通道的仲裁信号,直至接收的该接收通道的仲裁信号验证不通过或对该接收通道的最后一个仲裁信号验证通过时,结束当前验证;

7、所述运算比较器根据接收的数据,对当前时钟周期内该接收通道输出的数据验证,在验证通过时,对下一个时钟周期内该接收通道输出的数据进行验证,直至验证不通过或对最后一个时钟周期内该接收通道输出的数据验证通过时,结束当前验证。

8、本发明具有如下有益技术效果:

9、通过本发明提供的基于多通道二级缓存的模块验证方法,可以将测试分成针对仲裁机制和针对数据完备性检查两部分,每一部分有各自的验证环境,两部分验证不再相互依赖、相互影响,从而提高了验证效率低,降低了验证时所需的人力成本、时间成本。

10、以下将结合附图及实施例对本发明做进一步详细说明。

技术特征:

1.一种基于多通道二级缓存的模块验证方法,应用于验证平台,其特征在于,包括:

2.根据权利要求1所述的基于多通道二级缓存的模块验证方法,其特征在于,所述多通道二级缓存生成当前时钟周期内每个接收通道的仲裁信号,包括:

3.根据权利要求2所述的基于多通道二级缓存的模块验证方法,其特征在于,所述实际输出通道是所述多通道二级缓存基于预设仲裁信息确定的;

4.根据权利要求3所述的基于多通道二级缓存的模块验证方法,其特征在于,所述采用所述下一个时钟周期内的预期通道,对下一个时钟周期内该接收通道的仲裁信号进行验证,包括:

5.根据权利要求2所述的基于多通道二级缓存的模块验证方法,其特征在于,所述实际输出通道是所述多通道二级缓存基于预设仲裁信息确定的;所述监视器中包含与所述多通道二级缓存的多个输出通道一一对应的多个第一队列;所述当前控制信号包含所述至少两个输出通道的地址、所述至少一个接收通道的地址;

6.根据权利要求1所述的基于多通道二级缓存的模块验证方法,其特征在于,所述运算比较器包括:运算器和对比器;

7.根据权利要求6所述的基于多通道二级缓存的模块验证方法,其特征在于,所述对比器采用所述运算数据对当前时钟周期内该接收通道输出的数据进行验证,包括:

8.根据权利要求1所述的基于多通道二级缓存的模块验证方法,其特征在于,所述方法还包括:

9.根据权利要求1所述的基于多通道二级缓存的模块验证方法,其特征在于,所述监视器中包含与所述多通道二级缓存的多个接收通道一一对应的多个第二队列;所述监视器从所述至少两个输出通道处获取当前时钟周期内发送至该接收通道的数据之后,将所述至少两个输出通道中每个输出通道发送的数据存储至对应的第二队列中。

技术总结

本发明公开了一种基于多通道二级缓存的模块验证方法,包括:激励发生器向多通道二级缓存和监视器发送当前控制信号;多通道二级缓存根据当前控制信号,在当前时钟周期内采用至少两个输出通道分别向每个接收通道同时发送数据,从至少两个输出通道中确定当前时钟周期内每个接收通道对应的实际输出通道,存储实际输出通道发送的数据;生成当前时钟周期内每个接收通道的仲裁信号后发至监视器,将当前时钟周期内该接收通道接收的数据输出至比较器;监视器从至少两个输出通道处获取当前时钟周期内发送至该接收通道的数据,并发送至比较器,对当前时钟周期内该接收通道的仲裁信号验证;比较器根据接收的数据对当前时钟周期内该接收通道输出的数据验证。

技术研发人员:赵晓春,张金风,刘斌

受保护的技术使用者:西安电子科技大学

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!