基于SRAM的ECC校验方法及装置与流程

本发明涉及电子通信,特别涉及一种基于sram的ecc校验方法及装置。

背景技术:

1、sram(static random-access memory,静态随机存取存储器)支持byte(8bits)、half-word(16bits)、word(32bits)三种读写操作,可在系统时钟频率下进行读写操作。但是当sram支持ecc纠错功能、且ecc使能后,只能是32bits一起写入,不能8bits/16bits单独的写入,否则ecc校验会出错。

2、此时,当写入的数据为8/16位时,由于bus总线剩余的数据位会保持原来的值,ecc校验的数据是8/16位待写入的数据加上bus总线上原来的24/16位数据,而不是8/16位待写入的数据加上sram中对应的24/16位数据。这样得到的ecc校验码是错误的,并且在数据写入sram后会将原来正确的ecc校验码替换掉,导致下次读取数据的时候产生ecc校验错误。

3、因此,当sram进行ecc校验时,如何支持8bits/16bits单独的写入而ecc校验码不出错,是我们亟待解决的问题。

技术实现思路

1、本发明的目的之一在于提供一种基于sram的ecc校验方法,以解决现有技术中sram进行ecc校验时无法应对多种数据处理长度的技术问题。

2、本发明的目的之一在于同一种基于sram的ecc校验装置。

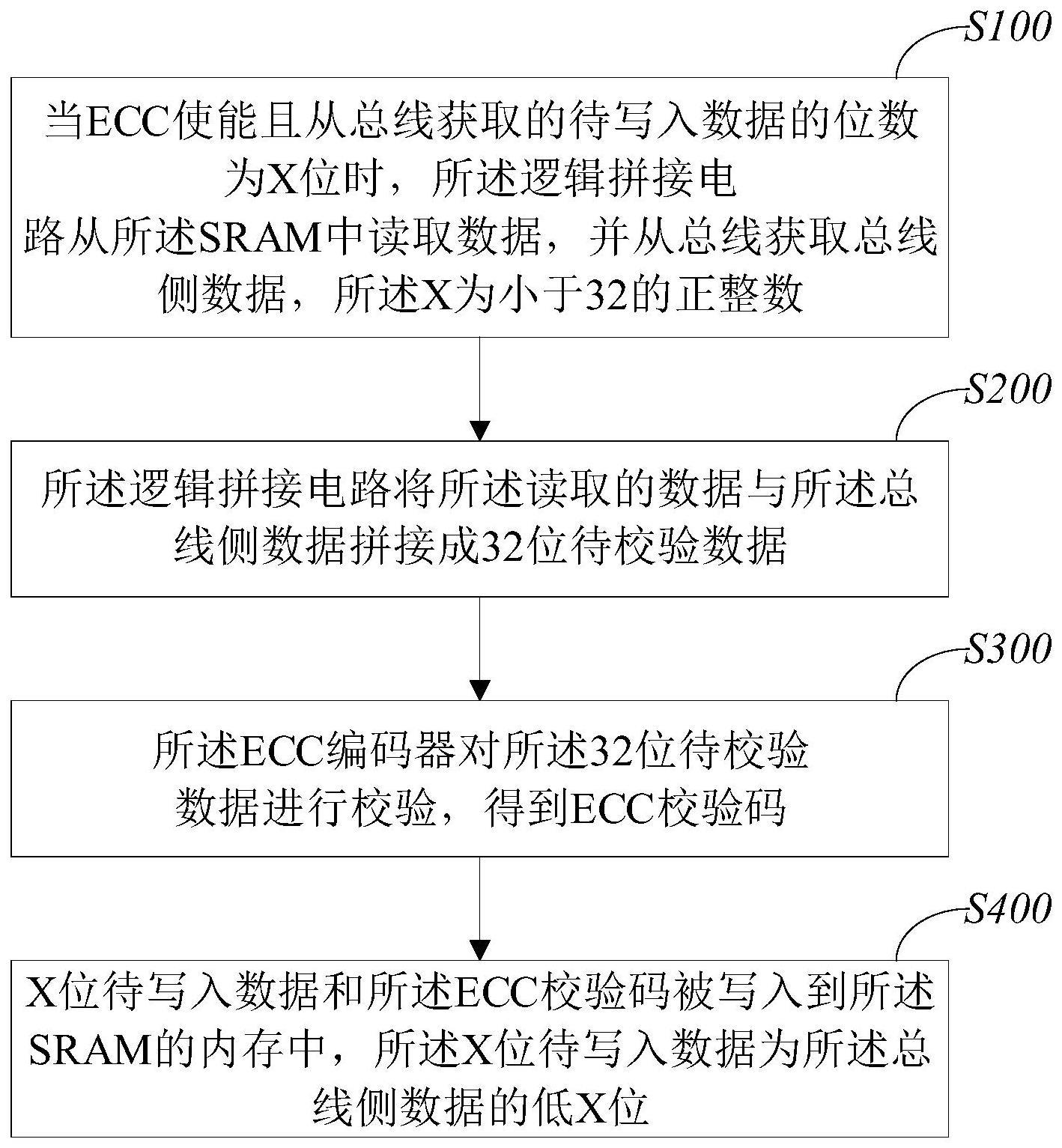

3、为实现上述发明目的之一,本发明一实施方式提供一种基于sram的ecc校验方法,所述sram外接逻辑拼接电路和ecc编码器,所述方法包括:当ecc使能且从总线获取的待写入数据的位数为x位时,所述逻辑拼接电路从所述sram中读取数据,并从总线获取总线侧数据,所述x为小于32的正整数;所述逻辑拼接电路将所述读取的数据与所述总线侧数据拼接成32位待校验数据;所述ecc编码器对所述32位待校验数据进行校验,得到ecc校验码;x位待写入数据和所述ecc校验码被写入到所述sram的内存中,所述x位待写入数据为所述总线侧数据的低x位。

4、作为本发明一实施方式的进一步改进,所述“逻辑拼接电路从所述sram中读取数据,并从总线获取总线侧数据”具体包括:在同一个时钟周期内,所述逻辑拼接电路从所述sram中读取数据,同时从总线获取总线侧数据。

5、作为本发明一实施方式的进一步改进,所述逻辑拼接电路到所述sram的输出信号包括读写使能cen信号、读写标记we信号和地址a信号,所述“逻辑拼接电路从所述sram中读取数”具体包括:所述逻辑拼接电路拉低所述cen信号的电平,同时,将所述we信号置为0,其中,所述cen信号为低电平有效,所述we信号为0表示对sram进行读操作;所述sram根据所述cen信号、we信号和地址a信号,到所述地址a处读取数据,并返回给所述逻辑拼接电路。

6、作为本发明一实施方式的进一步改进,所述“逻辑拼接电路将所述读取的数据与所述总线侧数据拼接成32位待校验数据”具体包括:所述读取的数据和所述总线侧数据都为32位;所述逻辑拼接电路根据所述待写入数据位数x,将所述总线侧数据的低x位与所述读取的数据的高32-x位进行拼接,得到32位待校验数据。

7、作为本发明一实施方式的进一步改进,所述x为8或者16。

8、为实现上述发明目的之一,本发明一实施方式提供一种基于sram的ecc校验装置,所述装置包括相互连接的逻辑拼接电路、ecc编码器和sram,其中:所述逻辑拼接电路的一侧与总线连接,用于从总线获取待写入数据的位数和总线侧数据;当ecc使能且从总线获取的待写入数据的位数为x位时,从所述sram中读取数据,将所述读取的数据与所述总线侧数据拼接成32位待校验数据,并将所述32位待校验数据发送给所述sram和所述ecc编码器,所述x为小于32的正整数;所述ecc编码器用于对所述32位待校验数据进行ecc校验,得到ecc校验码,并将所述ecc校验码发送给,所述sram;所述sram用于响应所述逻辑拼接电路和所述ecc编码器的读写请求,并将x位待写入数据和所述ecc校验码写入内存中,所述x位待写入数据为所述总线侧数据的低x位。

9、作为本发明一实施方式的进一步改进,所述逻辑拼接电路还用于:在同一个时钟周期内,从所述sram中读取数据,同时从总线获取总线侧数据。

10、作为本发明一实施方式的进一步改进,所述逻辑拼接电路到所述sram的输出信号包括读写使能cen信号、读写标记we信号和地址a信号;所述逻辑拼接电路还用于,当需要从所述sram中读取数据时,拉低所述cen信号的电平,同时,将所述we信号置为0,其中,所述cen信号为低电平有效,所述we信号为0表示对sram进行读操作;所述sram还用于根据所述cen信号、we信号和地址a信号,到所述地址a处读取数据,并返回给所述逻辑拼接电路。

11、作为本发明一实施方式的进一步改进,所述读取的数据和所述总线侧数据都为32位,所述逻辑拼接电路还用于:根据所述待写入数据位数x,将所述总线侧数据的低x位与所述读取的数据的高32-x位进行拼接,得到32位待校验数据。

12、作为本发明一实施方式的进一步改进,所述sram的内存包括数据存储区和ecc存储区,所述x位待写入数据被存入所述数据存储区,所述ecc校验码被存入所述ecc存储区。

13、与现有技术相比,本发明的基于sram的ecc校验方法,不仅能够保证8位或16位数据单独写入时ecc校验码的准确性,同时还可以避免8位或16位数据单独写入时出现延时,大大提高写操作的效率。

技术特征:

1.一种基于sram的ecc校验方法,其特征在于,所述sram外接逻辑拼接电路和ecc编码器,所述方法包括:

2.根据权利要求1所述的基于sram的ecc校验方法,其特征在于,所述“逻辑拼接电路从所述sram中读取数据,并从总线获取总线侧数据”具体包括:

3.根据权利要求1所述的基于sram的ecc校验方法,其特征在于,所述逻辑拼接电路到所述sram的输出信号包括读写使能cen信号、读写标记we信号和地址a信号,所述“逻辑拼接电路从所述sram中读取数”具体包括:

4.根据权利要求1所述的基于sram的ecc校验方法,其特征在于,所述“逻辑拼接电路将所述读取的数据与所述总线侧数据拼接成32位待校验数据”具体包括:

5.根据权利要求1所述的基于sram的ecc校验方法,其特征在于:

6.一种基于sram的ecc校验装置,其特征在于,所述装置包括相互连接的逻辑拼接电路、ecc编码器和sram,其中:

7.根据权利要求6所述的基于sram的ecc校验装置,其特征在于,所述逻辑拼接电路还用于:

8.根据权利要求6所述的基于sram的ecc校验装置,其特征在于:

9.根据权利要求6所述的基于sram的ecc校验装置,其特征在于,所述读取的数据和所述总线侧数据都为32位,所述逻辑拼接电路还用于:

10.根据权利要求6所述的基于sram的ecc校验装置,其特征在于:

技术总结

本发明揭示了一种基于SRAM的ECC校验方法和装置,所述装置包括相互连接的SRAM、逻辑拼接电路和ECC编码器,所述方法包括:当ECC使能且从总线获取的待写入数据的位数为X位时,所述逻辑拼接电路从所述SRAM中读取数据,并从总线获取总线侧数据;所述逻辑拼接电路将所述读取的数据与所述总线侧数据拼接成32位待校验数据;所述ECC编码器对所述32位待校验数据进行校验,得到ECC校验码;X位待写入数据和所述ECC校验码被写入到所述SRAM的内存中。与现有技术相比,本发明提供的基于SRAM的ECC校验方法,不仅能够保证8位或16位数据单独写入时ECC校验码的准确性,同时还可以避免8位或16位数据单独写入时出现延时,大大提高写操作的效率。

技术研发人员:陈家敏,石国城,杨维,王荣华,王成,张季润,岳海群,董厚希

受保护的技术使用者:芯弦半导体(苏州)有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!