内嵌逻辑分析系统、逻辑器件和器件分析设备的制作方法

本申请涉及集成电路,具体涉及一种内嵌逻辑分析系统、一种逻辑器件以及一种器件分析设备。

背景技术:

1、具有边界扫描功能的逻辑器件例如fpga(field programmable gate array,现场可编程逻辑门阵列)器件的内嵌逻辑分析仪是fpga器件开发和调试的重要工具,它以预先设定的时钟频率实时采样fpga器件的内部信号或者io(input output,输入输出)状态,并存储于fpga器件内部的ram(random access memory,随机存取存储器)中,然后通过逻辑分析电路(la,logic analyzer)进行数据分析和加工。当预设的触发条件满足后,逻辑分析电路通过jtag(joint test action group,联合测试工作组)接口将存储在内部ram中的数据缓存传输至pc(personal computer,个人计算机)上。当pc获得jtag接口回传数据后,通过本地计算将对应的逻辑分析结果展现出来。

2、目前,fpga器件的内嵌逻辑分析仪采集和上报数据是通过jtag来完成的。jtag包含测试访问端口、边界扫描单元(boundary scan cell)、测试访问端口控制器(testaccess port controller)、指令寄存器(ir,instruction register)和测试数据寄存器(tdr,test data register)等。其中,测试访问端口就是常见的jtag接口,一般它包含测试时钟输入(tck)引脚、测试模式选择输入(tms)引脚、测试数据输出(tdo)引脚和测试数据输入(tdi)引脚,另外还包含可选的测试复位输入(trst)引脚。

3、jtag接口一般用于研发调试和维护阶段,且大多存在于多io的器件上,但对于一款成熟的fpga产品来说,使用jtag接口是一种浪费。

技术实现思路

1、因此,为了节省io资源,本申请实施例提供一种内嵌逻辑分析系统、一种逻辑器件以及一种器件分析设备。

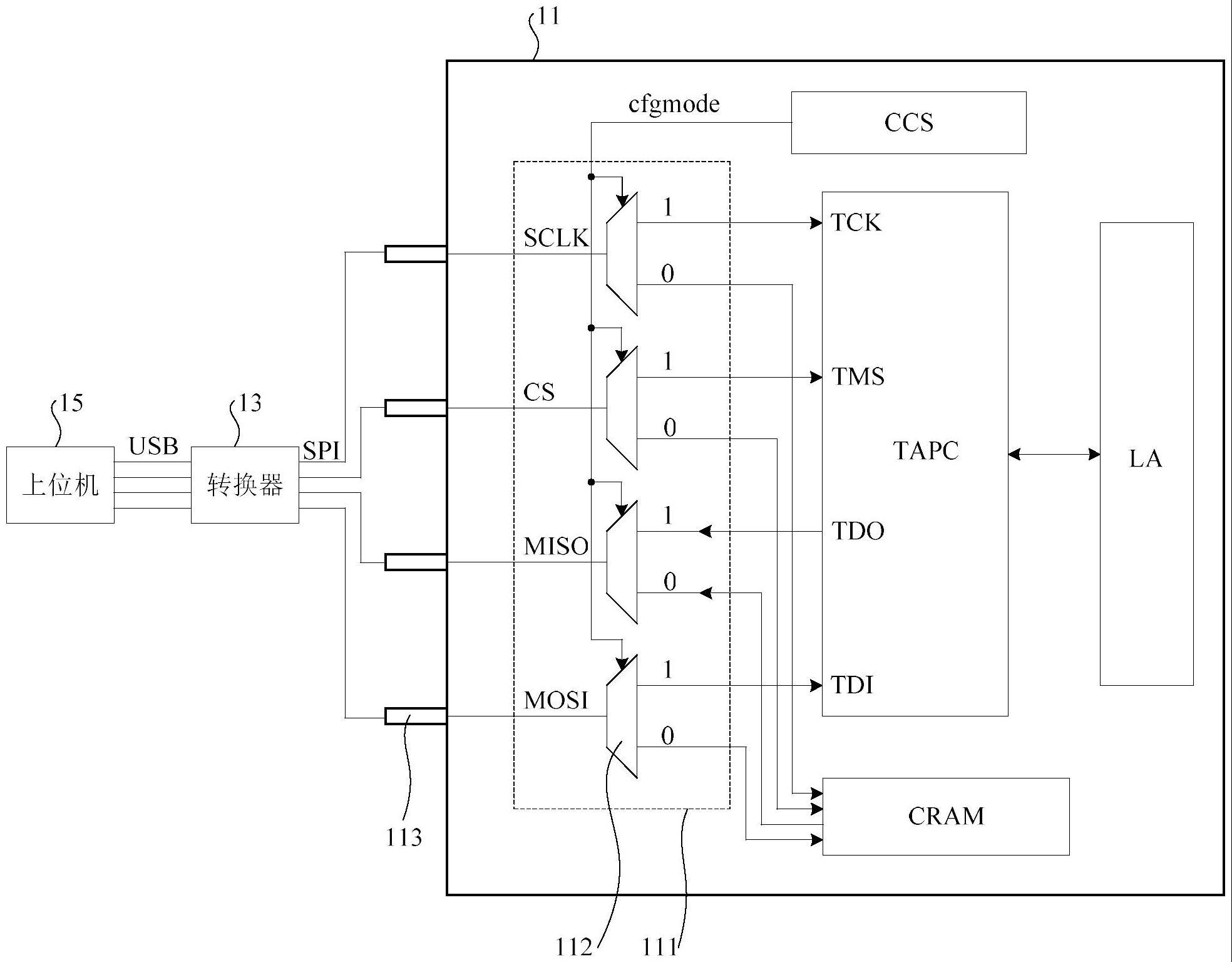

2、本申请实施例提供的一种内嵌逻辑分析系统,包括:spi接口输入输出电路、配置控制电路、测试访问端口控制电路和逻辑分析电路;所述spi接口输入输出电路包括串行移位时钟信号端、片选信号端、主输入从输出信号端、主输出从输入信号端、和多个选择器;所述配置控制电路连接所述多个选择器的控制端;所述测试访问端口控制电路通过所述多个选择器连接所述串行移位时钟信号端、所述片选信号端、所述主输入从输出信号端和所述主输出从输入信号端;所述逻辑分析电路连接所述测试访问端口控制电路。

3、进一步地,所述多个选择器包括四个二选一选择器,所述测试访问端口控制电路包括测试时钟输入端、测试模式选择输入端、测试数据输出端和测试数据输入端,所述测试时钟输入端、所述测试模式选择输入端、所述测试数据输出端和所述测试数据输入端通过所述四个二选一选择器分别连接所述串行移位时钟信号端、所述片选信号端、所述主输入从输出信号端和所述主输出从输入信号端。

4、进一步地,所述测试访问端口控制电路包括测试访问端口控制器、指令寄存器和测试数据寄存器,所述测试访问端口控制器连接所述测试时钟输入端和所述测试模式选择输入端,所述指令寄存器和所述测试数据寄存器连接所述测试访问端口控制器且连接所述测试数据输出端和所述测试数据输入端。

5、进一步地,所述测试数据寄存器包括旁路寄存器和标识寄存器,所述旁路寄存器连接所述测试数据输出端和所述测试数据输入端,所述标识寄存器连接所述测试数据输出端和所述测试数据输入端。

6、另一方面,本申请实施例提供的一种逻辑器件,包括:内嵌逻辑分析系统、配置存储器和引脚组;所述内嵌逻辑分析系统包括:spi接口输入输出电路、配置控制电路、测试访问端口控制电路和逻辑分析电路;其中,所述spi接口输入输出电路包括串行移位时钟信号端、片选信号端、主输入从输出信号端、主输出从输入信号端、和多个选择器,所述配置控制电路连接所述多个选择器的控制端,所述测试访问端口控制电路通过所述多个选择器连接所述串行移位时钟信号端、所述片选信号端、所述主输入从输出信号端和所述主输出从输入信号端,所述逻辑分析电路连接所述测试访问端口控制电路;所述配置存储器通过所述多个选择器连接所述串行移位时钟信号端、所述片选信号端、所述主输入从输出信号端和所述主输出从输入信号端,且所述配置存储器用于存储所述逻辑器件的逻辑单元的功能配置信息;所述引脚组连接所述串行移位时钟信号端、所述片选信号端、所述主输入从输出信号端和所述主输出从输入信号端。

7、进一步地,所述多个选择器包括四个二选一选择器,所述测试访问端口控制电路包括测试时钟输入端、测试模式选择输入端、测试数据输出端和测试数据输入端,所述测试时钟输入端、所述测试模式选择输入端、所述测试数据输出端和所述测试数据输入端通过所述四个二选一选择器分别连接所述串行移位时钟信号端、所述片选信号端、所述主输入从输出信号端和所述主输出从输入信号端。

8、进一步地,所述测试访问端口控制电路包括测试访问端口控制器、指令寄存器和测试数据寄存器,所述测试访问端口控制器连接所述测试时钟输入端和所述测试模式选择输入端,所述指令寄存器和所述测试数据寄存器连接所述测试访问端口控制器且连接所述测试数据输出端和所述测试数据输入端。

9、进一步地,所述测试数据寄存器包括旁路寄存器和标识寄存器,所述旁路寄存器连接所述测试数据输出端和所述测试数据输入端,所述标识寄存器连接所述测试数据输出端和所述测试数据输入端。

10、进一步地,所述逻辑器件为现场可编程门阵列器件。

11、再一方面,本申请实施例提供的一种器件分析设备,包括:上位机、转换器、和前述任一实施例所述的逻辑器件;所述上位机通过usb接口连接所述转换器,且所述转换器连接所述引脚组。

12、本申请实施例提供的上述内嵌逻辑分析系统、逻辑器件和器件分析设备,其采用从spi接口而不再使用jtag接口作为测试访问端口,jtag接口的4个io在封装中不会引出甚至硬件上不做设计,加载和功能调试都借助于从spi接口;从spi接口既可以加载逻辑器件例如fpga器件,也可以抓取和分析波形,这样做既可以节省io资源,又可以简化一部分硬件设计。

技术特征:

1.一种内嵌逻辑分析系统,其特征在于,包括:spi接口输入输出电路、配置控制电路、测试访问端口控制电路和逻辑分析电路;

2.如权利要求1所述的内嵌逻辑分析系统,其特征在于,所述多个选择器包括四个二选一选择器;所述测试访问端口控制电路包括测试时钟输入端、测试模式选择输入端、测试数据输出端和测试数据输入端;其中,所述测试时钟输入端、所述测试模式选择输入端、所述测试数据输出端和所述测试数据输入端通过所述四个二选一选择器分别连接所述串行移位时钟信号端、所述片选信号端、所述主输入从输出信号端和所述主输出从输入信号端。

3.如权利要求2所述的内嵌逻辑分析系统,其特征在于,所述测试访问端口控制电路包括测试访问端口控制器、指令寄存器和测试数据寄存器,所述测试访问端口控制器连接所述测试时钟输入端和所述测试模式选择输入端,所述指令寄存器和所述测试数据寄存器连接所述测试访问端口控制器且连接所述测试数据输出端和所述测试数据输入端。

4.如权利要求3所述的内嵌逻辑分析系统,其特征在于,所述测试数据寄存器包括旁路寄存器和标识寄存器,所述旁路寄存器连接所述测试数据输出端和所述测试数据输入端,所述标识寄存器连接所述测试数据输出端和所述测试数据输入端。

5.一种逻辑器件,其特征在于,包括:内嵌逻辑分析系统、配置存储器和引脚组;

6.如权利要求5所述的逻辑器件,其特征在于,所述多个选择器包括四个二选一选择器,所述测试访问端口控制电路包括测试时钟输入端、测试模式选择输入端、测试数据输出端和测试数据输入端,所述测试时钟输入端、所述测试模式选择输入端、所述测试数据输出端和所述测试数据输入端通过所述四个二选一选择器分别连接所述串行移位时钟信号端、所述片选信号端、所述主输入从输出信号端和所述主输出从输入信号端。

7.如权利要求6所述的逻辑器件,其特征在于,所述测试访问端口控制电路包括测试访问端口控制器、指令寄存器和测试数据寄存器,所述测试访问端口控制器连接所述测试时钟输入端和所述测试模式选择输入端,所述指令寄存器和所述测试数据寄存器连接所述测试访问端口控制器且连接所述测试数据输出端和所述测试数据输入端。

8.如权利要求7所述的逻辑器件,其特征在于,所述测试数据寄存器包括旁路寄存器和标识寄存器,所述旁路寄存器连接所述测试数据输出端和所述测试数据输入端,所述标识寄存器连接所述测试数据输出端和所述测试数据输入端。

9.如权利要求5至8任意一项所述的逻辑器件,其特征在于,所述逻辑器件为现场可编程门阵列器件。

10.一种器件分析设备,其特征在于,包括:上位机、转换器、和如权利要求5至9任意一项所述的逻辑器件;所述上位机通过usb接口连接所述转换器,且所述转换器连接所述引脚组。

技术总结

本申请实施例公开了一种内嵌逻辑分析系统及相应的逻辑器件和器件分析设备。所述内嵌逻辑分析系统包括:SPI接口输入输出电路、配置控制电路、测试访问端口控制电路和逻辑分析电路;SPI接口输入输出电路包括串行移位时钟信号端、片选信号端、主输入从输出信号端、主输出从输入信号端和多个选择器;配置控制电路连接多个选择器的控制端;测试访问端口控制电路通过多个选择器连接串行移位时钟信号端、片选信号端、主输入从输出信号端和主输出从输入信号端;逻辑分析电路连接测试访问端口控制电路。本申请实施例采用从SPI接口而不再使用JTAG接口作为测试访问端口,加载和功能调试都借助于从SPI接口,这样既可以节省IO资源,又可以简化一部分硬件设计。

技术研发人员:龙鲤跃,彭祥吉,包朝伟

受保护的技术使用者:深圳市紫光同创电子有限公司

技术研发日:20221118

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!