时间去偏差电路、系统及电子设备的制作方法

本技术实施例涉及计算机硬件设计,尤其涉及一种时间去偏差电路、系统及电子设备。

背景技术:

1、数据传输接口可以应用于数据发送电路和数据接收电路之间的数据传输,在利用数据传输接口传输多线路的数据时,各线路的数据在经过传输后会存在时间偏差,因此如何去除多线路的数据之间的时间偏差,并且降低数据的访问延迟,成为了本领域技术人员亟需解决的技术问题。

技术实现思路

1、本实用新型实施例解决的技术问题是如何去除多线路的数据之间的时间偏差,并且降低数据的访问延迟。

2、为解决上述问题,本实用新型实施例提供如下技术方案。

3、第一方面,本实用新型实施例提供一种时间去偏差电路,包括:

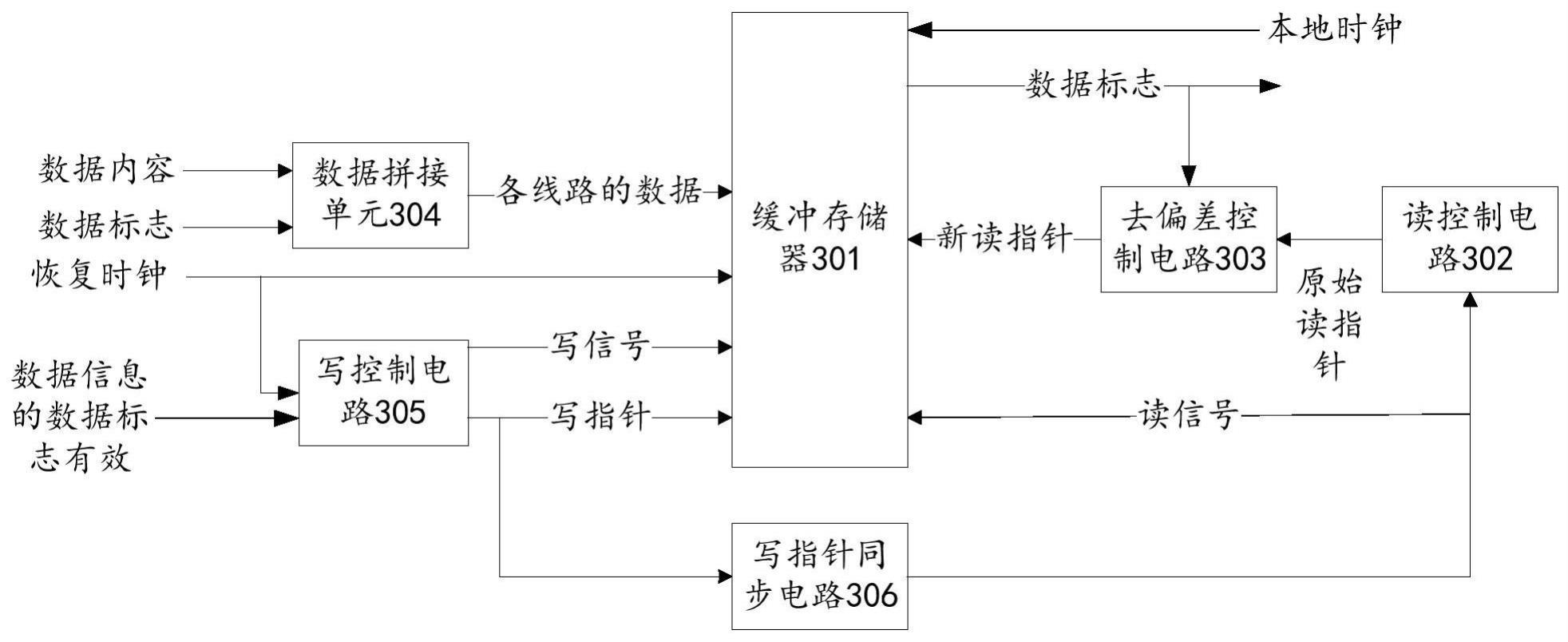

4、缓冲存储器,用于存储各线路的数据信息,一个线路的数据信息包括一个线路的数据内容和数据标志;

5、读控制电路,用于产生读信号和原始读指针,所述读信号用于控制所述缓冲存储器输出存储的数据信息;

6、去偏差控制电路,用于在所述缓冲存储器输出的数据信息中存在所有线路的数据标志时,对所述原始读指针和各线路偏差时间进行计算,得到各线路的新读指针;将所述新读指针传递给所述缓冲存储器,以控制所述缓冲存储器输出去除时间偏差后的各线路的数据信息。

7、第二方面,本实用新型实施例提供一种时间去偏差系统,包括:数据接收电路,所述数据接收电路包括如第一方面所述的时间去偏差电路。

8、第三方面,本实用新型实施例还提供了一种电子设备,包括如第二方面所述的时间去偏差系统。

9、数据发送电路通过数据传输接口传输多线路数据(数据内容)时,所出现的传输后的多线路数据之间存在时间偏差的问题,主要是由于数据发送电路中的缓冲存储器需要通过数据传输接口,向数据接收电路传输多线路数据所引起的;因此,本实用新型实施例提供应用于数据接收电路的时间去偏差电路,通过在时间去偏差电路中合并缓冲存储器和用于去除时间偏差的去偏差控制电路,以在较低的延迟周期内,去除线路之间的时间偏差。该时间去偏差电路包括缓冲存储器、读控制电路和去偏差控制电路。缓冲存储器,可存储数据发送电路传递的各线路的数据信息,一个线路的数据信息包括一个线路的数据内容和数据标志;读控制电路可产生读信号和原始读指针,读信号用于控制缓冲存储器输出存储的数据信息;去偏差控制电路可在所述缓冲存储器输出的数据信息中存在所有线路的数据标志时,对原始读指针和各线路的偏差时间进行计算,得到各线路的新读指针;将新读指针传递给所述缓冲存储器,以在新读指针的作用下,控制所述缓冲存储器输出去除时间偏差后的各线路的数据信息。本实用新型实施例可在新型的数据接收电路中,利用去偏差控制电路将缓冲存储器中存储的各线路的数据信息之间的时间偏差进行去除,并且降低数据发送电路和数据接收电路之间多线路数据信息的访问延迟。

10、可见,本实用新型实施例所提供的技术方案,在数据接收电路中,设置有包括缓冲存储器、读控制电路、去偏差控制电路的时间去偏差电路,通过将缓冲存储器设置于所述数据接收电路中,以实现缓冲存储器和去偏差控制电路的合并,避免在缓冲存储器和所述去偏差控制电路之间通过数据传输接口传输多线路数据信息;并且,进一步的基于所述读控制电路产生的原始读指针,和所述去偏差控制电路内部获得的各线路的偏差时间进行计算,对所述原始读指针对应的存储位置进行调整;以对缓冲存储器中存储的各线路的数据信息之间存在的时间偏差进行去除,由于数据信息中包含有数据内容,因此可以确保多线路数据去偏差的同时,降低多线路数据的访问延迟。

技术特征:

1.一种时间去偏差电路,其特征在于,包括:

2.如权利要求1所述的时间去偏差电路,其特征在于,所述去偏差控制电路包括:

3.如权利要求2所述的时间去偏差电路,其特征在于,所述状态机包括组合逻辑电路和状态寄存器;

4.如权利要求2所述的时间去偏差电路,其特征在于,所述计算器包括减法器,用于将所述原始读指针减去各线路的计时器的计时时间,得到各线路的新读指针。

5.如权利要求2所述的时间去偏差电路,其特征在于,还包括:

6.如权利要求1-5任一项所述的时间去偏差电路,其特征在于,还包括:

7.如权利要求6所述的时间去偏差电路,其特征在于,还包括:

8.一种时间去偏差系统,其特征在于,包括:

9.如权利要求8所述的时间去偏差系统,其特征在于,还包括:

10.如权利要求9所述的时间去偏差系统,其特征在于,还包括:

11.如权利要求10所述的时间去偏差系统,其特征在于,还包括:

12.一种电子设备,其特征在于,包括如权利要求8-11任一项所述的时间去偏差系统。

技术总结

本技术实施例提供一种时间去偏差电路、系统及电子设备,所述时间去偏差电路包括:缓冲存储器,用于存储各线路的数据信息,一个线路的数据信息包括一个线路的数据内容和数据标志;读控制电路,用于产生读信号和原始读指针,所述读信号用于控制所述缓冲存储器输出存储的数据信息;去偏差控制电路,用于在所述缓冲存储器输出的数据信息中存在所有线路的数据标志时,对所述原始读指针和各线路偏差时间进行计算,得到各线路的新读指针;将所述新读指针传递给所述缓冲存储器,以控制所述缓冲存储器输出去除时间偏差后的各线路的数据信息。本技术实施例提供的技术方案,可去除多线路数据之间的时间偏差,降低数据的访问延迟。

技术研发人员:李涛

受保护的技术使用者:成都海光集成电路设计有限公司

技术研发日:20221208

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!