基于FPGA构建的LPCFLASH数据一致性保护电路的制作方法

本技术涉及信息安全,尤其涉及一种基于fpga构建的lpc flash数据一致性保护电路。

背景技术:

1、通常在某些特定的嵌入式及计算机系统中,为了增加系统安全性,往往需要判断flash中的相关数据是否被篡改。以往技术手段都是将电路板中的flash拆下,通过烧写器查看数据是否被篡改,若被篡改,也需要通过烧写器更新flash中的数据。这种方式操作繁琐复杂,经常拆装容易损坏flash,安全性较低,且flash数据被篡改时,不能实时更新数据。

技术实现思路

1、为解决上述技术问题,本实用新型提供一种基于fpga构建的lpc flash数据一致性保护电路。本实用新型的技术方案如下:

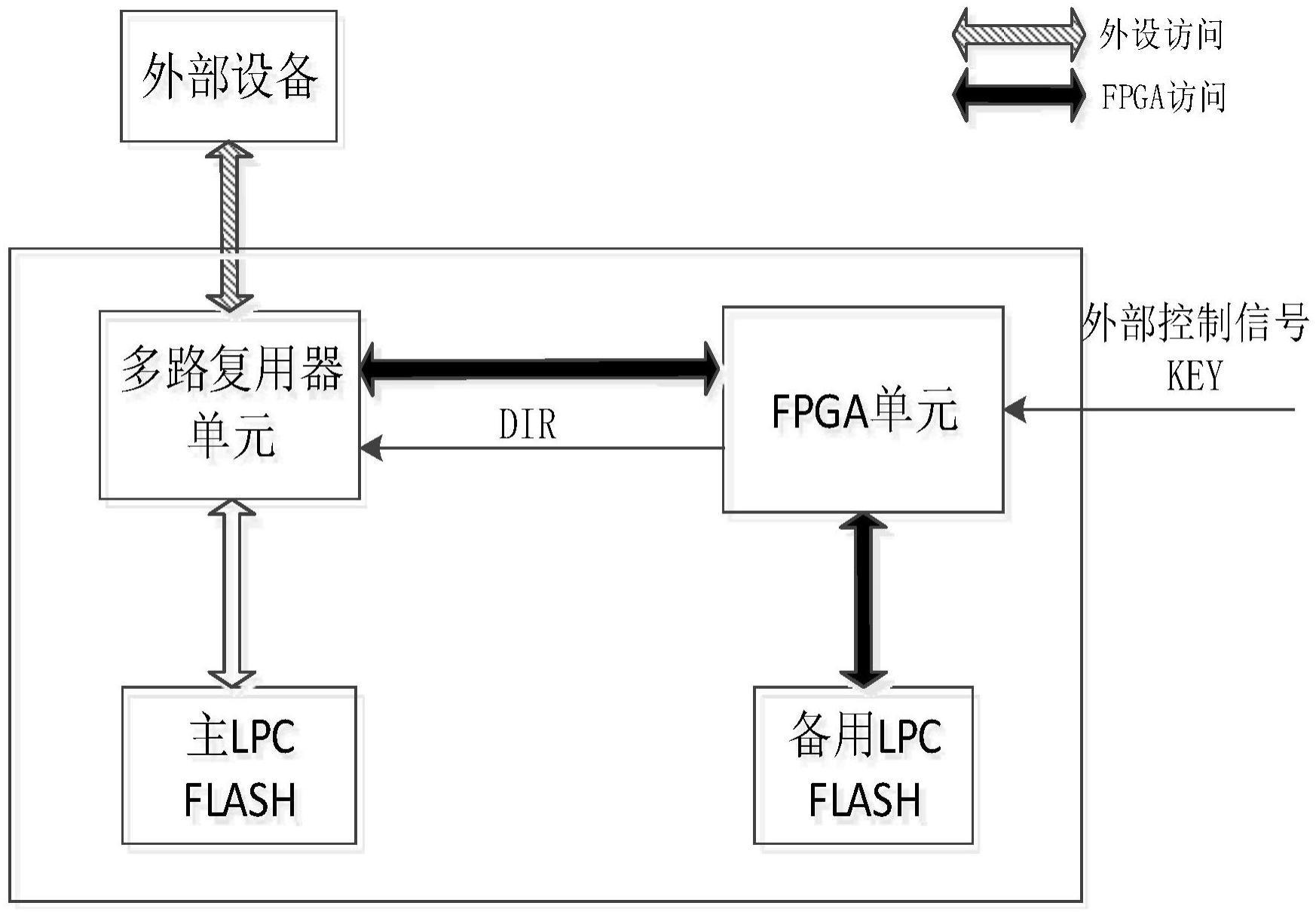

2、一种基于fpga构建的lpc flash数据一致性保护电路,其包括fpga单元、多路复用器单元和lpc flash存储单元,所述lpc flash存储单元包括主lpc flash和备用lpcflash;所述备用lpc flash与fpga单元连接,fpga单元还通过多路复用器单元与主lpcflash连接,主lpc flash还通过多路复用器单元与外部设备连接;

3、所述备用lpc flash中预先备份有主lpc flash中的数据,fpga单元通过外部控制信号控制多路复用器单元在线读取主lpc flash中的数据,并对主lpc flash与备用lpcflash中的数据进行一致性判断,并且如果fpga单元确定主lpc flash中的数据被篡改,则fpga单元在线将备用lpc flash中的数据回写至主lpc flash中,实现主lpc flash内数据的及时更新;所述多路复用器单元通过判断使能信号实现外部设备访问主lpc flash和fpga单元访问主lpc flash的通路转换。

4、可选地,所述fpga单元包括主芯片d1c,d1c采用xc6slx16-2csg225i,d1c的引脚9、引脚m10、引脚m9、引脚n9、引脚p9、引脚r9和引脚n8分别与备用lpc flash的相应输出端口连接,d1c的引脚p11、引脚r11、引脚m11、引脚n11和引脚n10分别与多路复用器单元的相应输入端口连接,d1c的引脚n6为多路复用器单元的控制信号dir的输入端口,d1c的引脚n7为外部控制信号key的输入端口。

5、可选地,所述多路复用器单元包括芯片d2和芯片d4,d2和d4均采用sn74cbtlv3257pwr;

6、d2的引脚16为电源端口,引脚15和引脚8均接地,引脚4、引脚7、引脚9和引脚12分别与主lpc flash的相应输出端口连接,引脚2、引脚5、引脚11和引脚14分别与fpga单元的相应输出端口连接,引脚3、引脚6、引脚10和引脚13分别与外部设备的相应输出端口连接,引脚1为控制信号dir的输入端口;

7、d4的引脚16为电源端口,引脚15和引脚8均接地,引脚4、引脚7和引脚9分别与主lpc flash的相应输出端口连接,引脚2、引脚5和引脚11分别与fpga单元的相应输出端口连接,引脚3、引脚6和引脚10分别与外部设备的相应输出端口连接,引脚1为控制信号dir的输入端口。

8、可选地,所述主lpc flash和备用lpc flash分别采用芯片d3和d34,d3和d34均采用sst49lf008a;

9、d3的引脚25和引脚32为电源端口,引脚13、引脚14、引脚15和引脚17分别与d2的引脚4、引脚7、引脚9和引脚12连接,引脚31与d4的引脚4连接,引脚2与d4的引脚9连接,引脚23与d4的引脚7连接,引脚7、引脚23和引脚24分别通过电阻r15、r17和r22与直流电源输入端连接,引脚29通过电阻r23接地,引脚16和引脚28均接地,引脚8通过电阻r14与直流电源输入端连接,引脚12、引脚11、引脚10和引脚9分别通过电阻r18、r19、r20和r21接地,引脚6、引脚5、引脚4、引脚3和引脚30均接地;

10、d34的引脚25和引脚32为电源端口,引脚13、引脚14、引脚15和引脚17分别与d1c的引脚9、引脚m10、引脚m9和引脚n9连接,引脚31与d1c的引脚n8连接,引脚2与d1c的引脚p9连接,引脚23与d1c的引脚r9连接,引脚7、引脚23和引脚24分别通过电阻r200、r201和r206与直流电源输入端连接,引脚29通过电阻r208接地,引脚16和引脚28均接地,引脚8通过电阻r199与直流电源输入端连接,引脚12、引脚11、引脚10和引脚9分别通过电阻r202、r203、r204和r205接地,引脚6、引脚5、引脚4、引脚3和引脚30均接地。

11、上述所有可选地技术方案均可任意组合,本实用新型不对一一组合后的结构进行详细说明。

12、借由上述方案,本实用新型的有益效果如下:

13、通过设置fpga单元、多路复用器单元、主lpc flash和备用lpc flash,并通过在备用lpc flash中预先备份主lpc flash中的数据后,如果fpga单元确定主lpc flash中的数据被篡改,则fpga单元在线将备用lpc flash中的数据回写至主lpc flash中,实现主lpcflash内数据的及时更新,在该电路结构下,当flash中的数据被篡改后,无需拆装flash芯片,不仅可降低器件多次拆装而损坏的风险,降低人工及芯片损坏成本,而且实现了flash中数据的在线实时更新,并可减少对烧写器的依赖,降低了工具使用及维护成本。

14、上述说明仅是本实用新型技术方案的概述,为了能够更清楚了解本实用新型的技术手段,并可依照说明书的内容予以实施,以下以本实用新型的较佳实施例并配合附图详细说明如后。

技术特征:

1.一种基于fpga构建的lpc flash数据一致性保护电路,其特征在于,包括fpga单元、多路复用器单元和lpc flash存储单元,所述lpc flash存储单元包括主lpc flash和备用lpc flash;所述备用lpc flash与fpga单元连接,fpga单元还通过多路复用器单元与主lpcflash连接,主lpc flash还通过多路复用器单元与外部设备连接;

2.根据权利要求1所述的基于fpga构建的lpc flash数据一致性保护电路,其特征在于,所述fpga单元包括主芯片d1c,d1c采用xc6slx16-2csg225i,d1c的引脚9、引脚m10、引脚m9、引脚n9、引脚p9、引脚r9和引脚n8分别与备用lpc flash的相应输出端口连接,d1c的引脚p11、引脚r11、引脚m11、引脚n11和引脚n10分别与多路复用器单元的相应输入端口连接,d1c的引脚n6为多路复用器单元的控制信号dir的输入端口,d1c的引脚n7为外部控制信号key的输入端口。

3.根据权利要求2所述的基于fpga构建的lpc flash数据一致性保护电路,其特征在于,所述多路复用器单元包括芯片d2和芯片d4,d2和d4均采用sn74cbtlv3257pwr;

4.根据权利要求3所述的基于fpga构建的lpc flash数据一致性保护电路,其特征在于,所述主lpc flash和备用lpc flash分别采用芯片d3和d34,d3和d34均采用sst49lf008a;

技术总结

本技术涉及一种基于FPGA构建的LPCFLASH数据一致性保护电路,属于信息安全技术领域。包括:备用LPCFLASH中预先备份有主LPCFLASH中的数据,FPGA单元通过外部控制信号控制多路复用器单元在线读取主LPC FLASH中的数据,并对主LPCFLASH与备用LPCFLASH中的数据进行一致性判断,如果主LPCFLASH中的数据被篡改,则在线将备用LPCFLASH中的数据回写至主LPCFLASH中。当FLASH中的数据被篡改后,本技术无需拆装FLASH芯片,不仅可降低器件多次拆装而损坏的风险,而且实现了FLASH中数据的在线实时更新。

技术研发人员:王卫霞

受保护的技术使用者:山西银河电子设备厂

技术研发日:20221230

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!