基于模拟信号的多比特数据计算电路、芯片及计算装置的制作方法

本公开涉及集成电路设计,尤其是一种基于模拟信号的多比特数据计算电路、芯片及计算装置。

背景技术:

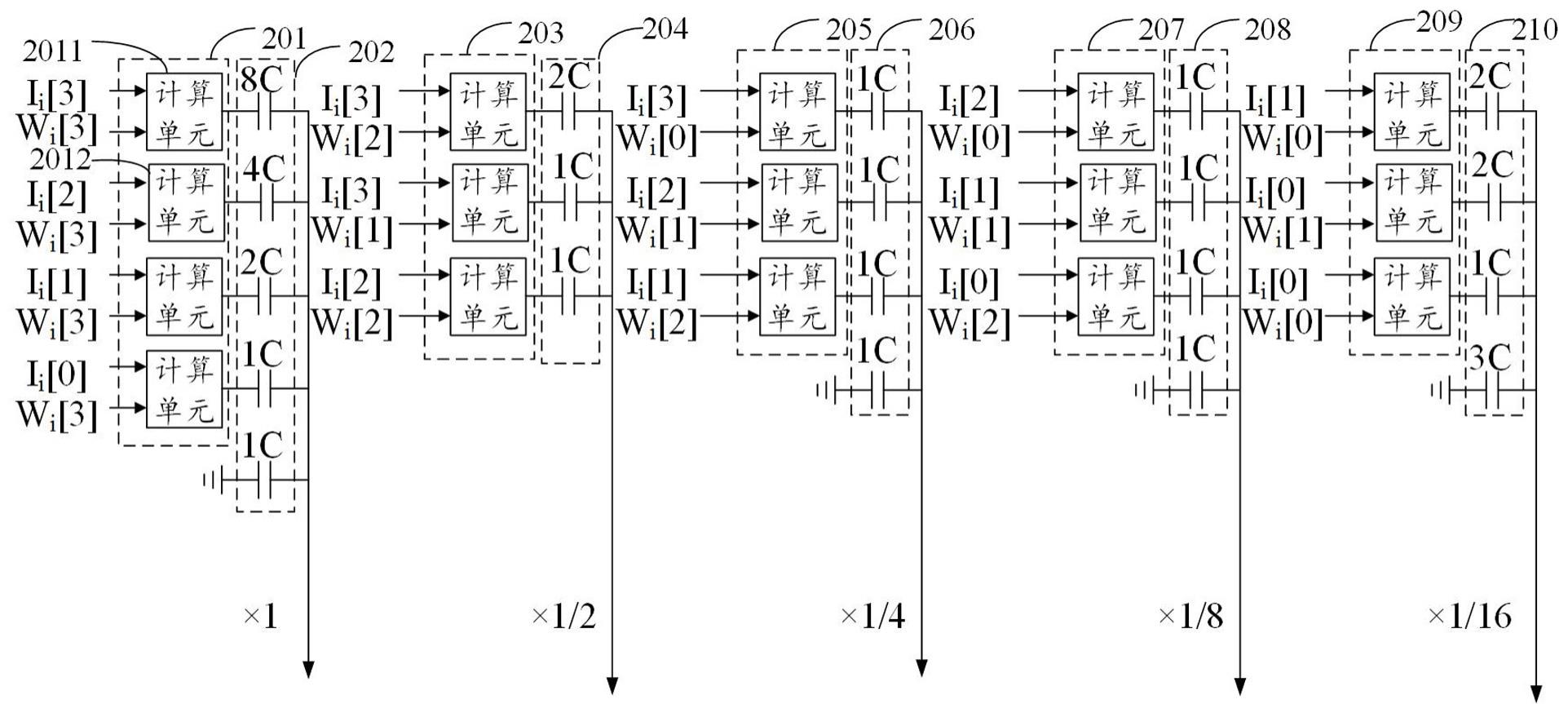

1、基于模拟信号域的存算一体阵列,对于乘累加(mac,multiply accumulate)运算具有重要作用,该种计算方式常应用于深度神经网络算法中,用于执行密集的乘累加运算,且该种计算方式具有高并行度和低功耗的优势。模拟信号域的信号包括电流域、电荷域和时间域等。目前在存算一体阵列中常用的模拟信号为电荷域信号,这是因为在集成电路中电容的加工精度较高,相较于其他两种模拟信号,使用电容实现的电荷域的计算方法具有较好的线性度。

2、目前采用的包含电容的电荷域乘累加方案,每个单比特存储数据(例如神经网络场景下的权重数据中的一个比特位)对应的多个电容的容值均按照1:2:4:8……的比例关系分布,这样,根据电容分压的原理,实现了同一单比特存储数据与多比特输入数据的每个单比特位相乘后,再按照对应权重实现乘积的叠加。

技术实现思路

1、本公开的实施例提供了一种基于模拟信号的多比特数据计算电路,该电路包括:预设数量个计算单元组和预设数量个加法单元组;对于预设数量个计算单元组中的每个计算单元组,该计算单元组对应于目标加法单元组,并具有对应的累加权重,该计算单元组中的每个计算单元的输出端与对应的加法单元的输入端连接;目标加法单元组用于为该计算单元组中的每个计算单元分配对应的数位权重,并对每个计算单元输出的计算结果信号按照对应的数位权重进行累加,将累加结果信号经过该加法单元组的信号输出端输出,其中,每个计算单元对应的数位权重基于目标加法单元组中的每个加法单元的特性度量值和累加权重确定;预设数量个加法单元组中的每个加法单元组包括的各个加法单元的特性度量值的比例关系不同。

2、在一些实施例中,该电路还包括预设数量个模数转换器、移位累加器,其中,预设数量个模数转换器中的每个模数转换器对应一个加法单元组;预设数量个模数转换器中的每个模数转换器用于接收对应的加法单元组输出的累加结果信号,并根据接收的累加结果信号生成数字信号,以及将得到的数字信号发送至移位累加器;移位累加器用于对接收的第二预设数量个数字信号分别按照对应的累加权重进行移位累加操作,得到多比特累加结果数据。

3、在一些实施例中,对于预设数量个计算单元组中的计算单元组,该计算单元组包括的每个计算单元对应一个存储单元,存储单元用于存储单比特存储数据,每个计算单元用于对对应的存储单元中的单比特数据和输入的单比特输入数据进行计算,并将计算结果信号输入对应的加法单元。

4、在一些实施例中,预设数量个计算单元组中的计算单元组由乘法器组成,乘法器用于对对应的存储单元中的单比特存储数据和输入的单比特输入数据进行乘法计算,输出计算结果信号。

5、在一些实施例中,乘法器包括第一开关和第二开关,第一开关用于在乘法器对应的存储单元中的单比特存储数据为第一数据时,将输入的单比特输入数据作为计算结果信号输出,第二开关用于在乘法器对应的存储单元中的单比特存储数据为第二数据时,将预设电平作为计算结果信号输出。

6、在一些实施例中,对于预设数量个加法单元组中的加法单元组,该加法单元组包括的加法单元为电容的容值,且加法单元的特性度量值为电容值;或者,该加法单元组包括的加法单元为晶体管,且加法单元的特性度量值为晶体管的跨导参数。

7、在一些实施例中,对于预设数量个加法单元组中的加法单元组,若该加法单元组由电容组成,该加法单元组输出的累加结果信号为电压信号,该加法单元组对应的模数转换器用于将电压信号转换为数字信号;若该加法单元组由晶体管组成,该加法单元组输出的累加结果信号为电流信号,该加法单元组对应的模数转换器用于将电流信号转换为数字信号。

8、根据本公开实施例的另一个方面,提供了一种芯片,该芯片包括上述基于模拟信号的多比特数据计算电路。

9、根据本公开实施例的另一个方面,提供了一种计算装置,该计算装置包括上述芯片。

10、本公开上述实施例提供的基于模拟信号的多比特数据计算电路、芯片及计算装置,在电路中设置预设数量个计算单元组和预设数量个加法单元组,每个计算单元组对应一个加法单元组,加法单元组为对应的计算单元组中的每个计算单元分配对应的数位权重,并对每个计算单元输出的计算结果信号按照对应的数位权重进行累加,将累加结果信号经过信号输出端输出,每个计算单元对应的数位权重基于对应的加法单元组中的每个加法单元的特性度量值和累加权重确定,且预设数量个加法单元组中的每个加法单元组包括的各个加法单元的特性度量值的比例关系不同。本公开实施例相比于目前的基于模拟信号的多比特数据乘累加电路,无需使每个加法单元组中的各个加法单元按照相同的比例关系分布,在实现了对多比特存储数据和多比特输入数据进行计算及累加的基础上,降低了加法单元的特殊度量值的总和,避免了随着计算数据的位宽的增加,加法单元的特性度量值指数增长的问题,进而有助于降低整个计算电路的面积和功耗。

11、下面通过附图和实施例,对本公开的技术方案做进一步的详细描述。

技术特征:

1.一种基于模拟信号的多比特数据计算电路,包括:预设数量个计算单元组和预设数量个加法单元组;

2.根据权利要求1所述的电路,其中,所述电路还包括预设数量个模数转换器、移位累加器,其中,所述预设数量个模数转换器中的每个模数转换器对应一个加法单元组;

3.根据权利要求1所述的电路,其中,对于所述预设数量个计算单元组中的计算单元组,该计算单元组包括的每个计算单元对应一个存储单元,所述存储单元用于存储单比特存储数据,每个计算单元用于对对应的存储单元中的单比特数据和输入的单比特输入数据进行计算,并将计算结果信号输入对应的加法单元。

4.根据权利要求3所述的电路,其中,所述预设数量个计算单元组中的计算单元组由乘法器组成,所述乘法器用于对对应的存储单元中的单比特存储数据和输入的单比特输入数据进行乘法计算,输出计算结果信号。

5.根据权利要求4所述的电路,其中,所述乘法器包括第一开关和第二开关,所述第一开关用于在所述乘法器对应的存储单元中的单比特存储数据为第一数据时,将输入的单比特输入数据作为计算结果信号输出,所述第二开关用于在所述乘法器对应的存储单元中的单比特存储数据为第二数据时,将预设电平作为计算结果信号输出。

6.根据权利要求1所述的电路,其中,对于所述预设数量个加法单元组中的加法单元组,该加法单元组包括的加法单元为电容的容值,且加法单元的特性度量值为电容值;或者,该加法单元组包括的加法单元为晶体管,且加法单元的特性度量值为晶体管的跨导参数。

7.根据权利要求6所述的电路,其中,对于所述预设数量个加法单元组中的加法单元组,若该加法单元组由电容组成,该加法单元组输出的累加结果信号为电压信号,该加法单元组对应的模数转换器用于将所述电压信号转换为数字信号;

8.一种芯片,其特征在于,包括根据权利要求1-7中任一项所述的基于模拟信号的多比特数据计算电路。

9.一种计算装置,其特征在于,包括根据权利要求8所述的芯片。

技术总结

本公开实施例公开了一种基于模拟信号的多比特数据计算电路、芯片及计算装置,其中,该电路包括:预设数量个计算单元组和预设数量个加法单元组;对于预设数量个计算单元组中的每个计算单元组,该计算单元组对应于目标加法单元组,并具有对应的累加权重,每个计算单元的输出端与对应的加法单元的输入端连接;目标加法单元组用于为该计算单元组中的每个计算单元分配对应的数位权重,并对每个计算单元输出的计算结果信号按照对应的数位权重进行累加,将累加结果信号经过该加法单元组的信号输出端输出;预设数量个加法单元组中的每个加法单元组包括的各个加法单元的特性度量值的比例关系不同。本公开实施例有助于降低整个计算电路的面积和功耗。

技术研发人员:马松,吴强

受保护的技术使用者:上海后摩智能科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!