多FPGA间的连线分配方法、系统、存储介质及电子设备与流程

本发明属于自动化,特别涉及一种多fpga间的连线分配方法、系统、存储介质及电子设备。

背景技术:

1、随着用户设计规模的不断增大,对用户设计的逻辑验证不得不采用多fpga的系统,这时就需要把用户设计分割成指定数量的不同部分,每部分被分配至不同的fpga中运行,各fpga之间采用互连线进行连接,互连线的距离相较于fpga内部距离很大,所以产生的信号延时也大。fpga内部常常由几颗slr(super logic region,超逻辑区域)组成,也成为die。各die呈现的分布呈现一定的拓扑关系,同一颗fpga内部的各个die之间采用highwidth low latency connections(高宽度低延迟连接)的技术进行连接,它们往往具有低延迟,低功耗,高吞吐量等特征。

2、经典的布线方法为按照最短路径进行布线。比如,一个net的驱动节点和负载节点被分配到两块不同的fpga(例如分别命名为a和b)上,那么这条net的路由方法是寻找a,b之间的最短路径,即经过i连通a,b的最少中间中转fpga数量。这种方法简单易行,但是所有的net都按照最短路径路由容易造成某些路径经过的net过多,从而造成拥挤。即现有技术下,由于用户设计规模逐步增大,在布局布线过程中:常常不能统筹规划、平衡所有信号的合理routing路径,造成部分信号routing选择不合理,进而引起个别die crossing处的连接资源使用紧张,甚至导致布局布线过程的失败。因此需要一种在die level对连线分配统筹处理,平衡信号分配路径的方法。

技术实现思路

1、本发明克服了现有技术的不足之一,提供了一种多fpga间的连线分配方法、系统、存储介质及电子设备,能够实现在die level(裸片级)对多fpga间的信号与连线进行统筹分配。

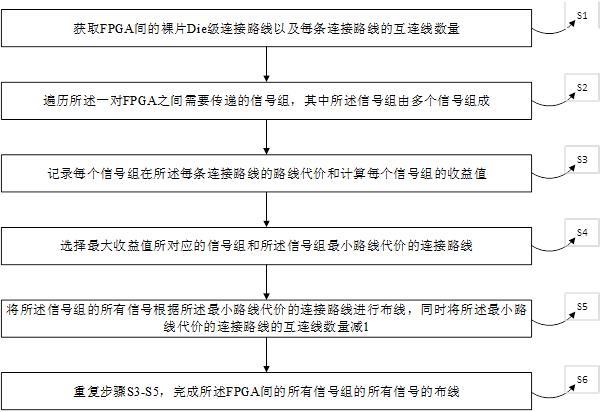

2、根据本公开的一方面,提出了一种多fpga间的连线分配方法,所述方法包括:

3、步骤s1:获取fpga间的裸片die级连接路线以及每条连接路线的互连线数量;

4、步骤s2:遍历所述一对fpga之间需要传递的信号组,其中所述信号组由多个信号组成;

5、步骤s3:记录每个信号组在所述每条连接路线的路线代价和计算每个信号组的收益值;

6、步骤s4:选择最大收益值所对应的信号组和所述信号组最小路线代价的连接路线;

7、步骤s5:将所述信号组的所有信号根据所述最小路线代价的连接路线进行布线,同时将所述最小路线代价的连接路线的互连线数量减1;

8、重复步骤s3-s5,完成所述fpga间的所有信号组的所有信号的布线。

9、在一种可能的实现方式中,将所述信号组的所有信号根据所述最小路线代价的连接路线进行布线,包括:

10、对于同一连接路线进行布线的信号组,将信号总数最大的信号组放置在所述连接路线的互连线的边缘,将信号总数最小的信号组放置在所述信号总数最大的信号组的下方,重复该过程,完成fpga间的信号组的所有信号的布线。

11、在一种可能的实现方式中,所述每条连接路线的互连线的长度相同。

12、在一种可能的实现方式中,所述信号组的多个信号采用时分复用的方式共用一根互连线。

13、在一种可能的实现方式中,所述每个信号组内的多个信号的传播方向一致。

14、在一种可能的实现方式中,每个信号组的收益值为所述每个信号组的所有连接路线的路线代价的最大差值的绝对值。

15、在一种可能的实现方式中,在所述将所述信号组的所有信号根据所述最小路线代价的连接路线进行布线之后,还包括:

16、将根据所述最小路线代价的连接路线进行布线的所述信号组剔除。

17、根据本公开的另一方面,提出了一种多fpga间的连线分配系统,所述系统包括:

18、获取模块,用于获取fpga间的裸片die级连接路线以及每条连接路线的互连线数量;

19、遍历模块,用于遍历所述一对fpga之间需要传递的信号组,其中所述信号组由多个信号组成;

20、计算模块,用于记录每个信号组在所述每条连接路线的路线代价和计算每个信号组的收益值;

21、选择模块,用于选择最大收益值所对应的信号组和所述信号组最小路线代价的连接路线;

22、第一布线模块,用于将所述信号组的所有信号根据所述最小路线代价的连接路线进行布线,同时将所述最小路线代价的连接路线的互连线数量减1;

23、第二布线模块,用于完成所述fpga间的所有信号组的所有信号的布线。

24、根据本公开的另一方面,提出了一种存储介质,其上存储有计算机程序,所述程序被处理器运行时实现如上所述的方法.

25、根据本公开的另一方面,提出了一种电子设备,包括:处理器和存储有计算机程序的存储器,所述处理器被配置为在运行计算机程序时实现如上所述的方法。

26、本公开的多fpga间的连线分配方法,通过获取fpga间的裸片die级连接路线以及每条连接路线的互连线数量;遍历所述一对fpga之间需要传递的信号组,其中所述信号组由多个信号组成;记录每个信号组在所述每条连接路线的路线代价和计算每个信号组的收益值;选择最大收益值所对应的信号组和所述信号组最小路线代价的连接路线;将所述信号组的所有信号根据所述最小路线代价的连接路线进行布线,同时将所述最小路线代价的连接路线的互连线数量减1;重复上述步骤,完成所述fpga间的所有信号组的所有信号的布线。能够实现在die level对多fpga间的信号与连线进行统筹分配。

27、本发明实施例的其他可选特征和技术效果一部分在下文描述,一部分可通过阅读本文而明白。

技术特征:

1.一种多fpga间的连线分配方法,其特征在于,所述方法包括:

2.根据权利要求1所述的连线分配方法,其特征在于,将所述信号组的所有信号根据所述最小路线代价的连接路线进行布线,包括:

3.根据权利要求1所述的连线分配方法,其特征在于,所述每条连接路线的互连线的长度相同。

4.根据权利要求1所述的连线分配方法,其特征在于,所述信号组的多个信号采用时分复用的方式共用一根互连线。

5.根据权利要求4所述的连线分配方法,其特征在于,所述每个信号组内的多个信号的传播方向一致。

6.根据权利要求1所述的连线分配方法,其特征在于,每个信号组的收益值为所述每个信号组的所有连接路线的路线代价的最大差值的绝对值。

7.根据权利要求1所述的连线分配方法,其特征在于,在所述将所述信号组的所有信号根据所述最小路线代价的连接路线进行布线之后,还包括:将根据所述最小路线代价的连接路线进行布线的所述信号组剔除。

8.一种多fpga间的连线分配系统,其特征在于,所述系统包括:

9.一种存储介质,其上存储有计算机程序,其特征在于,所述程序被处理器运行时实现如权利要求1-7中任一所述的方法。

10.一种电子设备,其特征在于,包括:处理器和存储有计算机程序的存储器,所述处理器被配置为在运行计算机程序时实现权利要求1-7中任一所述的方法。

技术总结

本发明涉及的多FPGA间的连线分配方法、系统、存储介质及电子设备。所述多FPGA间的连线分配方法通过获取FPGA间的裸片Die级连接路线以及每条连接路线的互连线数量;遍历所述一对FPGA之间需要传递的信号组,其中所述信号组由多个信号组成;记录每个信号组在所述每条连接路线的路线代价和计算每个信号组的收益值;选择最大收益值所对应的信号组和所述信号组最小路线代价的连接路线;将所述信号组的所有信号根据所述最小路线代价的连接路线进行布线,同时将所述最小路线代价的连接路线的互连线数量减1;重复上述步骤,完成所述FPGA间的所有信号组的所有信号的布线。能够实现在Die level(裸片级)对多FPGA间的信号与连线进行统筹分配。

技术研发人员:邵中尉,孙亚强,张吉锋,周思远

受保护的技术使用者:上海思尔芯技术股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!