一种基于AXI总线双MicroBlaze架构的通信系统和方法与流程

本发明芯片设计技术属于领域,具体涉及一种基于axi总线双microblaze架构的通信系统和方法。

背景技术:

1、近年来,在航空航天,军事装备领域,新研设备的数据链通信,突显出数据总线大幅增多,总线交互愈加频繁,程序逻辑愈加复杂等特点。随着嵌入式技术领域的不断发展,仅采用arm架构设计的微处理器,有着速度受限、资源较少、系统实时性差等问题。只采用fpga系列处理器,又有着开发门槛高、多任务程序逻辑处理难度大等问题。

2、microblaze是标准的risc哈佛处理架构,由执行单元、寄存器群、指令通路和数据通路四部分组成,是可以方便地嵌入在fpga中的32位微处理器。它具备高级可扩展接口axi4,拥有32个32位通用寄存器,单发流水线结构,本地存储总线(lmb)等特点,但microblaze存在主频不高,应对复杂交互运算能力不足等问题。

技术实现思路

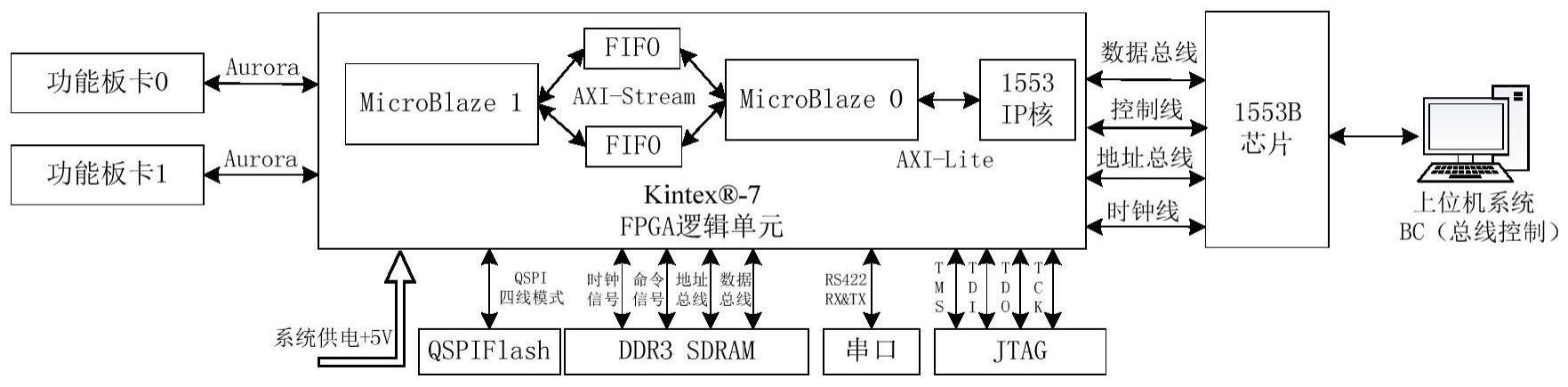

1、针对现有技术的以上缺陷或改进需求中的一种或者多种,本发明提供了一种基于axi总线的双microblaze架构的系统,其特征在于,所述系统包括:处理器、总线芯片、一个或多个功能板卡以及外设;所述处理器通过地址线,数据线,控制线与所述总线芯片通信连接;

2、所述处理器包括:第一软核、第二软核以及接口ip核;所述第一软核与所述总线芯片连接并进行数据交互;所述第二软核作为辅助数据采集处理器,与所述一个或多个功能板卡以及外设进行交互;所述第一软核和所述第二软核之间使用axi-steam实现数据交互;

3、接口ip核用于将所述第一软核传递过来的数据进行解析并根据解析内容控制所述总线芯片;

4、接口ip核用于对所述芯片进行读、写、控制。

5、优选地,所述第二软核通过窗口或aurora总线和所述一个或多个功能板卡建立的通信链路。

6、优选地,所述外设包括flash、ddr、422串口芯片、jtag调试器可在所述处理器数据交互时进行动态监控。

7、优选地,所述系统还包括ilaip核,所述ilaip核连接到所述处理器的逻辑电路关键节点便于监控数据在链路状态。

8、优选地,所述系统还包括mdmip核,所述mdmip核与所述第一软核、所述第二软核连接,实现软核功能程序的单步调试。

9、本发明还提供了一种上述系统的接口通信方法,其特征在于,所述方法包括以下步骤:fpga基础硬件电路设计、pl端硬件逻辑设计、以及所述第一软核和所述第二软核的应用程序设计;

10、所述第一软核和所述第二软核的应用程序设计包括:

11、所述第一软核调用初始化程序对所述处理器以及外设进行初始化,初始化完成后,启动所述第二软核;

12、所述第二软核不间断获取所述处理器中第一寄存器的值,当所述第一软核初始化后,改变所述第一寄存器的值,所述第二软核进入数据处理功能;

13、所述第一软核不断查询中断状态寄存器的值,当总线上有数据需要处理时,所述总线芯片接收来自上位机的数据后并由所述第一软核进行数据校验,数据校验完成后,所述第一软核判断是否进行内部处理或是将数据发送给所述第二软核。

14、总体而言,通过本发明所构思的以上技术方案与现有技术相比,具有的有益效果包括:

15、(1)本发明提供了一种通用的、鲁棒性高的双microblaze架构的接口通信设计方法。并且以具体应用的方式,对核间通信总线的数据吞吐量,数据承载量与应用线程调度冲突问题的解决方式和方法进行了测验。使用k7处理器的逻辑资源上模拟出两个轻量化的处理器microblaze,很好解决了裸机开发下单microblaze主频不高,应对复杂交互运算能力不足等问题,并简化了系统程序逻辑和开发难度。在理论上microblaze的数量和性能,受制于fpga处理器的逻辑资源,故多核间的同步协作,有利于提升多任务处理的并发性和解决程序间的耦合性。。

技术特征:

1.一种基于axi总线的双microblaze架构的系统,其特征在于,所述系统包括:处理器、总线芯片、一个或多个功能板卡以及外设;所述处理器通过地址线,数据线,控制线与所述总线芯片建立物理线路连接;

2.根据权利要求1所述的系统,其特征在于,所述第二软核通过串口或aurora总线和所述一个或多个功能板卡建立的通信链路。

3.根据权利要求1所述的系统,其特征在于,所述外设包括flash、ddr、422串口芯片及jtag调试器可在所述处理器数据交互时进行动态监控。

4.根据权利要求1所述的系统,其特征在于,所述系统还包括ilaip核,所述ilaip核连接到所述处理器的逻辑电路关键节点便于调试模式下监控数据在链路状态。

5.根据权利要求1所述的系统,其特征在于,所述系统还包括mdmip核,所述mdmip核与所述第一软核、所述第二软核连接,实现软核功能程序的单步调试。

6.权利要求1-5中任一系统的接口通信方法,其特征在于,所述方法包括以下步骤:fpga基础硬件电路设计、pl端硬件逻辑设计、以及所述第一软核和所述第二软核的应用程序设计;

技术总结

本发明提供了一种通用的、鲁棒性高的双MicroBlaze架构的接口通信设计方法。并且以具体应用的方式,对核间通信总线的数据吞吐量,数据承载量与应用线程调度冲突问题的解决方式和方法进行了测验。使用K7处理器的逻辑资源上模拟出两个轻量化的处理器MicroBlaze,很好解决了裸机开发下单MicroBlaze主频不高,应对复杂交互运算能力不足等问题,并简化了系统程序逻辑和开发难度。在理论上MicroBlaze的数量和性能,受制于FPGA处理器的逻辑资源,故多核间的同步协作,有利于提升多任务处理的并发性和解决程序间的耦合性。

技术研发人员:谷长春,陈辉,丁俊杰,杨俊华

受保护的技术使用者:湖北三江航天险峰电子信息有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!