一种自适应SPI接口装置及自适应时序校准方法与流程

本发明属于spi通信领域,涉及一种自适应spi接口装置及自适应时序校准方法。

背景技术:

1、spi是一种高速的全双工,同步的通信总线,一般由3或4根线组成。spi接口广泛应用于芯片/设备(本文中“芯片”和“设备”可互换)间通讯如:mcu、flash、eeprom、adc等。

2、spi以主从方式工作,由主芯片发起数据传输,一个主芯片可以连接一个或多个从芯片。

3、实际应用中,主芯片需要根据从芯片spi接口的工作模式配置自己的spi接口的工作模式,只有主从芯片工作模式一致时,两者才能正常、稳定的通信。由于不同类型的芯片或同一类型芯片不同生产厂家的工作模式可能不同,导致主芯片需要人为的修改程序以重新适配从芯片模式,这种方式调试效率低且容易出错。此外,一种更为隐蔽的故障模式是:当主从芯片的spi模式不匹配,总线时序靠近标准时序的临界态时,总线也有可能正常通信,但由于时序余量非常小,系统的可靠性很差,例如在不同的环境温度下通信数据会出现错误,并且这种不稳定态引起的问题在实际工程中也难以排查。

技术实现思路

1、本发明的目的在于克服上述现有技术的缺点,提供一种自适应spi接口装置及自适应时序校准方法,实现了自适应时序,时序免调试,调试效率高。

2、为达到上述目的,本发明采用以下技术方案予以实现:

3、一种自适应spi接口装置,包括主设备接口和从设备接口;

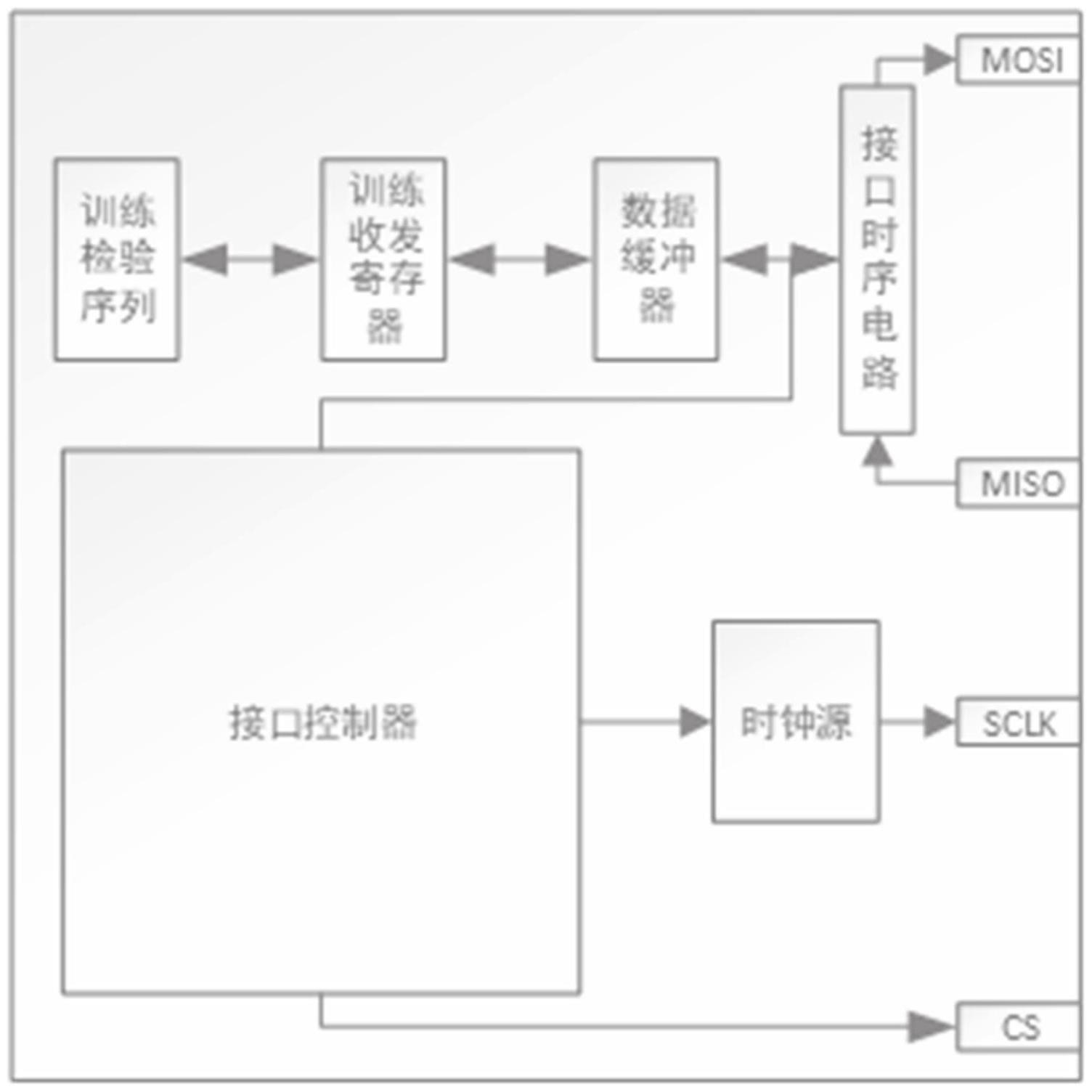

4、主设备接口和/或从设备接口包括数据缓冲器、时钟源、接口控制器、训练校验序列、训练接收寄存器和接口时序电路;训练校验序列与训练接收寄存器交互连接,训练接收寄存器和数据缓冲器交互连接,数据缓冲器和接口时序电路交互连接,接口控制器输出端分别与数据缓冲器、接口时序电路和时钟源输入端连接。

5、优选的,当主设备接口和从设备接口采用四线制连接时,时钟源输入或输出时钟信号,接口时序电路输入或输出片选信号、主出从入信号和主入从出信号。

6、优选的,当主设备接口和从设备接口采用三线制连接时,自时钟源输入或输出时钟信号,接口时序电路输入或输出片选信号和双向数据信号。

7、优选的,主设备接口连接有主设备,从设备接口连接有从设备;

8、主设备和从设备采用fpga、mcu、dsp、cpu、gpu、cpld、flash、pll、adc、dac、放大器、衰减器、收发机或传感器。

9、一种基于上述装置的自适应时序校准方法,包括以下过程:

10、主设备接口和从设备接口连接后,以主设备接口作为自适应端时:

11、s1,主从设备接口进入校准模式,主设备接口发起校准,从设备接口响应校准;

12、s2,主设备接口依次配置多个spi模式;

13、s3,主设备接口配置时钟相位为标准相位,即时钟沿与数据变化对齐;

14、s4,主设备接口写数据到从设备接口,并接收从设备接口的数据;

15、s5,主设备接口判断写和读的数据一致性,如果不一致,回到s2,切换下一spi模式,如果一致,则继续下一步;

16、s6,主设备接口依次配置时钟相位为超前和滞后,即时钟沿相对于数据变化沿超前或滞后一定相位;

17、s7,主设备接口写数据到从设备接口,并接收从设备接口的数据;

18、s8,主设备接口判读写和读的数据一致性,如果不一致,回到s2,切换下一spi模式,如果一致,则结束自适应模式;

19、s9,主设备接口配置成标准相位参数进行正常spi通信;

20、以从设备接口作为自适应端时,与主设备接口自适应过程一致。

21、优选的,spi模式为0、1、2和3。

22、优选的,超前或滞后的时间为1/8或1/4时钟。

23、优选的,s4的具体过程为:第一帧由主设备接口向从设备接口发送训练校验序列,从设备接口按其设置的时序,向从设备接口训练接收寄存器里写入接收采样到的序列。第二帧由主设备接口向从设备接口读取接收采样到的序列,从设备接口按其设置的时序,向主设备接口发射训练接收寄存器数据,主设备接口按spi模式进行数据接收,存入主设备接口的训练接收寄存器。

24、进一步,s5的具体过程为:接收完成后,主设备接口的接口控制器比较训练接收寄存器和之前发送的训练校验序列,若发送数据和接收数据相同,认为该时序配置有效。

25、优选的,若所有spi模式下均写和读的数据不一致,则更换主设备接口。

26、与现有技术相比,本发明具有以下有益效果:

27、本发明通过配置多个spi模式,在正常时钟相位及超前和滞后下,进行写和读数据的一致性比对,若正常时钟相位下发送数据和接收数据相同,认为该时序配置有效,若超前和滞后时钟偏移都配置有效,则认为当前spi时序模式配置正确。实现了自适应时序,时序免调试,调试效率高;实测并使用最佳信号时序,稳定性强;并且发明所述接口兼容性好,能够适配各种厂家芯片的时序,后期硬件更换不需要修改维护软件,降低系统成本。

技术特征:

1.一种自适应spi接口装置,其特征在于,包括主设备接口和从设备接口;

2.根据权利要求1所述的自适应spi接口装置,其特征在于,当主设备接口和从设备接口采用四线制连接时,时钟源输入或输出时钟信号,接口时序电路输入或输出片选信号、主出从入信号和主入从出信号。

3.根据权利要求1所述的自适应spi接口装置,其特征在于,当主设备接口和从设备接口采用三线制连接时,自时钟源输入或输出时钟信号,接口时序电路输入或输出片选信号和双向数据信号。

4.根据权利要求1所述的自适应spi接口装置,其特征在于,主设备接口连接有主设备,从设备接口连接有从设备;

5.一种基于权利要求1-4任意一项所述装置的自适应时序校准方法,其特征在于,包括以下过程:

6.根据权利要求5所述的自适应时序校准方法,其特征在于,spi模式为0、1、2和3。

7.根据权利要求5所述的自适应时序校准方法,其特征在于,超前或滞后的时间为1/8或1/4时钟。

8.根据权利要求5所述的自适应时序校准方法,其特征在于,s4的具体过程为:第一帧由主设备接口向从设备接口发送训练校验序列,从设备接口按其设置的时序,向从设备接口训练接收寄存器里写入接收采样到的序列。第二帧由主设备接口向从设备接口读取接收采样到的序列,从设备接口按其设置的时序,向主设备接口发射训练接收寄存器数据,主设备接口按spi模式进行数据接收,存入主设备接口的训练接收寄存器。

9.根据权利要求8所述的自适应时序校准方法,其特征在于,s5的具体过程为:接收完成后,主设备接口的接口控制器比较训练接收寄存器和之前发送的训练校验序列,若发送数据和接收数据相同,认为该时序配置有效。

10.根据权利要求5所述的自适应时序校准方法,其特征在于,若所有spi模式下均写和读的数据不一致,则更换主设备接口。

技术总结

本发明公开了一种自适应SPI接口装置及自适应时序校准方法,包括主设备接口和从设备接口;主设备接口和/或从设备接口包括数据缓冲器、时钟源、接口控制器、训练校验序列、训练接收寄存器和接口时序电路;训练校验序列与训练接收寄存器交互连接,训练接收寄存器和数据缓冲器交互连接,数据缓冲器和接口时序电路交互连接,接口控制器输出端分别与数据缓冲器、接口时序电路和时钟源输入端连接。实现了自适应时序,时序免调试,调试效率高。

技术研发人员:王晨,郭强,张志军,付小伟,李刚,李庆

受保护的技术使用者:西安思丹德信息技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!