一种FPGA内部自激振荡产生时钟信号的方法及系统与流程

本发明涉及fpga使用,具体涉及一种fpga内部自激振荡产生时钟信号的方法及系统。

背景技术:

1、现代电子设备一般都需要使用到时钟信号,时钟信号是时序逻辑的基础,用于决定逻辑单元中的状态何时更新处理。时钟信号常被用于同步电路当中,扮演计时器的角色,保证相关的电子组件得以同步运作。

2、时钟信号可用于同步cpu、dsp、fpga、ddr等芯片的不同进程,通过时钟信号的上升沿或下降沿来改变周期输出,从而使得芯片内部实现严格按照时钟信号周期来处理的时序功能。

3、时钟信号的特征是定时下信号高低电平的转换变化。时钟信号包括低电平和高电平,最常见的时钟信号的高低电平的时间分布为50%的占空比,高电平和低电平的持续时间是相同的,即固定的常数频率方波形式。cpu、dsp、fpga、ddr等芯片内部电路在使用时钟信号后,内部电路会在任一上升沿、下降沿进行处理或在上升沿、下降沿同时处理,得到双数据速率。

4、现今fpga内部的设计大多采用时序逻辑,需使用时钟信号才能工作,通常情况下,fpga所需的时钟信号是通过外部晶体振荡器产生供给的。虽然大多数情况下使用外部的晶体振荡器产生供给时钟信号是较好的选择,但晶体振荡器的使用也是存在问题的,如:现今常用的晶体振荡器为石英晶体振荡器,石英晶体振荡器对温度漂移敏感,且也易碎。对于一些外部环境特别恶劣的场景,也应避免晶体振荡器的使用,如:导引头制导电路、外太空使用的电子设备、温度骤变、大量辐射等外部环境特别恶劣的场景。另外,有些芯片、器件对时钟信号质量要求是比较高的,如ddr存储芯片,外部时钟信号走线过程复杂,经过外部走线的高频时钟信号进入fpga前容易产生信号损失的误差,这样会导致进入fpga后的时钟信号无法满足ddr存储芯片等外挂配套的使用要求。

技术实现思路

1、发明目的:本发明目的是提供一种fpga内部自激振荡产生时钟信号的方法及系统,解决了当前fpga所需外部时钟信号所带来的缺点和不便。本发明可实现fpga内部自激振荡产生时钟信号,从而使得fpga不再需要外部时钟信号,也使得fpga使用时钟信号过程中不再受外部走线的干扰,节省了硬件器件,提高了fpga使用时钟信号过程中的便捷性、可操作性。

2、技术方案:一种fpga内部自激振荡产生时钟信号的方法,该方法包括以下步骤:

3、步骤1:fpga上电后内部电路产生电压信号,fpga内部的硬件延迟单元接收电压信号并进行固定时间延迟,而后输出至fpga内部的取反单元;

4、步骤2:取反单元对接收到的信号进行高低电平的翻转,而后输出至硬件延迟单元及fpga内部的锁相环;

5、步骤3:硬件延迟单元对接收到的信号会再次进行固定时间延迟,而后再次输出至取反单元;

6、步骤4:重复步骤2、3,取反单元不断输出信号;

7、其中,取反单元输出信号即为fpga内部硬件延迟单元、取反单元构建闭合组合逻辑链自激振荡产生的时钟信号。

8、进一步的,步骤2中,所述锁相环用于对接收到的时钟信号进行分频处理或倍频处理,而后输出。

9、进一步的,所述锁相环输出的时钟信号会输送至fpga内部的数字信号处理模块,所述数字信号处理模块用于对接收到的数字信号进行表示。

10、进一步的,所述fpga外部连接配设器件,所述锁相环输出的时钟信号会输送至所述配设器件。

11、进一步的,所述硬件延迟单元由n个时钟缓冲器组合而成,所述硬件延迟单元接收到的信号会经时钟缓冲器依次传输,通过改变时钟缓冲器的数量,可以改变所述取反单元输出的时钟信号的频率。

12、进一步的,单个时钟缓冲器的固定延迟时间为t,所述取反单元输出的时钟信号频率为f,则

13、进一步的,所述配设器件为ddr存储芯片。

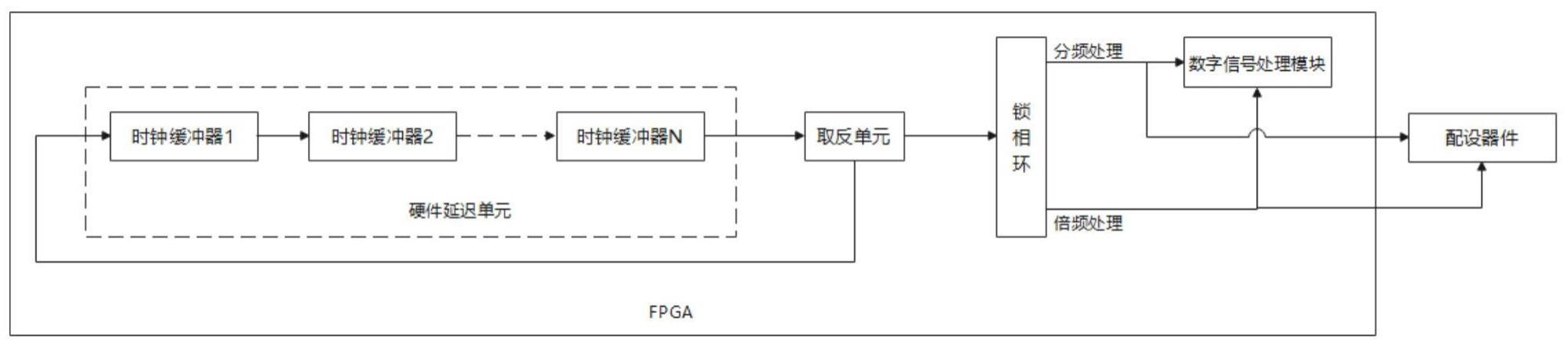

14、一种fpga内部自激振荡产生时钟信号的系统,该系统包括fpga及fpga外部连接的配设器件,fpga内部包括硬件延迟单元、取反单元、锁相环及数字信号处理模块;

15、其中,所述硬件延迟单元用于对接收到的信号进行固定时间延迟;

16、所述取反单元用于对接收到的信号进行高低电平的翻转;

17、所述锁相环用于处理接收到的时钟信号;

18、所述数字信号处理模块用于对接收到的数字信号进行表示。

19、进一步的,所述fpga上电后内部电路产生电压信号,所述硬件延迟单元接收电压信号并进行固定时间延迟,而后输出至取反单元,所述取反单元对接收到的信号进行高低电平的翻转,而后输出至硬件延迟单元及锁相环,所述硬件延迟单元对接收到的信号会再次进行固定时间延迟,而后再次输出至取反单元,重复操作,所述取反单元不断输出信号,所述取反单元输出信号即为fpga内部硬件延迟单元、取反单元构建闭合组合逻辑链自激振荡产生的时钟信号。

20、进一步的,所述硬件延迟单元由n个时钟缓冲器组合而成,所述硬件延迟单元接收到的信号会经时钟缓冲器依次传输,所述取反单元向所述锁相环输出时钟信号,所述锁相环对接收到的时钟信号进行分频处理或倍频处理,而后输出至数字信号处理模块及配设器件。

21、本发明的有益效果:

22、1、本发明fpga内部硬件延迟单元、取反单元构建闭合组合逻辑链自激振荡产生的时钟信号,使得fpga不再需要使用外部时钟信号,有效避免外部时钟信号使用所带来的缺点和不便,如:晶体振荡器使用时存在的问题、外部时钟信号走线复杂所带来的问题等;

23、2、本发明fpga不需要外部时钟信号也可以让内部锁相环工作,锁相环会对接收到的时钟信号进行分频或倍频处理,可以满足产生特殊频点的功能,时钟信号不受外部走线影响,可保证时钟信号的质量,有效避免时钟信号干扰而导致一些器件不能使用。

技术特征:

1.一种fpga内部自激振荡产生时钟信号的方法,其特征在于,该方法包括以下步骤:

2.根据权利要求1所述的一种fpga内部自激振荡产生时钟信号的方法,其特征在于,步骤2中,所述锁相环用于对接收到的时钟信号进行分频处理或倍频处理,而后输出。

3.根据权利要求2所述的一种fpga内部自激振荡产生时钟信号的方法,其特征在于,所述锁相环输出的时钟信号会输送至fpga内部的数字信号处理模块,所述数字信号处理模块用于对接收到的数字信号进行表示。

4.根据权利要求2所述的一种fpga内部自激振荡产生时钟信号的方法,其特征在于,所述fpga外部连接配设器件,所述锁相环输出的时钟信号会输送至所述配设器件。

5.根据权利要求1所述的一种fpga内部自激振荡产生时钟信号的方法,其特征在于,所述硬件延迟单元由n个时钟缓冲器组合而成,所述硬件延迟单元接收到的信号会经时钟缓冲器依次传输,通过改变时钟缓冲器的数量,可以改变所述取反单元输出的时钟信号的频率。

6.根据权利要求5所述的一种fpga内部自激振荡产生时钟信号的方法,其特征在于,单个时钟缓冲器的固定延迟时间为t,所述取反单元输出的时钟信号频率为f,则

7.根据权利要求4所述的一种fpga内部自激振荡产生时钟信号的方法,其特征在于,所述配设器件为ddr存储芯片。

8.一种fpga内部自激振荡产生时钟信号的系统,其特征在于,该系统包括fpga及fpga外部连接的配设器件,fpga内部包括硬件延迟单元、取反单元、锁相环及数字信号处理模块;

9.根据权利要求8所述的一种fpga内部自激振荡产生时钟信号的系统,其特征在于,所述fpga上电后内部电路产生电压信号,所述硬件延迟单元接收电压信号并进行固定时间延迟,而后输出至取反单元,所述取反单元对接收到的信号进行高低电平的翻转,而后输出至硬件延迟单元及锁相环,所述硬件延迟单元对接收到的信号会再次进行固定时间延迟,而后再次输出至取反单元,重复操作,所述取反单元不断输出信号,所述取反单元输出信号即为fpga内部硬件延迟单元、取反单元构建闭合组合逻辑链自激振荡产生的时钟信号。

10.根据权利要求9所述的一种fpga内部自激振荡产生时钟信号的系统,其特征在于,所述硬件延迟单元由n个时钟缓冲器组合而成,所述硬件延迟单元接收到的信号会经时钟缓冲器依次传输,所述取反单元向所述锁相环输出时钟信号,所述锁相环对接收到的时钟信号进行分频处理或倍频处理,而后输出至数字信号处理模块及配设器件。

技术总结

本发明公开了一种FPGA内部自激振荡产生时钟信号的方法及系统,涉及FPGA使用技术领域,该方法为硬件延迟单元接收电压信号并进行固定时间延迟,而后输出至取反单元,取反单元对接收到的信号进行高低电平的翻转,而后输出至硬件延迟单元及锁相环,硬件延迟单元对接收到的信号再次进行固定时间延迟,而后再次输出至取反单元,重复操作,取反单元不断输出信号,即时钟信号。该系统包括FPGA及FPGA外部连接的配设器件,FPGA内部包括硬件延迟单元、取反单元、锁相环及数字信号处理模块,FPGA内部硬件延迟单元、取反单元构建闭合组合逻辑链自激振荡产生时钟信号。本发明可实现FPGA内部自激振荡产生时钟信号,使得FPGA不再需要外部时钟信号及不再受外部时钟信号走线的干扰。

技术研发人员:聂晓鸿,戴大海

受保护的技术使用者:矩阵时光数字科技有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!