一种对加法器进行时序分析的方法及装置与流程

本发明属于fpga领域,尤其是涉及一种对加法器进行时序分析的方法及装置。

背景技术:

1、加法器是fpga内部最基本的运算模块,使用加法器可以实现减法、乘法、除法等算数运算逻辑,现在的fpga芯片通常会采用超前进位加法器,以减少多位加法器的进位延时,由于超前进位加法器,进位不是逐级传递的,而是提前跨越多级提前计算出来的,因此以往的时序分析方法不能满足针对进位链的时序分析。

技术实现思路

1、本发明所要解决的技术问题是怎样对所有种类的加法器进行时序分析,提出了一种对加法器进行时序分析的方法及装置。

2、为解决上述技术问题,本发明所采用的技术方案是:

3、一种对加法器进行时序分析的方法,包括以下步骤:

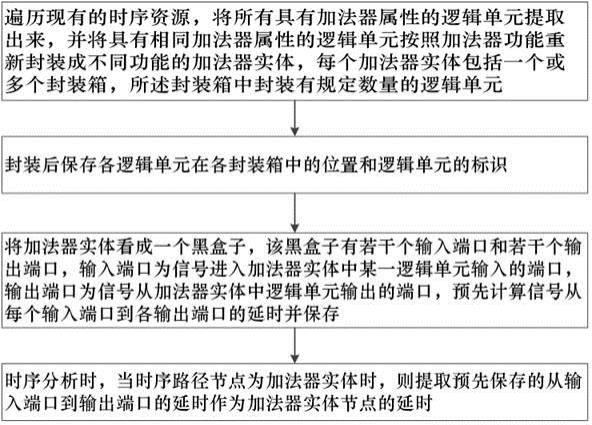

4、步骤1:遍历现有的时序资源,将所有具有加法器属性的逻辑单元提取出来,并将具有相同加法器属性的逻辑单元按照加法器功能重新封装成不同功能的加法器实体,每个加法器实体包括一个或多个封装箱,所述封装箱中封装有规定数量的逻辑单元;

5、步骤2:封装后保存各逻辑单元在各封装箱中的位置和逻辑单元的标识;

6、步骤3:将加法器实体看成一个黑盒子,该黑盒子有若干个输入端口和若干个输出端口,输入端口为信号进入加法器实体中某一逻辑单元输入的端口,输出端口为信号从加法器实体中逻辑单元输出的端口,预先计算信号从每个输入端口到各输出端口的延时并保存;

7、步骤4:时序分析时,当时序路径节点为加法器实体时,则提取预先保存的从输入端口到输出端口的延时作为加法器实体节点的延时。

8、进一步地,步骤3中预先计算信号从每个输入端口到各输出端口的延时的方法是:

9、根据输入端口和输出端口各自所在的逻辑单元位置,判断输入端口和输出端口是否位于封装箱的一个半区,若是,则计算从输入端口到输出端口所经过的几个逻辑单元的延时加上输出端口的延时;若不是,则计算输入端口所在封装箱半区的延时,再将从输入端口到输出端口所经过的其他几个封装箱的半区的延时累加,再加上输出端口的延时得到从输入端口到输出端口的延时。

10、进一步地,步骤1中重新封装时采用尾对齐的装箱策略,所述尾对齐的装箱策略是指,对具有相同加法器属性的逻辑单元按照加法器功能封装成不同功能的加法器实体时,根据加法器实体所包含的封装箱个数,使逻辑单元从最后一个封装箱的最后一个位置开始装箱。

11、本发明还提供了一种对加法器进行时序分析装置,包括以下模块:

12、重新封装模块:用于遍历现有的时序资源,将所有具有加法器属性的逻辑单元提取出来,并将具有相同加法器属性的逻辑单元按照加法器功能封装成不同功能的加法器实体,每个加法器实体包括一个或多个封装箱,所述封装箱中封装有规定数量的逻辑单元;

13、位置保存模块:用于封装后保存各逻辑单元在各封装箱中的位置和逻辑单元的标识;

14、延时预先计算模块:用于将加法器实体看成一个黑盒子,该黑盒子有若干个输入端口和若干个输出端口,输入端口为信号进入加法器实体中某一逻辑单元输入的端口,输出端口为信号从加法器实体中逻辑单元输出的端口,预先计算信号从每个输入端口到各输出端口的延时并保存;

15、时序分析模块:用于当时序路径节点为加法器实体时,则提取预先保存的从输入端口到输出端口的延时作为加法器实体节点的延时。

16、进一步地,预先计算信号从每个输入端口到各输出端口的延时的方法是:

17、根据输入端口和输出端口各自所在的逻辑单元位置,判断输入端口和输出端口是否位于封装箱的一个半区,若是,则计算从输入端口到输出端口所经过的几个逻辑单元的延时加上输出端口的延时;若不是,则计算输入端口所在封装箱半区的延时,再将从输入端口到输出端口所经过的其他几个封装箱的半区的延时累加,再加上输出端口的延时得到从输入端口到输出端口的延时。

18、进一步地,所述重新封装模块在重新封装时,采用尾对齐的装箱策略,所述尾对齐的装箱策略是指,对具有相同加法器属性的逻辑单元按照加法器功能封装成不同功能的加法器实体时,根据加法器实体所包含的封装箱个数,使逻辑单元从最后一个封装箱的最后一个位置开始装箱。采用上述技术方案,本发明具有如下有益效果:

19、本发明提供的一种对加法器进行时序分析的方法及装置,通过将有加法器属性的逻辑单元cell都单独提取出来重新封装成一个个加法器箱子,从而使加法器逻辑单元独立出来,并且发现,加法器在时序分析时,其时序计算只与信号所输入的端口以及输出端口,以及输入和输出端口中间跨越逻辑单元的长度有关,与半区内有多少个逻辑单元无关,也不关心输出端口在半区的哪个逻辑单元上,因此预先计算出加法器实体中每个输入端口到各输出端口的延时并保存,在以后的时序分析中,对于加法器实体,只需要提取保存的时序延时即可,由于在一个fpga中,有很多不同功能的加法器实体,通过本发明的方法,可以节省大量的延时计算时间,提高了时序分析的速度。

技术特征:

1.一种对加法器进行时序分析的方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的方法,其特征在于,步骤3中预先计算信号从每个输入端口到各输出端口的延时的方法是:

3.根据权利要求2所述的方法,其特征在于,步骤1中重新封装时采用尾对齐的装箱策略,所述尾对齐的装箱策略是指,对具有相同加法器属性的逻辑单元按照加法器功能封装成不同功能的加法器实体时,根据加法器实体所包含的封装箱个数,使逻辑单元从最后一个封装箱的最后一个位置开始装箱。

4.一种对加法器进行时序分析装置,其特征在于,包括以下模块:

5.根据权利要求4所述的装置,其特征在于,预先计算信号从每个输入端口到各输出端口的延时的方法是:

6.根据权利要求5所述的装置,其特征在于,所述重新封装模块在重新封装时,采用尾对齐的装箱策略,所述尾对齐的装箱策略是指,对具有相同加法器属性的逻辑单元按照加法器功能封装成不同功能的加法器实体时,根据加法器实体所包含的封装箱个数,使逻辑单元从最后一个封装箱的最后一个位置开始装箱。

技术总结

本发明提供了一种对加法器进行时序分析的方法及装置,通过将有加法器属性的逻辑单元Cell都单独提取出来重新封装成加法器箱子,从而使加法器逻辑单元独立出来,并且发现,加法器在时序分析时,其时序计算只与信号所输入的端口以及输出端口有关,因此预先计算出每个输入端口到各输出端口的延时并保存,在以后的时序分析中,对于加法器,只需要提取保存的时序延时即可,由于在一个FPGA中,有很多的加法器,通过本发明的方法,可以节省大量的延时计算时间,提高了时序分析的速度。

技术研发人员:曲志明,吴明杰,刘洋

受保护的技术使用者:中科亿海微电子科技(苏州)有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!