量子算法的拓扑结构构建方法、装置、设备及介质与流程

本申请适用于量子计算,尤其涉及一种量子算法的拓扑结构构建方法、装置、设备及介质。

背景技术:

1、目前,量子算法主要在链式或者网状的通用量子计算芯片中执行,通过拓扑计算找到其中能够满足运算的一个较优拓扑结构,并进行映射后在指定的几个物理比特上运行该量子算法。然而,链式或者网状的芯片尽管能够满足算法的拓扑结构,但是,由于当前的体系大多数物理比特只能两两耦合,若较远比特耦合纠缠需要使用swap传递等方式,对于比特数较多的量子算法,该实现形式会带来无谓的开销与保真度下降,还可能导致量子算法在物理体系内的量子比特的相干时间上限内无法执行完成。因此,为了减少量子算法的开销,提高量子算法实现的保真度,实现量子算法的执行,可以设计专用量子芯片来实现量子算法,通过采用更特殊的结构实现三比特纠缠的量子门,如ccx,来构建专用量子芯片。

技术实现思路

1、本申请的发明人发现,由于芯片的布线和元器件的工艺受限,在设计专用量子芯片时,需要对量子算法的比特之间的连接拓扑进行优化,以在有限的工艺条件下,尽量接近所执行量子算法理想的拓扑,以降低量子算法执行过程中设置额外操作的数量,从而达到减少量子算法的开销,提高量子算法实现的保真度,以及减少量子算法的执行时间的目的。有鉴于此,本申请实施例提供了一种量子算法的拓扑结构构建方法、装置、设备及介质。

2、第一方面,本申请实施例提供一种量子算法的拓扑结构构建方法,所述方法包括:

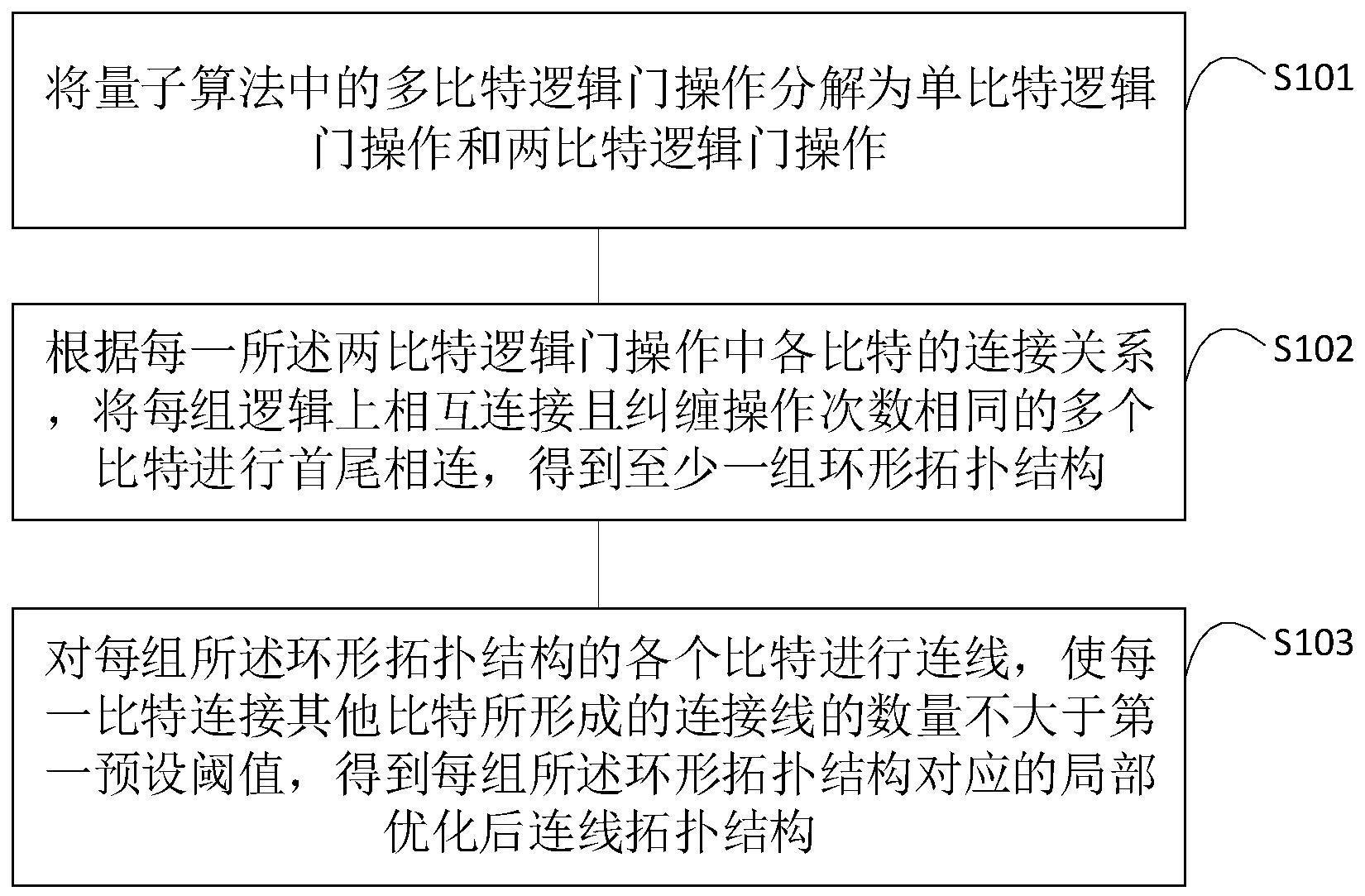

3、将量子算法中的多比特逻辑门操作分解为单比特逻辑门操作和两比特逻辑门操作;

4、根据每一所述两比特逻辑门操作中各比特的连接关系,将每组逻辑上相互连接且纠缠操作次数相同的多个比特进行首尾相连,得到至少一组环形拓扑结构;

5、对每组所述环形拓扑结构的各个比特进行连线,使每一比特连接其他比特所形成的连接线的数量不大于第一预设阈值,得到每组所述环形拓扑结构对应的局部优化后连线拓扑结构。

6、第二方面,本申请实施例提供一种量子算法的拓扑结构构建装置,所述装置包括:

7、算法分解模块,用于将量子算法中的多比特逻辑门操作分解为单比特逻辑门操作和两比特逻辑门操作;

8、环构建模块,用于根据每一所述两比特逻辑门操作中各比特的连接关系,将每组逻辑上相互连接且纠缠操作次数相同的多个比特进行首尾相连,得到至少一组环形拓扑结构;

9、拓扑优化模块,用于对每组所述环形拓扑结构的各个比特进行连线,使每一比特连接其他比特所形成的连接线的数量不大于第一预设阈值,得到每组所述环形拓扑结构对应的局部优化后连线拓扑结构。

10、第三方面,本申请实施例提供一种计算机设备,所述计算机设备包括处理器、存储器以及存储在所述存储器中并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现如第一方面所述的量子算法的拓扑结构构建方法。

11、第四方面,本申请实施例提供一种计算机可读存储介质,所述计算机可读存储介质存储有计算机程序,所述计算机程序被处理器执行时实现如第一方面所述的量子算法的拓扑结构构建方法。

12、本申请实施例与现有技术相比存在的有益效果是:

13、本申请实施例提供的量子算法的拓扑结构构建方法,通过确定量子算法中每一两比特逻辑门操作中各比特的连接关系,构建环形拓扑结构,通过优化环形拓扑结构中各个比特之间的连接线,使得各个比特之间尽可能的两两相连,得到每组环形拓扑结构对应的局部优化后连线拓扑结构,实现对量子算法的比特之间的连接拓扑优化,从而可以使用该局部优化后连线拓扑结构来指导构建芯片拓扑,以在有限的工艺条件下,尽量接近所执行量子算法理想的拓扑,降低在执行量子算法时因两比特间没有直接连接导致设置额外操作的数量,从而降低量子算法在专用量子芯片中执行的耗时,最大程度的减少量子算法的开销,提高量子算法实现的保真度,提升了量子算法的执行效率。

技术特征:

1.一种量子算法的拓扑结构构建方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述对每组所述环形拓扑结构的各个比特进行连线,使每一比特连接其他比特所形成的连接线的数量不大于第一预设阈值,得到每组所述环形拓扑结构对应的局部优化后连线拓扑结构,包括:

3.根据权利要求2所述的方法,其特征在于,所述对所述环形拓扑结构的各个比特进行连线,使每一比特连接其他比特所形成的连接线的数量不大于第一预设阈值,得到所述环形拓扑结构对应的局部优化后连线拓扑结构,包括:

4.根据权利要求3所述的方法,其特征在于,所述以所述环形拓扑结构中每一比特连接其他比特所形成的连接线的数量不大于第一预设阈值为条件,对所述环形拓扑结构的各个比特进行连线,得到所述环形拓扑结构中每个比特的至少一组连接线组合方式,包括:

5.根据权利要求1所述的方法,其特征在于,还包括:

6.根据权利要求1-5任一项所述的方法,其特征在于,还包括:

7.根据权利要求6所述的方法,其特征在于,还包括:

8.根据权利要求7所述的方法,其特征在于,所述根据所述至少一种芯片拓扑结构,确定至少一种芯片结构设计结果,包括:

9.根据权利要求7所述的方法,其特征在于,还包括:

10.一种计算机设备,其特征在于,所述计算机设备包括处理器、存储器以及存储在所述存储器中并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现如权利要求1至9任一项所述的量子算法的拓扑结构构建方法。

技术总结

本申请涉及一种量子算法的拓扑结构构建方法、装置、设备及介质。该方法包括:将量子算法中的多比特逻辑门操作分解为单比特逻辑门操作和两比特逻辑门操作;根据每一两比特逻辑门操作中各比特的连接关系,将每组逻辑上相互连接且纠缠操作次数相同的多个比特进行首尾相连,得到至少一组环形拓扑结构;对每组环形拓扑结构的各个比特进行连线,使每一比特连接其他比特所形成的连接线的数量不大于第一预设阈值,得到每组环形拓扑结构对应的局部优化后连线拓扑结构。使用该局部优化后连线拓扑结构来指导构建芯片拓扑,以在有限工艺条件,降低量子算法在专用量子芯片中执行耗时,最大程度减少量子算法的开销,提高量子算法实现的保真度。

技术研发人员:林育丞,梁潇,郭聪,孟铁军,项金根

受保护的技术使用者:深圳量旋科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!