主机与从机之间的通信系统和通信方法与流程

本申请涉及电子或者芯片,具体涉及一种主机与从机之间的通信系统和通信方法。

背景技术:

1、现在的i2c(inter-integrated circuit)通信在消费电子产品上越来越普及,在很多电子产品上都有i2c接口。i2c通信应用场景广泛,技术成熟,现在很多芯片之间的交互,数据传输以及读取,就是通过i2c通信来实现的,但有些时候标准模式的i2c通信并不能满足所有的应用场景。

2、实际应用中,有些时候芯片为了省片内资源,降低成本,并不支持i2c master以标准模式对从机芯片内的所有寄存器读和写,但在一些应用场景下,外界的i2c master又需要与从机进行通信,进而知道从机的寄存器各种数据,因此,如何在芯片不支持i2c master以标准模式对从机芯片内的所有寄存器读和写的情况下,实现主机与从机之间通信的问题亟待解决。

技术实现思路

1、本申请实施例提供了一种主机与从机之间的通信系统和通信方法,能够实现在芯片不支持i2c master以标准模式对从机芯片内的所有寄存器读和写的情况下,实现主机与从机之间通信。

2、第一方面,本申请实施例提供一种主机与从机之间的通信系统,所述通信系统包括主机和从机,所述主机与从机之间通过三根线进行通信,具体为:所述三根线包括:sck线、sda线和int线;

3、所述主机的sck_m引脚通过所述sck线直连所述从机的sck_s引脚;所述主机的sda_m引脚通过所述sda线直连所述从机的sda_s引脚;所述主机的int_m引脚通过所述int线直连所述从机的int_s引脚;所述sck_m引脚、所述sck_s引脚均通过第一电阻r1连接电源vcc;所述sda_m引脚、所述sda_s引脚通过第二电阻r2连接所述电源vcc;

4、在所述主机与所述从机之间的逻辑电平误差的绝对值小于预设阈值时,所述主机通过读取所述int_m引脚的逻辑电平状态判断所述从机的工作状态,在确定所述从机接收所述主机的一整个通信过程完成后,提醒所述主机以i2c标准模式去可读或写所述从机中的中间寄存器的数据,以通过该数据识别通信结果。

5、第二方面,本申请实施例提供一种应用于如第一方面所述的通信系统,所述方法包括:

6、当所述主机进行写操作a,完成一整个通信过程后的i2c_irq_count为6,确定所述从机已经接收到了所述主机写入的6个8bit数据,其中,该6个8bit数据包括:一个8bit数据为write_mode、一个8bit的addr和一个32bit的data;所述i2c_irq_count表示所述主机向所述从机每次写周期进入i2c中断服务函数的次数;所述写操作a包括6个i2c标准写周期和1个i2c标准读周期;

7、当完整一个写操作a完成后,如果所述主机读取到的read_reg[0]中间寄存器值不是6,则说明通信异常;

8、当所述主机进行读操作b,完成一整个通信过程后的i2c_irq_count为2,确定所述从机接收到所述主机写入的2个8bit数据,所述2个8bit数据包括一个8bit的read_mode和一个8bit的addr;所述读操作b包括2个i2c标准写周期和5个i2c标准读周期;

9、当完整一个读操作b完成后,如果所述主机读取到的read_reg[0]中间寄存器值不是2,则说明通信异常。

10、第三方面,本申请实施例提供一种芯片,该芯片包括如第一方面所述的通信系统。

11、第四方面,本申请实施例提供一种电子设备,所述电子设备包括第一方面所述的通信系统,或者,所述电子设备包括如第三方面所述的芯片。

12、实施本申请实施例,具有如下有益效果:

13、基于本申请实施例所提供的主机与从机之间的通信系统和通信方法,该通信系统包括主机和从机,主机与从机之间通过三根线进行通信,具体为:三根线包括:sck线、sda线和int线,主机的sck_m引脚通过sck线直连从机的sck_s引脚;主机的sda_m引脚通过sda线直连从机的sda_s引脚;主机的int_m引脚通过int线直连从机的int_s引脚;sck_m引脚、sck_s引脚均通过第一电阻r1连接电源vcc;sda_m引脚、sda_s引脚通过第二电阻r2连接电源vcc,在主机与从机之间的逻辑电平误差的绝对值小于预设阈值时,主机通过读取int_m引脚的逻辑电平状态判断从机的工作状态,在确定从机接收主机的一整个通信过程完成后,提醒主机以i2c标准模式去可读或写从机中的中间寄存器的数据,以通过该数据识别通信结果,能够实现在芯片不支持i2c master以标准模式对从机芯片内的所有寄存器读和写的情况下,实现主机与从机之间通信,并且具有通信自校验、加密防破解功能、通信超时功能和从机唤醒功能。

技术特征:

1.一种主机与从机之间的通信系统,其特征在于,所述通信系统包括主机和从机,所述主机与从机之间通过三根线进行通信,具体为:所述三根线包括:sck线、sda线和int线;

2.根据权利要求1所述的通信系统,其特征在于,在所述sda_m引脚、所述sda_s引脚之间的逻辑电平误差的绝对值大于或等于所述预设阈值时,所述sda_m引脚通过第三电阻r3连接主机电源master_vcc,该master_vcc通过第四电阻r4连接所述sck_m引脚;

3.根据权利要求1或2所述的通信系统,其特征在于,在所述int_m引脚与所述int_s引脚之间的逻辑电平误差的绝对值大于或等于所述预设阈值时,所述int_m引脚通过第七电阻r7连接主机电源master_vcc;所述int_m引脚连接第三nmos管q3的源极,所述第三nmos管q3的栅极连接从机电源slave_vcc和所述第四nmos管q4的栅极,以及通过第九电阻r9连接所述第四nmos管q4的漏极;所述第三nmos管q3的栅极还通过第十电阻r10连接所述第三nmos管q3的漏极和所述int_s引脚;所述第四nmos管q4的源极还通过所述第八电阻r8连接所述master_vcc。

4.根据权利要求1或2所述的通信系统,其特征在于,所述int_s引脚,用于在通信空闲时,且不是所述从机待机时,输出高电平;当所述从机进入待机时,输出低电平;

5.根据权利要求4所述的通信系统,其特征在于,所述写操作a包括:

6.根据权利要求4所述的通信系统,其特征在于,所述读操作b包括:

7.一种通信方法,其特征在于,应用如权利要求1-5任一项所述的主机与从机之间的通信系统,所述方法包括:

8.根据权利要求7所述的方法,其特征在于,所述方法还包括:

9.根据权利要求8所述的方法,其特征在于,在所述写操作a固定初始写秘钥为0x7f,二进制为:0111 1111时,所述预设规则为:所述主机每往所述从机写入一个数据,将所述初始写秘钥0x7f从最低位到第七位叠加逐步取反,第二次写操作a是最低一位取反,第三次写操作a是低二位取反,第八次写操作a是低七位取反;记前八次写操作a的密钥数据为keys1,该keys1为0x00,第九次写操作a将所述keys1最低一位取反;第十五次写操作a将所述keys1低七位全部取反,记第十五次写操作a的密钥数据为keys2;keys2就是初始写秘钥0x7f;

10.根据权利要求9所述的方法,其特征在于,在所述读操作b固定初始读秘钥为0x00,二进制为:0000 0000时,所述预设规则为:所述主机每往所述从机读一个数据,将所述初始读秘钥0x00从最低位到第七位叠加逐步取反,第二次读操作b是最低一位取反,第三次读操作b是低二位取反,第八次读操作b是低七位取反,记前八次读操作b的密钥数据为keys3,该keys3为0x7f,第九次读操作b是把keys3最低一位取反;第十五次读操作b将keys3低七位全部取反,记第十五次读操作b的密钥数据为keys4,所述keys4就是初始读秘钥0x00;

技术总结

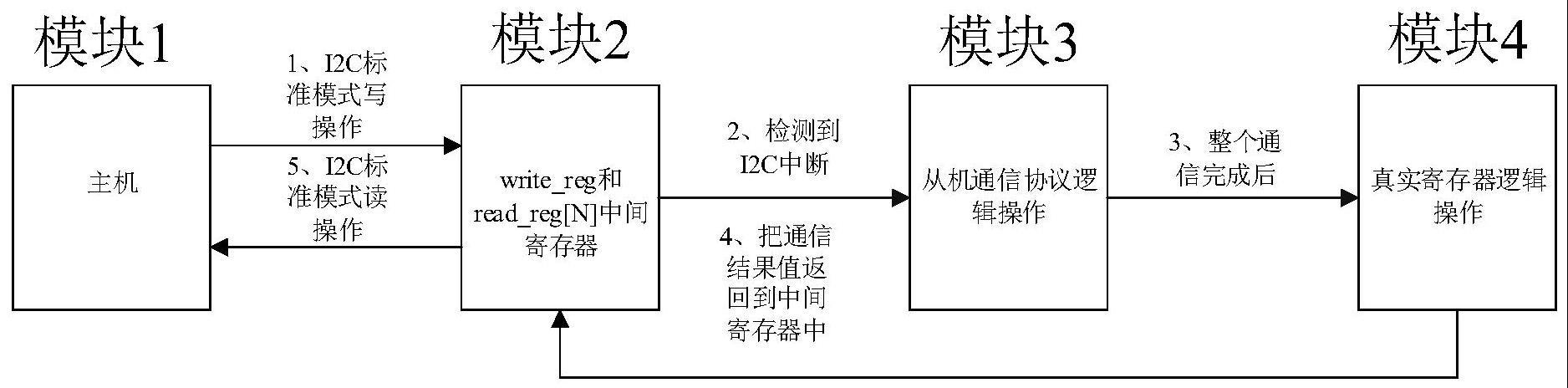

本申请提供了一种主机与从机之间的通信系统和通信方法;该系统有三根线:SCK、SDA、INT;主机和从机的逻辑电平的绝对值误差小于预设阈值时,三根线直连;主机和从机的逻辑电平的绝对值误差大于预设阈值时,通过两个NMOS管来转换通信电平,实现可靠通信;主机通过对从机内部的中间寄存器write_reg和read_reg[N]与从机数据交互,从机通过检测主机对其有操作的发生,在从机内部进行协议逻辑处理,操作从机所有的真实寄存器,把结果返回给中间寄存器read_reg[N],主机再通过读取相应数据,完成一整个通信流程,在整个主机和从机通信过程中,有自校验、加密功能、超时功能、唤醒功能。

技术研发人员:卓明锋

受保护的技术使用者:深圳英集芯科技股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!