纠错码电路和包括纠错码电路的半导体装置的制作方法

本公开涉及一种半导体电路,具体地涉及纠错码电路和包括该纠错码电路的半导体装置。

背景技术:

1、在半导体装置(例如,半导体存储装置)中,与多种操作相关的规范所需的时间由于操作速度的增加而减少,导致误码率增加。因此,半导体装置具有纠错码(ecc)功能,用于校正比特位错误并且向外部提供错误信息。

技术实现思路

1、根据本公开的实施例的一种纠错码电路可以包括:错误信息处理电路,其被配置成根据校正子信息生成错误信息;以及数据校正电路,其被配置成根据校正子信息校正数据中的错误。在测试模式下,仅错误信息处理电路和数据校正电路之中的错误信息处理电路可以被配置成被激活。

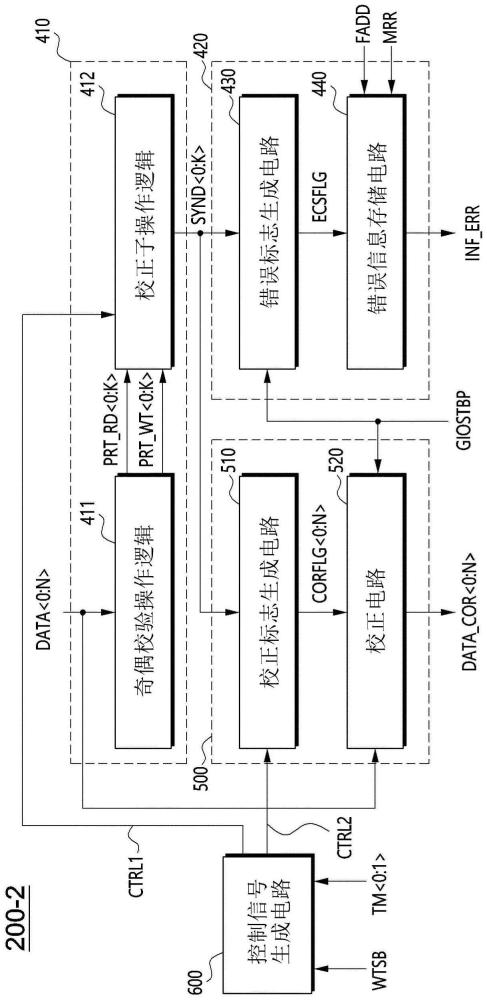

2、根据本公开的实施例的一种纠错码电路可以包括:纠错码引擎,其被配置成通过响应于第一控制信号对数据执行操作来生成校正子信息;错误信息处理电路,其被配置成根据校正子信息生成错误信息;数据校正电路,其被配置成响应于第二控制信号根据校正子信息校正数据中的错误;以及控制信号生成电路,其被配置成响应于写入/读取状态信号和一个或更多个测试模式信号而生成第一控制信号和第二控制信号。

3、根据本公开的实施例的一种半导体装置可以包括:存储区域;数据输入/输出电路,与存储区域连接并且被配置成与外部系统和存储区域中的一个交换数据;以及纠错码电路,连接到数据输入/输出电路并且被配置成执行错误信息处理操作以及数据校正操作,错误信息处理操作用于根据数据生成校正子信息并且通过使用校正子信息生成关于数据中包括的错误的信息,以及数据校正操作用于校正数据中的错误。纠错码电路可以被配置成在测试模式下仅执行错误信息处理操作和数据校正操作之中的错误信息处理操作。

技术特征:

1.一种纠错码电路,包括:

2.根据权利要求1所述的纠错码电路,其中,在所述测试模式下的读取操作期间,仅所述错误信息处理电路和所述数据校正电路之中的所述错误信息处理电路被激活。

3.根据权利要求1所述的纠错码电路,其中,所述数据校正电路在正常模式下的读取操作期间被激活。

4.根据权利要求3所述的纠错码电路,其中,所述数据校正电路在所述测试模式下的写入操作期间被禁止,以及在所述测试模式下的读取操作期间被禁止。

5.根据权利要求1所述的纠错码电路,其中,所述错误信息处理电路包括:

6.根据权利要求1所述的纠错码电路,其中,所述数据校正电路包括:

7.根据权利要求1所述的纠错码电路,还包括:

8.一种纠错码电路,包括:

9.根据权利要求8所述的纠错码电路,其中,所述纠错码引擎包括:

10.根据权利要求8所述的纠错码电路,其中,所述错误信息处理电路包括:

11.根据权利要求8所述的纠错码电路,其中,所述数据校正电路包括:

12.根据权利要求8所述的纠错码电路,其中,当第一控制模式通过所述一个或更多个测试模式信号中的任何一个被设置时,所述控制信号生成电路仅在正常模式下的读取操作期间和在测试模式下的读取操作期间激活所述第一控制信号,以及仅在所述正常模式下的读取操作期间激活所述第二控制信号。

13.根据权利要求12所述的纠错码电路,其中,当第二控制模式通过所述一个或更多个测试模式信号中的任何一个被设置时,所述控制信号生成电路仅在所述正常模式下的读取操作和写入操作期间激活所述第一控制信号,以及在所述测试模式下禁止所述第一控制信号。

14.一种半导体装置,包括:

15.根据权利要求14所述的半导体装置,其中,所述纠错码电路仅在正常模式下的读取操作期间执行所述数据校正操作。

16.根据权利要求14所述的半导体装置,其中,所述纠错码电路包括:

17.根据权利要求16所述的半导体装置,其中,所述纠错码引擎包括:

18.根据权利要求16所述的半导体装置,其中,所述错误信息处理电路包括:

19.根据权利要求16所述的半导体装置,其中,所述数据校正电路包括:

20.根据权利要求16所述的半导体装置,其中,当第一控制模式通过所述一个或更多个测试模式信号中的任何一个被设置时,所述控制信号生成电路仅在正常模式下的读取操作期间和在测试模式下的读取操作期间激活所述第一控制信号,以及仅在所述正常模式下的读取操作期间激活所述第二控制信号。

21.根据权利要求20所述的半导体装置,其中,当第二控制模式通过所述一个或更多个测试模式信号中的任何一个被设置时,所述控制信号生成电路仅在所述正常模式下的读取操作和写入操作期间激活所述第一控制信号,以及在所述测试模式下禁止所述第一控制信号。

技术总结

本公开涉及纠错码电路和半导体装置。实施例包括:错误信息处理电路,其被配置成根据校正子信息生成错误信息;以及数据校正电路,其被配置成根据校正子信息校正数据中的错误。在测试模式下,仅错误信息处理电路和数据校正电路之中的错误信息处理电路被配置成被激活。

技术研发人员:文弘基

受保护的技术使用者:爱思开海力士有限公司

技术研发日:

技术公布日:2024/3/5

- 还没有人留言评论。精彩留言会获得点赞!