一种基于FPGA实现频偏跟踪的方法与流程

本发明涉及卫星通信信号处理,具体的说,是一种基于fpga实现频偏跟踪的方法。

背景技术:

1、在卫星通信系统中,信号处理部分通常通过现场可编程门阵列fpga去实现各种功能,由于各种外部环境及硬件系统引入频率偏移,并且随着外部环境和时间的不断变化,所引入的频率偏移也随之变化,迫切需要一种能够实现基于fpga频偏跟踪的方法。

技术实现思路

1、本发明的目的在于提供一种基于fpga实现频偏跟踪的方法,能够对外部环境及通信系统引入的频率偏移进行快速、实时跟踪,以便于后续系统模块进行实时修正。

2、本发明通过下述技术方案解决上述问题:

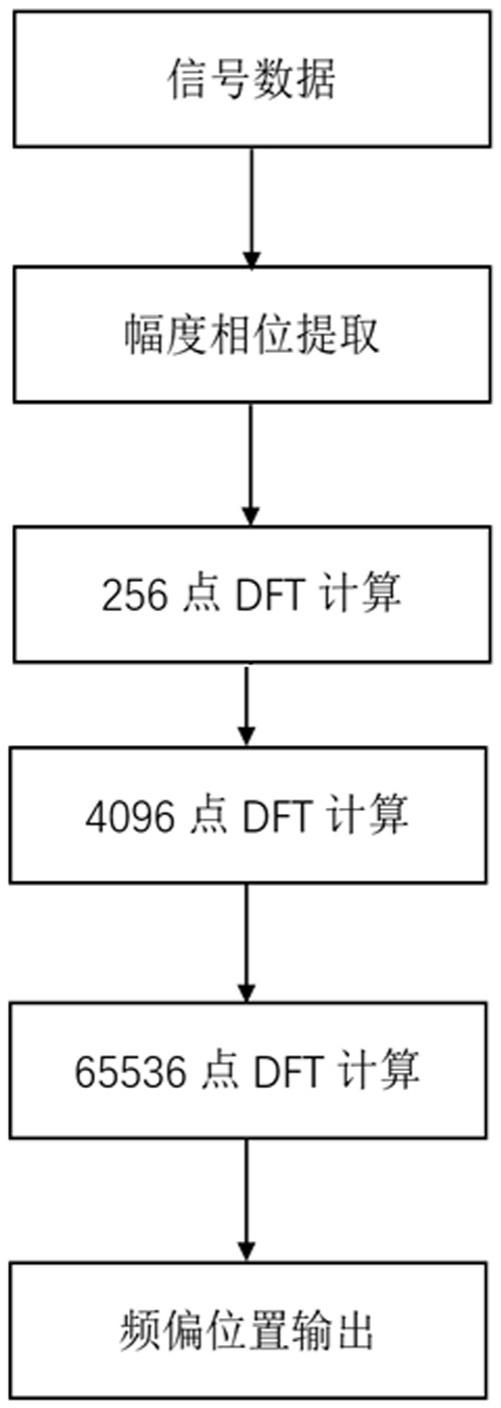

3、一种基于fpga实现频偏跟踪的方法,包括:

4、步骤s100、将接收的同向正交iq数据解析出相位数据和幅度数据;

5、步骤s200、将相位数据存入1024深度随机存储器ram,每1024个幅度数据求和并判断求和结果是否大于输出门限值,若大于,则输出该1024个幅度数据对应的1024个相位数据至65536深度ram,否则,删除该1024个幅度数据对应的1024个相位数据;

6、步骤s300、当65536深度ram中存满时,执行:

7、步骤s310、从65536深度ram中取出前256个相位数据,用于计算256个点的离散傅里叶变换dft,以第k1=0的dft点为中心,计算该dft点附近±m1个点的幅度值,k1∈{0~255},找到这些点的最大幅度值对应的k1值,将k1乘以16得到第二级dft计算的初始位置;

8、步骤s320、从65536深度ram中取出前4096个相位数据,接收第二级dft计算的初始位置,计算其附近±m1个点的幅度值,找到这些点的最大幅度值对应的k2值,k2∈{0~4095},即为第二频偏,将k2乘以16得到第三级dft计算的初始位置;

9、步骤s330、从65536深度ram中取出65536个相位数据,接收所述第三级dft计算的初始位置,计算其附近±m1个点的幅度值,找到这些点的最大幅度值对应的k3值,即为相对于65536个相位数据的频偏位置,k3∈{0~65535}。

10、本发明通过逐级查找的方式以极少量的计算量快速计算出频率偏移,提高了计算速度,并节约更多fpga资源,同时达到实时跟踪频偏的效果。

11、所述步骤s100具体包括:例化坐标旋转数字计算器cordic ip核,输入32比特bit的iq数据,输出16bit幅度值和16bit相位,相位为-1到1的值,其中高1bit为符号位,中2bit为整数位,低13bit为小数位。

12、所述随机存储器ram宽度为16bit。

13、所述步骤s310中计算幅度值的方法包括:

14、步骤a、分别例化存储余弦cos数值和正弦sin数值的只读存储器rom,将cos(0~2π)和sin(0~2π)的值分别乘以1024并存入各自rom;

15、步骤b、利用相位计算n个点m阶dft,化简dft计算公式:

16、 (1)

17、 (2)

18、由式(1)(2)得到:

19、 (3)

20、m阶dft:

21、 (4)

22、化简后得到:

23、 (5)

24、其中:表示dft变换的第个点,∈{0~n-1};n为dft点个数;为幅度;m为阶数;为相角;为输入的第个iq数据;为第个相角;为虚部;

25、步骤c、由公式(5)可知,通过幅度和相位能够算出m阶频谱,的值作为rom的读地址,读出余弦cos和正弦sin的rom表中的值分别累加计算,然后分别平方后相加得到第k个点的dft的幅度值。

26、所述m1=8或m1=16。

27、本发明与现有技术相比,具有以下优点及有益效果:

28、本发明通过分3级逐级查找的方式以少量的计算量快速计算出频率偏移,提高了计算速度,并节约更多fpga资源,同时达到实时跟踪频偏的效果。

技术特征:

1.一种基于fpga实现频偏跟踪的方法,其特征在于,包括:

2.根据权利要求1所述的一种基于fpga实现频偏跟踪的方法,其特征在于,包括:所述步骤s100具体包括:例化坐标旋转数字计算器cordic ip核,输入32比特bit的iq数据,输出16bit幅度值和16bit相位,相位为-1到1的值,其中高1bit为符号位,中2bit为整数位,低13bit为小数位。

3.根据权利要求2所述的一种基于fpga实现频偏跟踪的方法,其特征在于,所述随机存储器ram宽度为16bit。

4.根据权利要求1-3中任意一项所述的一种基于fpga实现频偏跟踪的方法,其特征在于,所述步骤s310中计算幅度值的方法包括:

5.根据权利要求1-3中任意一项所述的一种基于fpga实现频偏跟踪的方法,其特征在于,所述m1=8或m1=16。

技术总结

本发明公开了一种基于FPGA实现频偏跟踪的方法,涉及卫星通信信号处理技术领域,将接收IQ数据解析出相位和幅度;将相位存入1024 RAM,利用幅度进行TDMA信号提取和过滤后,从RAM读出相位存入65536深度RAM,存满时,先计算前256点中心位置±8的DFT,找到尖峰位置,将该偏移位置乘以16给到下一级计算4096点中心位置±8的DFT,找到尖峰位置,将该偏移位置乘以16给到下一级计算65536点中心位置±8的DFT,找到频率偏移。本发明通过分3级逐级查找的方式以少量的计算量快速计算出频率偏移,提高了计算速度,并节约更多FPGA资源,同时达到实时跟踪频偏的效果。

技术研发人员:龚珊,汪峰,于合龙,宗明,黄增泽

受保护的技术使用者:成都戎星科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!