DMA数据传输系统的制作方法

本公开涉及数据处理,尤其涉及一种dma数据传输系统。

背景技术:

1、fpga(field programmable gate array,可编程阵列逻辑器件)与pc机交互时,有时候需要将fpga中的数据传输到pc机供pc机调用。数据传输时一般会采用dma模块或sgdma模块。通过dma模块或sgdma模块进行数据传输时,一般需要fpga与pc机频繁通信,读取存储在pc机的数据链表中的物理地址,进行数据传输。这会降低fpga向pc机的数据传输效率。

技术实现思路

1、有鉴于此,本公开实施例期望提供一种dma数据传输系统。

2、本公开的技术方案是这样实现的:

3、本公开提供一种dma数据传输系统。

4、本公开实施例提供的dma数据传输系统,包括:

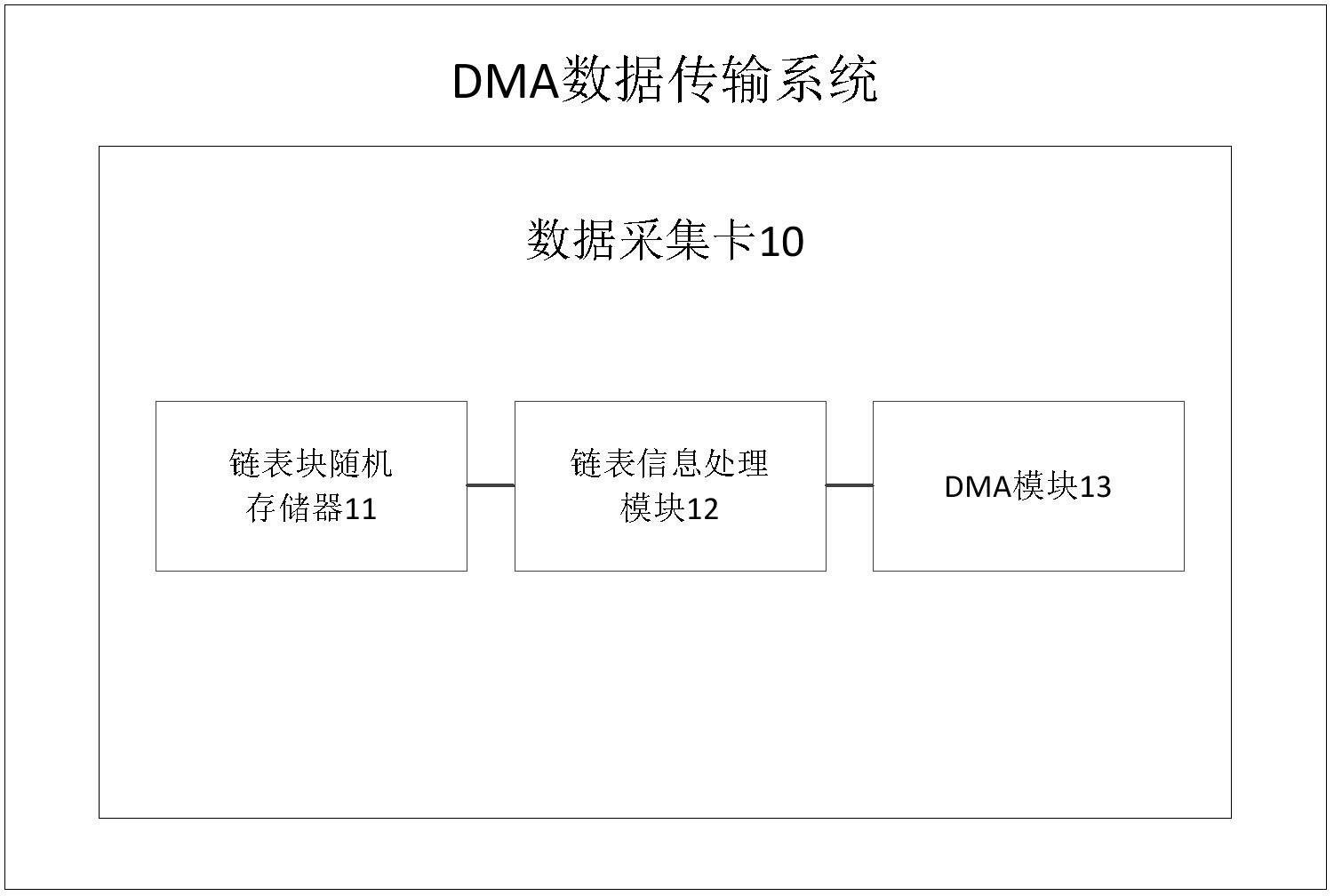

5、dma数据传输系统,其特征在于,包括基于fpga芯片开发的且用于向上位机环形内存缓冲区传输数据的数据采集卡,所述数据采集卡包括链表块随机存储器、链表信息处理模块和dma模块;

6、所述链表块随机存储器中存储有用于描述所述上位机环形内存缓冲区的dma设备描述符,所述dma设备描述符为n个,2≤n≤50,且每个所述dma设备描述符均包括一段物理上连续的内存空间的起始物理地址及存储空间大小,n个所述dma设备描述符所记录的存储空间大小之和等于所述上位机环形内存缓冲区的存储空间大小;

7、所述链表信息处理模块用于对n个所述dma设备描述符进行排序,且依次循环往复获取所述dma设备描述符并发送给所述dma模块;

8、所述dma模块用于依据接收的所述dma设备描述符向所述上位机环形内存缓冲区传输数据,每次传输的数据可写满一个所述dma设备描述符所对应的所述上位机环形内存缓冲区的存储空间之后,再接收所述链表信息处理模块发送的下一个所述dma设备描述符,并依据下一个所述dma设备描述符继续传输数据。

9、在一些实施例中,所述上位机环形内存缓冲区的申请方法为:

10、以存储空间大小的目标值申请物理地址连续的内存空间,其中,所述目标值的初始值为预设值,所述目标值小于所述上位机环形内存缓冲区的存储空间大小;

11、当申请失败后,更新所述目标值,并返回所述以存储空间大小的目标值申请物理地址连续的内存空间的步骤,其中,更新后的目标值小于更新前的目标值;

12、当申请成功后,获取申请到的内存空间的物理地址,并判断累积申请到的存储空间大小是否达到所述上位机环形内存缓冲区的存储空间大小;

13、若是,则确定申请完成;

14、若否,则返回所述以存储空间大小的目标值申请物理地址连续的内存空间的步骤。

15、在一些实施例中,所述更新所述目标值,包括:

16、计算所述目标值的半值;

17、将所述半值作为更新后的目标值。

18、在一些实施例中,在计算所述目标值的半值之后,所述方法还包括:

19、计算所述上位机环形内存缓冲区的存储空间大小与所述累积申请到的存储空间大小之间的差值,并判断所述差值是否小于所述半值;

20、若是,则将所述差值作为更新后的目标值;

21、若否,则执行所述将所述半值作为更新后的目标值的步骤。

22、在一些实施例中,所述数据采集卡还包括用于打包数据并向所述上位机环形内存缓冲区传输的数据接口模块。

23、在一些实施例中,所述数据接口模块为提供标准axi总线用户数据接口的axibridge pcie ip核,所述axi bridge pcie ip核使用axi slave接口接收所述dma模块传输的数据,打包数据为tlp数据包。

24、在一些实施例中,所述数据采集卡还包括用于通过所述数据接口模块接收指令、反馈状态,且用于对所述链表块随机存储器进行读写的寄存器读写模块。

25、在一些实施例中,所述寄存器读写模块为axi bram ctrl ip核,且所述axibridge pcie ip核使用axi master接口连接所述axi bram ctrl ip核。

26、在一些实施例中,数据采集卡还包括用于向所述dma模块提供原始数据的数据缓冲存储模块,所述数据缓冲存储模块包括缓冲存储控制单元和数据缓冲存储器,所述数据缓冲存储器为同步动态随机存取存储器。

27、在一些实施例中,所述dma模块包括用于向所述上位机环形内存缓冲区传输数据的dma数据搬运单元、用于接收原始数据并提供给所述dma数据搬运单元的先进先出写入存储器、用于依据接收的所述dma设备描述符控制所述dma数据搬运单元的dma搬运控制单元、用于获取所述dma搬运控制单元状态信息的dma状态监视单元。

28、在一些实施例中,所述dma模块包括用于接收所述dma数据搬运单元传输的数据的先进先出读出存储器,所述dma数据搬运单元还用于接收所述上位机环形内存缓冲区传输的数据。

29、根据本公开实施例的dma数据传输系统包括基于fpga芯片开发的且用于向上位机环形内存缓冲区传输数据的数据采集卡,数据采集卡包括链表块随机存储器、链表信息处理模块和dma模块;链表块随机存储器中存储有用于描述上位机环形内存缓冲区的dma设备描述符,dma设备描述符为n个,2≤n≤50,且每个dma设备描述符均包括一段物理上连续的内存空间的起始物理地址及存储空间大小,n个dma设备描述符所记录的存储空间大小之和等于上位机环形内存缓冲区的存储空间大小;链表信息处理模块用于对n个dma设备描述符进行排序,且依次循环往复获取dma设备描述符并发送给dma模块;dma模块用于依据接收的dma设备描述符向上位机环形内存缓冲区传输数据,每次传输的数据可写满一个dma设备描述符所对应的上位机环形内存缓冲区的存储空间之后,再接收链表信息处理模块发送的下一个dma设备描述符,并依据下一个dma设备描述符继续传输数据。本申请中链表块随机存储器集成于fpga中,存储有描述上位机环形内存缓冲区的dma设备描述符。fpga向pc机进行数据传输时可直接读取在fpga数据采集卡内的链表块随机存储器存储的dma设备描述符,根据dma设备描述符中的物理地址向pc 机发送存储数据。这个数据传输过程中不需要fpga再与pc机进行频繁通信,来获取物理地址,从而有利于提高数据传输效率。

30、本公开附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本公开的实践了解到。

技术特征:

1.一种dma数据传输系统,其特征在于,包括基于fpga芯片开发的且用于向上位机环形内存缓冲区传输数据的数据采集卡,所述数据采集卡包括链表块随机存储器、链表信息处理模块和dma模块;

2.根据权利要求1所述的dma数据传输系统,其特征在于,所述上位机环形内存缓冲区的申请方法为:

3.根据权利要求2所述的dma数据传输系统,其特征在于,所述更新所述目标值,包括:

4.根据权利要求3所述的dma数据传输系统,其特征在于,在计算所述目标值的半值之后,所述方法还包括:

5.根据权利要求1所述的dma数据传输系统,其特征在于,所述数据采集卡还包括用于打包数据并向所述上位机环形内存缓冲区传输的数据接口模块。

6.根据权利要求5所述的dma数据传输系统,其特征在于,所述数据接口模块为提供标准axi总线用户数据接口的axi bridge pcie ip核,所述axi bridge pcie ip核使用axislave接口接收所述dma模块传输的数据,打包数据为tlp数据包。

7.根据权利要求6所述的dma数据传输系统,其特征在于,所述数据采集卡还包括用于通过所述数据接口模块接收指令、反馈状态,且用于对所述链表块随机存储器进行读写的寄存器读写模块。

8.根据权利要求7所述的dma数据传输系统,其特征在于,所述寄存器读写模块为axibram ctrl ip核,且所述axi bridge pcie ip核使用axi master接口连接所述axi bramctrl ip核。

9.根据权利要求1所述的dma数据传输系统,其特征在于,数据采集卡还包括用于向所述dma模块提供原始数据的数据缓冲存储模块,所述数据缓冲存储模块包括缓冲存储控制单元和数据缓冲存储器,所述数据缓冲存储器为同步动态随机存取存储器。

10.根据权利要求9所述的dma数据传输系统,其特征在于,所述dma模块包括用于向所述上位机环形内存缓冲区传输数据的dma数据搬运单元、用于接收原始数据并提供给所述dma数据搬运单元的先进先出写入存储器、用于依据接收的所述dma设备描述符控制所述dma数据搬运单元的dma搬运控制单元、用于获取所述dma搬运控制单元状态信息的dma状态监视单元。

11.根据权利要求10所述的dma数据传输系统,其特征在于,所述dma模块包括用于接收所述dma数据搬运单元传输的数据的先进先出读出存储器,所述dma数据搬运单元还用于接收所述上位机环形内存缓冲区传输的数据。

技术总结

本公开是关于一种DMA数据传输系统。该DMA数据传输系统包括基于FPGA芯片开发的且用于向上位机环形内存缓冲区传输数据的数据采集卡,数据采集卡包括链表块随机存储器、链表信息处理模块和DMA模块;链表块随机存储器中存储有用于描述上位机环形内存缓冲区的DMA设备描述符,DMA设备描述符为n个且每个DMA设备描述符均包括一段物理上连续的内存空间的起始物理地址及存储空间大小。本申请FPGA向PC机进行数据传输时可直接读取在FPGA数据采集卡内的链表块随机存储器存储的DMA设备描述符,根据DMA设备描述符中的物理地址向PC机发送存储数据。这个数据传输过程中不需要FPGA再与PC机进行频繁通信,来获取物理地址,从而有利于提高数据传输效率。

技术研发人员:李峰,魏云清,黄斌,吴亚,贺羽

受保护的技术使用者:国仪量子(合肥)技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!