时序验证的方法、装置及存储介质与流程

本申请实施例涉及电子设计自动化,尤其涉及一种时序验证的方法、装置及存储介质。

背景技术:

1、在芯片数字后端实现过程中,通常先采用不同公司的eda(electronic designautomation,电子设计自动化)工具分别进行布局布线和静态时序分析,但是两者的时序验证结果一致性较差。

2、如果布局布线工具的时序验证结果比静态时序分析工具的好很多,那么会导致布局布线工具欠修正并使得静态时序分析阶段遗留大量违规路径。如果布局布线工具的时序验证结果比静态时序分析工具的差很多,那么会导致布局布线工具过修正从而影响了功耗等性能指标。

3、因此,后端不同设计工具的时序验证结果不一致是芯片数字后端实现过程中不可忽视的问题。

技术实现思路

1、本申请实施例提供了一种时序验证的方法,包括:

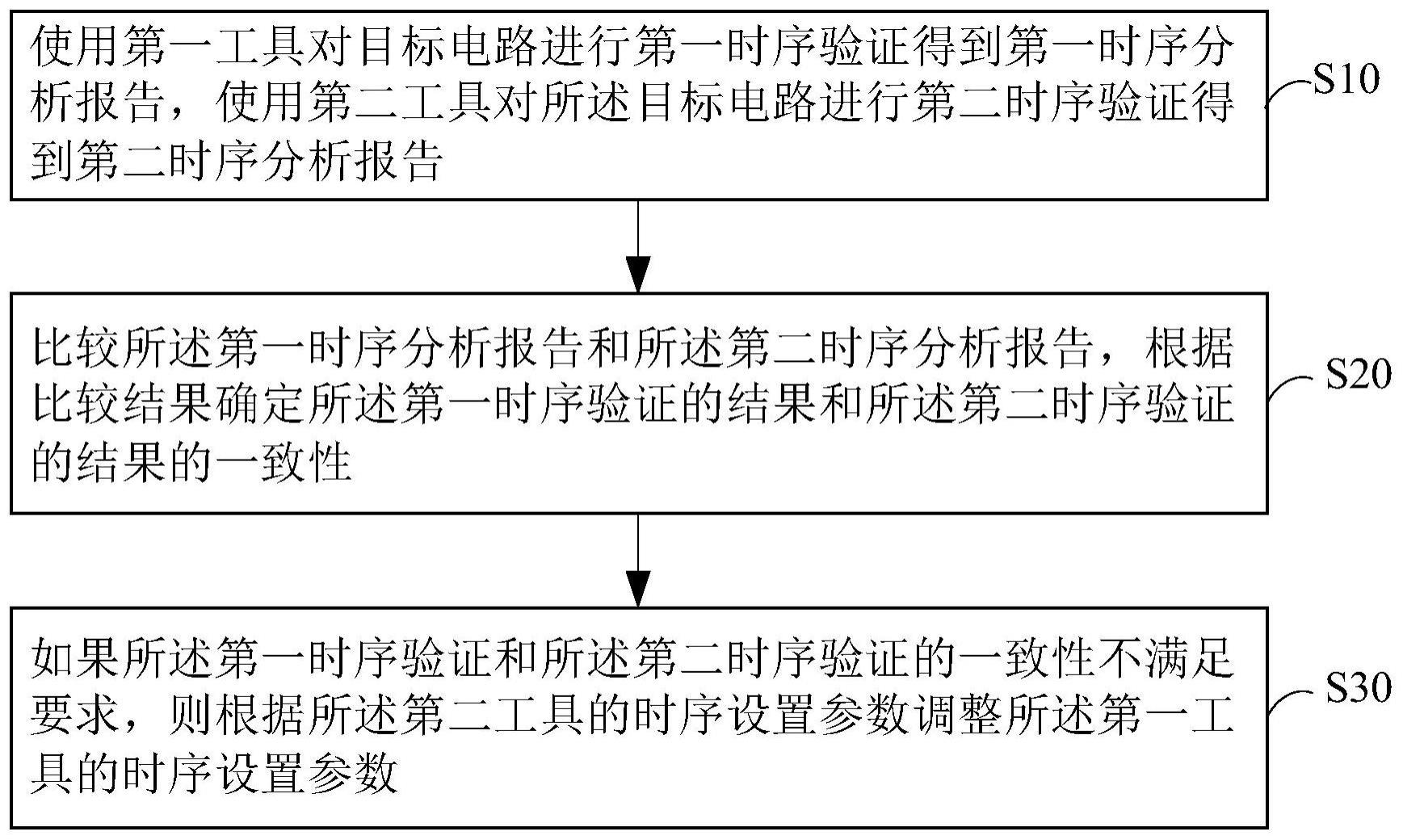

2、使用第一工具对目标电路进行第一时序验证得到第一时序分析报告,使用第二工具对所述目标电路进行第二时序验证得到第二时序分析报告;

3、比较所述第一时序分析报告和所述第二时序分析报告,根据比较结果确定所述第一时序验证的结果和所述第二时序验证的结果的一致性;

4、如果所述第一时序验证的结果和所述第二时序验证的结果的一致性不满足要求,则根据所述第二工具的时序设置参数调整所述第一工具的时序设置参数;

5、其中,所述第一工具为电子设计自动化布局布线工具,所述第二工具为电子设计自动化静态时序分析工具。

6、本申请实施例提供了一种时序验证的装置,包括:存储器及处理器,所述存储器存储有计算机程序,所述计算机程序被所述处理器执行时实现上述时序验证的方法的步骤。

7、本申请实施例提供了一种计算机可读存储介质,存储有计算机程序,所述计算机程序被处理器执行时实现上述时序验证的方法的步骤。

8、本申请实施例提供的时序验证的方法、装置及存储介质,使用第一工具对目标电路进行第一时序验证得到第一时序分析报告,使用第二工具对所述目标电路进行第二时序验证得到第二时序分析报告;比较所述第一时序分析报告和所述第二时序分析报告,根据比较结果确定所述第一时序验证的结果和所述第二时序验证的结果的一致性;如果所述第一时序验证的结果和所述第二时序验证的结果的一致性不满足要求,则根据所述第二工具的时序设置参数调整所述第一工具的时序设置参数。上述时序验证的方法能够提高芯片数字后端实现时不同eda工具的时序验证一致性。

9、在阅读并理解了附图和详细描述后,可以明白其他方面。

技术特征:

1.一种时序验证的方法,包括:

2.如权利要求1所述的方法,其特征在于:

3.如权利要求1所述的方法,其特征在于:

4.如权利要求1所述的方法,其特征在于:

5.如权利要求1所述的方法,其特征在于:

6.如权利要求1所述的方法,其特征在于:

7.如权利要求6所述的方法,其特征在于:

8.如权利要求1所述的方法,其特征在于:

9.一种时序验证的装置,包括:存储器及处理器,所述存储器存储有计算机程序,所述计算机程序被所述处理器执行时实现上述权利要求1-8中任一项所述的时序验证的方法的步骤。

10.一种计算机可读存储介质,存储有计算机程序,所述计算机程序被处理器执行时实现上述权利要求1-8中任一项所述的时序验证的方法的步骤。

技术总结

本文公开一种时序验证的方法、装置及存储介质。所述方法包括:使用第一工具对目标电路进行第一时序验证得到第一时序分析报告,使用第二工具对目标电路进行第二时序验证得到第二时序分析报告;比较所述第一时序分析报告和所述第二时序分析报告,根据比较结果确定所述第一时序验证的结果和所述第二时序验证的结果的一致性;如果一致性不满足要求,则根据第二工具的时序设置参数调整第一工具的时序设置参数;其中,第一工具为电子设计自动化软件的布局布线工具,第二工具为静态时序分析工具。本文的方案能够提高芯片数字后端实现时不同EDA工具的时序验证一致性。

技术研发人员:江浩源,陈玺洋,何瑞洲

受保护的技术使用者:声龙(新加坡)私人有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!