使用受害者高速缓存的行锤击缓解的制作方法

本公开大体上涉及半导体存储器及方法,并且更具体来说,涉及用于使用受害者高速缓存的行锤击缓解的设备、系统及方法。

背景技术:

1、存储器装置通常被提供为计算机或其它电子系统中的内部、半导体、集成电路。存在许多不同类型的存储器,包含易失性及非易失性存储器。易失性存储器可能需要电力来维持其数据(例如主机数据、错误数据等),并且包含随机存取存储器(ram)、动态随机存取存储器(dram)、静态随机存取存储器(sram)、同步动态随机存取存储器(sdram)及晶闸管随机存取存储器(tram)等等。非易失性存储器可通过在未供电时保持所存储数据来提供持久数据,并且可包含nand快闪存储器、nor快闪存储器、铁电随机存取存储器(feram)及电阻可变存储器,例如相变随机存取存储器(pcram)、电阻式随机存取存储器(rram)及磁阻式随机存取存储器(mram),例如自旋力矩转移随机存取存储器(stt ram)等。

2、存储器装置可耦合到主机(例如,主机计算装置)以存储数据、命令及/或指令以在操作计算机或电子系统时供主机使用。举例来说,数据、命令及/或指令可在计算或其它电子系统的操作期间在主机与存储器装置之间传送。控制器可用于管理主机与存储器装置之间的数据、命令及/或指令的传递。

技术实现思路

1、本公开的一个方面提供一种用于行锤击缓解的方法,其中所述方法包括:将数据写入到第一高速缓存的高速缓存行;及将最近最少使用的高速缓存行从所述第一高速缓存写入到第二高速缓存的高速缓存行,其中执行将所述最近最少使用的高速缓存行从所述第一高速缓存写入到所述第二高速缓存,作为行锤击缓解操作的一部分。

2、本公开的另一方面提供一种用于行锤击缓解的设备,其中所述设备包括:控制器;第一高速缓存,其耦合到所述控制器,所述第一高速缓存经配置以根据最近最少使用(lru)方案操作;第二高速缓存,其耦合到所述控制器,所述第二高速缓存经配置以根据lru方案操作;及存储器装置,其经由至少一个存储器信道耦合到所述第一高速缓存或所述第二高速缓存,其中所述控制器经配置以:控制将数据写入到所述第一高速缓存的高速缓存行;及控制将所述第一高速缓存的最近最少使用的高速缓存行写入到所述第二高速缓存,作为行锤击缓解操作的一部分。

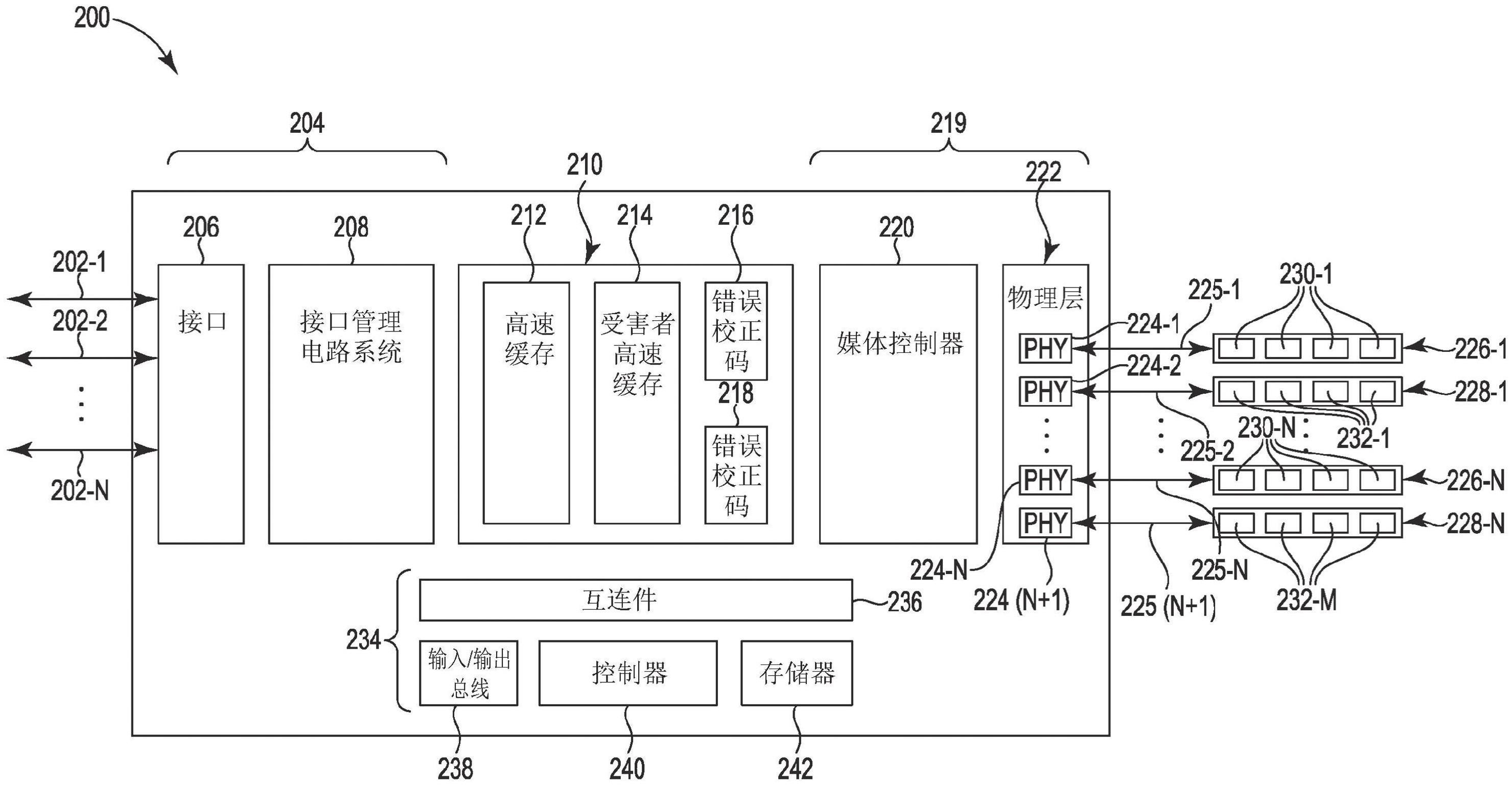

3、本公开的另一方面提供一种用于行锤击缓解的系统,其中所述系统包括:存储器控制器,其包括:中央控制器;第一高速缓存,其包括驻存于所述中央控制器上的第一数量的高速缓存行;第二高速缓存,其包括驻存于所述中央控制器上的第二数量的高速缓存行;及存储器装置,其耦合到所述存储器控制器,其中所述存储器控制器经配置以:使数据根据计算高速链路(cxl)协议写入到所述第一高速缓存;及使所述第一高速缓存的最近最少使用的高速缓存行写入到所述第二高速缓存,作为行锤击缓解操作的一部分。

技术特征:

1.一种用于行锤击缓解的方法,其包括:

2.根据权利要求1所述的方法,其中:

3.根据权利要求1所述的方法,其进一步包括将所述第二高速缓存的时延与将所述第一高速缓存或所述第二高速缓存或两者耦合到存储器装置的信道的时延匹配。

4.根据权利要求1所述的方法,其中所述第一高速缓存及所述第二高速缓存各自根据最近最少使用lru高速缓存策略操作。

5.根据权利要求1至4中任一项所述的方法,其进一步包括:

6.根据权利要求1至4中任一项所述的方法,其中所述第一高速缓存包括比所述第二高速缓存更多数量的高速缓存行。

7.一种用于行锤击缓解的设备,其包括:

8.根据权利要求7所述的设备,其中所述控制器包括存储器控制器的中央控制器部分(110;210),其经配置以根据计算高速链路协议操作,并且其中所述第一高速缓存及所述第二高速缓存驻存于所述存储器控制器的所述中央控制器部分上。

9.根据权利要求7所述的设备,其中所述控制器进一步经配置以将所述第二高速缓存的时延与将所述第一高速缓存或所述第二高速缓存或两者耦合到所述存储器装置的所述至少一个存储器信道的时延匹配。

10.根据权利要求7所述的设备,其中所述控制器进一步经配置以:

11.根据权利要求7至10中任一项所述的设备,其中所述第一高速缓存物理上不同于所述第二高速缓存。

12.一种用于行锤击缓解的系统,其包括:

13.根据权利要求12所述的系统,其中所述存储器控制器经配置以将所述第二高速缓存的时延与将所述存储器控制器耦合到所述存储器装置的存储器信道的时延匹配。

14.根据权利要求12所述的系统,其中所述存储器控制器经配置以利用指令级并行度方案,以使所述数据写入到所述第一高速缓存。

15.根据权利要求12至14中任一项所述的系统,其中所述存储器控制器经配置以使所述数据以至少每秒32千兆的速率写入到所述第一高速缓存。

技术总结

本申请涉及使用受害者高速缓存的行锤击缓解。行锤攻击利用存储器装置的非预期及不希望的副作用,其中存储器单元通过泄漏电荷在它们之间进行电相互作用,并且可能会改变原始存储器存取中未寻址的附近存储器行的内容。通过使用受害者高速缓存缓解行锤攻击。将数据写入到高速缓存的高速缓存行。将所述高速缓存的最近最少使用的高速缓存行写入到所述受害者高速缓存。

技术研发人员:A·D·艾卡尔,S·斯瓦米

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!