一种存内计算电路及控制方法与流程

本申请属于存内计算,尤其涉及一种存内计算电路及控制方法。

背景技术:

1、现有的存内计算单元中,存储器需要参与计算操作,因此,存储阵列基于不同运算形式进行相应改动,基于不同的计算方式可分为模拟域计算和数字域计算,模拟域计算利用电流、电荷累计等进行计算,在低精度计算应用场景得到广泛应用,而数字域计算相比于模拟域计算具备高精度和强鲁棒性。然而,现有的数字域计算中,运算器件的数量较多,占用电路面积较大,则容易造成存内计算电路的面积较大,且功耗较高。

技术实现思路

1、本申请实施例提供一种存内计算电路及控制方法,可以解决现有数字域存算电路中运算器件数量多,占用电路面积大以及功耗高的问题。

2、本申请实施例的第一方面,提供一种存内计算电路,该电路包括:

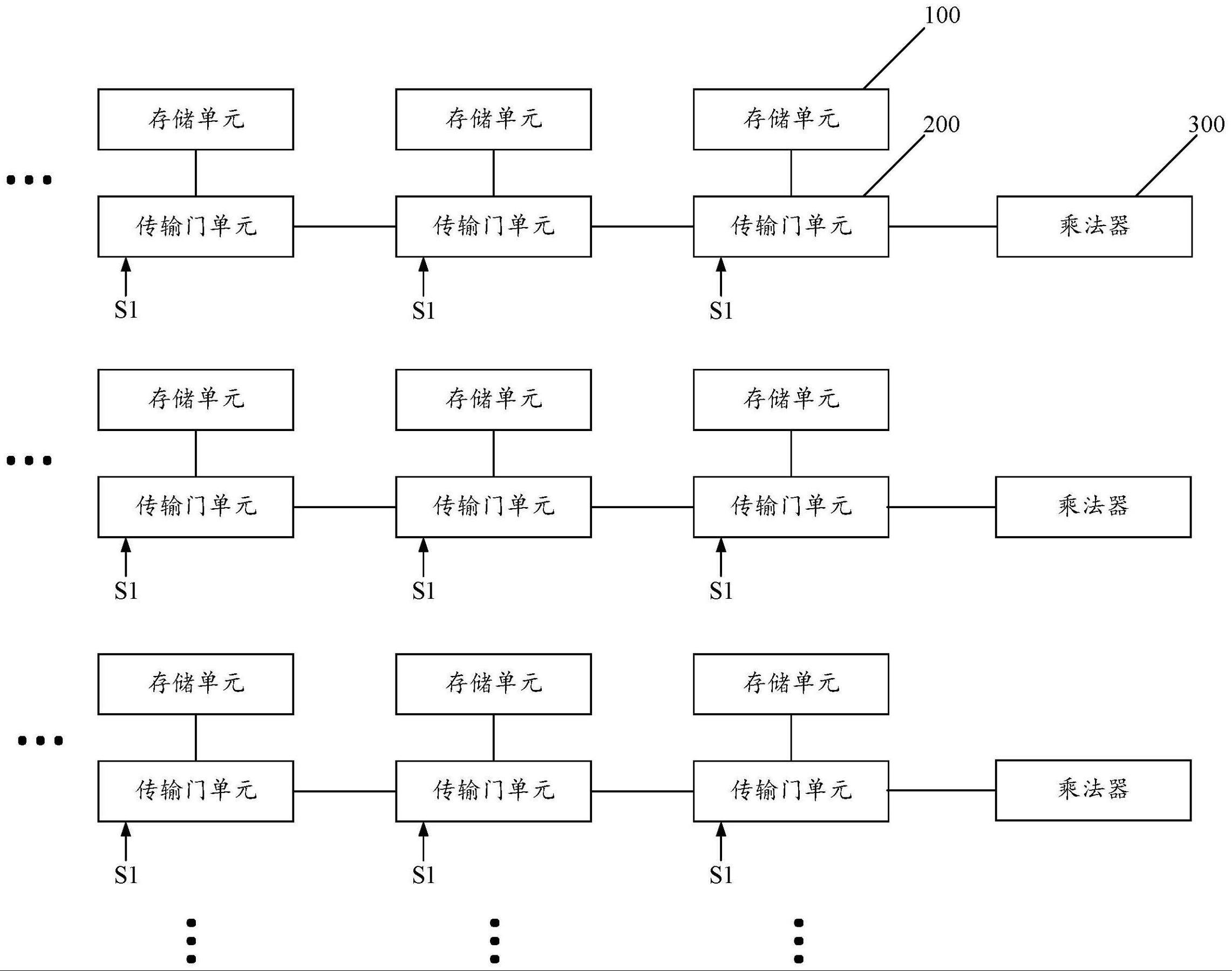

3、存储阵列,所述存储阵列包括多个存储单元;

4、传输门阵列,所述传输门阵列包括多个传输门单元,所述传输门单元与所述存储单元一对一电连接;

5、多个乘法器,每个所述乘法器与一行所述传输门单元电连接,或,每个所述乘法器与一列所述传输门单元电连接;

6、所述传输门单元用于基于筛选信号控制所述存储单元向所述乘法器输出存储数据。

7、在一些实施方式中,所述存内计算电路还包括:

8、加法器阵列,所述加法器阵列电连接于多个所述乘法器。

9、在一些实施方式中,所述存内计算电路还包括:

10、筛选控制模块,所述筛选控制模块用于生成所述筛选信号;

11、在所述乘法器与一行所述传输门单元电连接的情况下,所述筛选信号包括列筛选信号,所述列筛选信号用于控制对应的同一列所述传输门单元的导通或断开;

12、在所述乘法器与一列所述传输门单元电连接的情况下,所述筛选信号包括行筛选信号,所述行筛选信号用于控制对应的同一行所述传输门单元的导通或断开。

13、在一些实施方式中,

14、所述传输门单元包括晶体管,所述晶体管的栅极用于接收所述筛选信号。

15、在一些实施方式中,

16、所述晶体管包括至少两个并联的所述晶体管;

17、所述筛选信号用于控制所述晶体管的开关状态一致。

18、在一些实施方式中,

19、所述筛选控制模块包括反相器,所述筛选信号包括第一筛选信号和第二筛选信号,所述第二筛选信号是基于所述第一筛选信号通过所述反相器得到的;

20、所述晶体管包括n型晶体管和p型晶体管,所述第一筛选信号与所述第二筛选信号分别用于控制不同类型的所述晶体管。

21、在一些实施方式中,

22、所述筛选控制模块包括多个输出端口,所述输出端口用于输出所述筛选信号;

23、每个所述输出端口电连接于同一行或同一列所述传输门单元。

24、在一些实施方式中,

25、所述存储单元包括sram存储单元;

26、所述sram存储单元包括:

27、第一反相器,

28、第二反相器,所述第二反相器的输出端电连接于所述第一反相器的输入端以形成第一存储节点,所述第二反相器的输入端连接于所述第一反相器的输出端以形成第二存储节点;

29、所述传输门单元电连接于所述第一存储节点或所述第二存储节点中的一者。

30、在一些实施方式中,

31、所述乘法器包括同或门,所述同或门的第一输入端用于接收所述存储数据,所述同或门的第二输入端用于接收激励信号。

32、本申请实施例的第二方面,提供一种存内计算电路的控制方法,该方法包括:

33、根据计算指令,生成筛选信号;

34、基于所述筛选信号,控制传输门单元的导通状态;

35、基于导通的所述传输门单元,控制对应存储单元传输存储数据至对应连接的乘法器;

36、利用所述乘法器,对接收到的所述存储数据进行乘法运算。

37、综上,本申请实施例提供的一种存内计算电路,该电路包括:存储阵列,所述存储阵列包括多个存储单元;传输门阵列,所述传输门阵列包括多个传输门单元,所述传输门单元与所述存储单元一对一电连接;多个乘法器,每个所述乘法器与一行所述传输门单元电连接,或,每个所述乘法器与一列所述传输门单元电连接;所述传输门单元用于基于筛选信号控制所述存储单元向所述乘法器输出存储数据。通过对每个存储单元电连接一个传输门单元,传输门单元可以基于筛选信号控制与传输门单元电连接的存储单元中的存储数据输出至每一行或每一列的乘法器,从而每一行或每一列只需配置一个乘法器即可选取所需要的存储单元中的存储数据以完成二进制乘法计算,减少了乘法器数量,从而减少了存内计算电路的电子元器件,运行元器件的数量减少,从而减少了存内计算电路的面积,以及可以起到降低电路运行功耗的效果。

38、相应的,本申请实施例提供的存内计算电路的控制方法,也同样具有上述技术效果。

技术特征:

1.一种存内计算电路,其特征在于,包括:

2.根据权利要求1所述的存内计算电路,其特征在于,还包括:

3.根据权利要求1所述的存内计算电路,其特征在于,还包括:

4.根据权利要求3所述的存内计算电路,其特征在于,

5.根据权利要求4所述的存内计算电路,其特征在于,

6.根据权利要求5所述的存内计算电路,其特征在于,

7.根据权利要求3所述的存内计算电路,其特征在于,

8.根据权利要求1-7中任一项所述的存内计算电路,其特征在于,

9.根据权利要求1-7中任一项所述的存内计算电路,其特征在于,

10.一种存内算计算电路的控制方法,其特征在于,应用于如权利要求1-9中任一项所述的存内计算电路,所述控制方法包括:

技术总结

本申请公开一种存内计算电路及控制方法,涉及存内计算技术领域,其中,存内计算电路包括:存储阵列,所述存储阵列包括多个存储单元;传输门阵列,所述传输门阵列包括多个传输门单元,所述传输门单元与所述存储单元一对一电连接;多个乘法器,每个所述乘法器与一行所述传输门单元电连接,或,每个所述乘法器与一列所述传输门单元电连接;所述传输门单元用于基于筛选信号控制所述存储单元向所述乘法器输出存储数据。可以解决现有数字域存算电路中运算器件数量多,占用电路面积大的问题。

技术研发人员:乔树山,曹景楠,游恒,尚德龙,周玉梅

受保护的技术使用者:中科南京智能技术研究院

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!