缓存结构和电子设备的制作方法

本公开的实施例涉及一种缓存结构和电子设备。

背景技术:

1、处理器的工作速度远高于内存,如果处理器直接访问内存读写数据,则需要等待一定的时间周期,因此访问内存的过程中通常采用高速缓冲存储装置(cache)来提高系统效率以及处理器访问内存的速度。通常,处理器优先从cache中查找数据,例如,若应用程序或软件请求的数据在cache中存在,则称为缓存命中(cache hit),反之称为缓存未命中(cache miss)。

技术实现思路

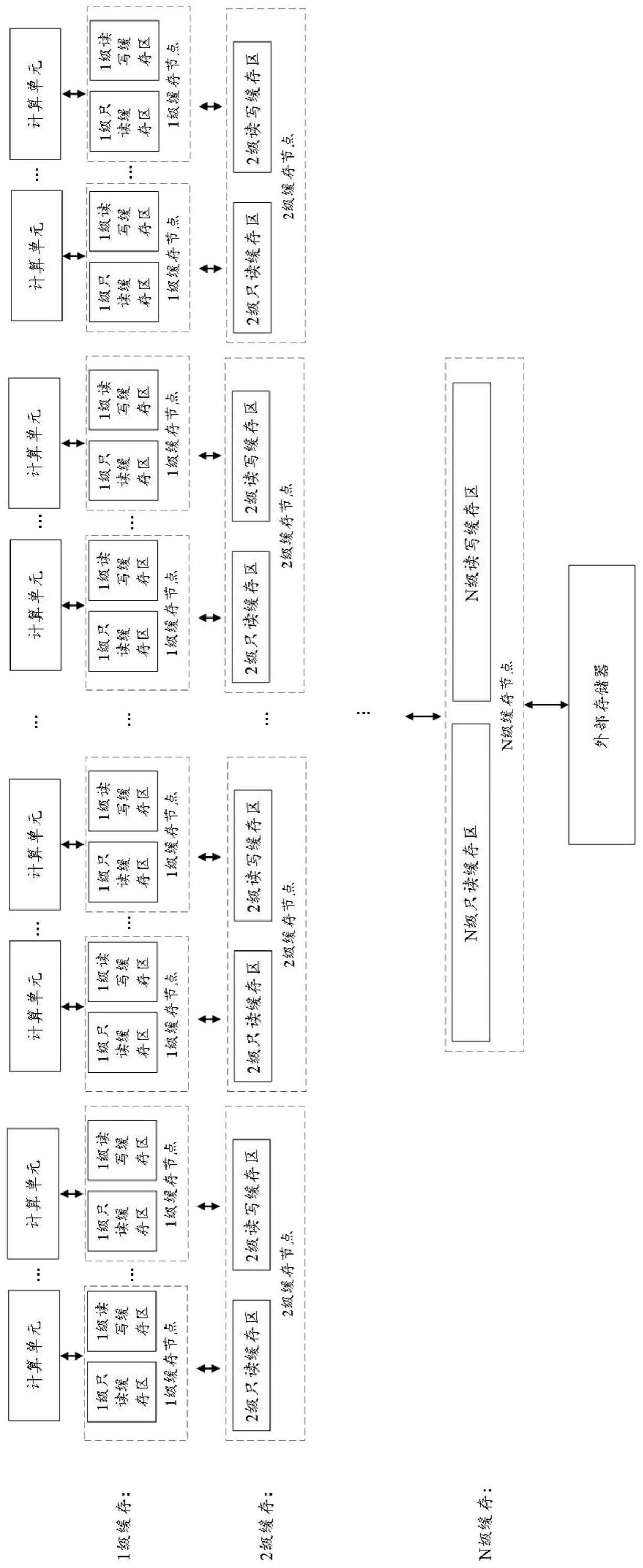

1、本公开至少一实施例提供一种缓存结构,用于矩阵计算,其中,所述缓存结构包括n级缓存,所述n级缓存中的第i级缓存包括至少1个i级缓存节点,每个i级缓存节点包括具有只读权限的i级只读缓存区以及具有读写权限的i级读写缓存区;每多个i级缓存节点共享一个i+1级缓存节点,所有n-1级缓存节点共享所述n级缓存中的第n级缓存包括的1个n级缓存节点,其中,所述n级缓存节点包括具有只读权限的n级只读缓存区以及具有读写权限的n级读写缓存区;所述第n级缓存与外部存储器电连接,每个1级缓存节点与对应的计算单元电连接;所述n级缓存中的具有只读权限的只读缓存区用于缓存所述矩阵计算中的作为计算输入参数的输入矩阵,以及在所述外部存储器和多个所述计算单元之间传输所述输入矩阵,所述n级缓存中的具有读写权限的读写缓存区用于缓存所述矩阵计算中的作为计算输出参数的输出矩阵,以及在所述外部存储器和多个所述计算单元之间传输所述输出矩阵,其中,n为大于1的正整数,i为1至n-1之间的任意正整数。

2、例如,在本公开至少一实施例提供的缓存结构中,每个计算单元包括运算模块和寄存器阵列,每个计算单元的寄存器阵列用于存储所述输入矩阵中的部分参数,以及所述输出矩阵中的部分参数;每个计算单元的运算模块包括多个乘法器和/或乘加器,用于并行执行乘法计算和/或乘加计算。

3、例如,在本公开至少一实施例提供的缓存结构中,所述矩阵计算包括矩阵乘法计算和/或矩阵乘加计算。

4、例如,在本公开至少一实施例提供的缓存结构中,作为计算输入参数的输入矩阵的读取通过由所述n级缓存中的具有只读权限的只读缓存区组成的只读缓存通路读入相应计算单元中的寄存器阵列,作为计算输出参数的输出矩阵的读取通过由所述n级缓存中的具有读写权限的读写缓存区组成的读写缓存通路读入相应计算单元中的寄存器阵列,由所述相应计算单元中的运算模块进行计算后得到更新后的输出矩阵,所述更新后的输出矩阵通过所述读写缓存通路从所述相应计算单元写回至所述外部存储器或任一级缓存的读写缓存区。

5、例如,在本公开至少一实施例提供的缓存结构中,响应于n为3,所述只读缓存通路包括所述相应计算单元对应的1级缓存节点中的只读缓存区,与所述1级缓存节点电连接的2级缓存节点中的只读缓存区,以及3级缓存节点中的只读缓存区;所述读写缓存通路包括所述相应计算单元对应的1级缓存节点中的读写缓存区,与所述1级缓存节点电连接的2级缓存节点中的读写缓存区,以及所述3级缓存节点中的读写缓存区。

6、例如,在本公开至少一实施例提供的缓存结构中,所述外部存储器为动态随机存储器。

7、本公开至少一实施例还提供一种电子设备,包括如本公开任一实施例所述的缓存结构。

8、例如,在本公开至少一实施例提供的电子设备中,所述电子设备包括与所述n级缓存一一对应的n级任务分发单元以及n个层级的线程组,每级任务分发单元包括至少一个任务分发单元,每个层级的线程组包括至少一个线程组,所述n级任务分发单元中位于第j级的第j级任务分发单元的数量与所述n级缓存中对应的第j级缓存包括的j级缓存节点的数量相同且一一对应,所述n个层级的线程组中位于第j级的j级线程组的数量与所述n级缓存中对应的第j级缓存包括的j级缓存节点的数量相同且一一对应,每个j级线程组包括的线程共享对应的j级缓存节点以缓存数据,其中,j为小于等于n的正整数。

9、例如,在本公开至少一实施例提供的电子设备中,所述n级任务分发单元中的位于第n级的第n级任务分发单元的数量为1,且配置为将用于所述矩阵计算的总任务拆分成p1个第一任务,分别分配给p1个n级线程组分时执行,p1为正整数。

10、例如,在本公开至少一实施例提供的电子设备中,在一个操作周期内,所述电子设备配置为执行1个n级线程组对应的第一任务。

11、例如,在本公开至少一实施例提供的电子设备中,所述电子设备配置为一次性读取执行所述p1个第一任务中的多个第一任务所需的输入矩阵的参数至所述n级缓存节点,以及调度多个所述计算单元在多个操作周期内执行完所述多个第一任务。

12、例如,在本公开至少一实施例提供的电子设备中,所述第n级任务分发单元还配置为选择至少一个第一任务,将每个第一任务拆分成p2个第二任务,以得到由每个第一任务对应的n级线程组拆分得到的p2个n-1级线程组,并将所述p2个n-1级线程组分发给p2个第n-1级任务分发单元,其中,p2为n-1级缓存节点的数量。

13、例如,在本公开至少一实施例提供的电子设备中,每个第k级任务分发单元配置为将接收的第k+1级任务分发单元分发的k级线程组拆分成p3个k-1级线程组,分发给相应的p3个第k-1级任务分发单元,其中,p3为共享一个k级缓存节点的k-1级缓存节点的数量,所述相应的p3个第k-1级任务分发单元为p3个k-1级缓存节点一一对应的p3个第k-1级任务分发单元,所述p3个k-1级缓存节点共享所述第k级任务分发单元对应的k级缓存节点,其中,k为大于1小于n的正整数。

14、例如,在本公开至少一实施例提供的电子设备中,每个第1级任务分发单元配置为将接收的1级线程组分发到对应的1级缓存节点以利用所述对应的1级缓存节点所对应的计算单元执行所述矩阵计算任务。

15、例如,在本公开至少一实施例提供的电子设备中,所述n级线程组包括的线程数量由1级缓存节点的数量及每个计算单元能够并行执行的任务数目决定;每个k级线程组包括的线程总数等于p3个k-1级线程组包括的线程总和,每个1级线程组包括的线程总数等于所述计算单元能够并行执行的任务数目。

16、例如,在本公开至少一实施例提供的电子设备中,每个任务分发单元配置为根据所述输入矩阵的参数之间的数据相关性拆分线程组。

17、例如,在本公开至少一实施例提供的电子设备中,针对根据所述输入矩阵的参数之间的数据相关性拆分得到的多个j-1级线程组,j级缓存节点中的具有只读权限的只读缓存区中缓存的输入矩阵的参数能够被共享所述j级缓存节点的对应所述多个j-1级线程组的多个j-1级缓存节点复用。

技术特征:

1.一种缓存结构,用于矩阵计算,其中,所述缓存结构包括n级缓存,

2.根据权利要求1所述的缓存结构,其中,每个计算单元包括运算模块和寄存器阵列,

3.根据权利要求1所述的缓存结构,其中,所述矩阵计算包括矩阵乘法计算和/或矩阵乘加计算。

4.根据权利要求1所述的缓存结构,其中,

5.根据权利要求4所述的缓存结构,其中,响应于n为3,

6.根据权利要求1-5中任一项所述的缓存结构,其中,所述外部存储器为动态随机存储器。

7.一种电子设备,包括如权利要求1-6中任一项所述的缓存结构。

8.根据权利要求7所述的电子设备,其中,所述电子设备包括与所述n级缓存一一对应的n级任务分发单元以及n个层级的线程组,

9.根据权利要求8所述的电子设备,其中,所述n级任务分发单元中的位于第n级的第n级任务分发单元的数量为1,且配置为将用于所述矩阵计算的总任务拆分成p1个第一任务,分别分配给p1个n级线程组分时执行,p1为正整数。

10.根据权利要求9所述的电子设备,其中,在一个操作周期内,所述电子设备配置为执行1个n级线程组对应的第一任务。

11.根据权利要求9所述的电子设备,其中,所述电子设备配置为一次性读取执行所述p1个第一任务中的多个第一任务所需的输入矩阵的参数至所述n级缓存节点,以及

12.根据权利要求9所述的电子设备,其中,所述第n级任务分发单元还配置为选择至少一个第一任务,将每个第一任务拆分成p2个第二任务,以得到由每个第一任务对应的n级线程组拆分得到的p2个n-1级线程组,并将所述p2个n-1级线程组分发给p2个第n-1级任务分发单元,

13.根据权利要求8所述的电子设备,其中,每个第k级任务分发单元配置为将接收的第k+1级任务分发单元分发的k级线程组拆分成p3个k-1级线程组,分发给相应的p3个第k-1级任务分发单元,

14.根据权利要求8所述的电子设备,其中,每个第1级任务分发单元配置为将接收的1级线程组分发到对应的1级缓存节点以利用所述对应的1级缓存节点所对应的计算单元执行所述矩阵计算任务。

15.根据权利要求13所述的电子设备,其中,所述n级线程组包括的线程数量由1级缓存节点的数量及每个计算单元能够并行执行的任务数目决定;

16.根据权利要求8-15中任一项所述的电子设备,其中,每个任务分发单元配置为根据所述输入矩阵的参数之间的数据相关性拆分线程组。

17.根据权利要求16所述的电子设备,其中,针对根据所述输入矩阵的参数之间的数据相关性拆分得到的多个j-1级线程组,j级缓存节点中的具有只读权限的只读缓存区中缓存的输入矩阵的参数能够被共享所述j级缓存节点的对应所述多个j-1级线程组的多个j-1级缓存节点复用。

技术总结

一种缓存结构和电子设备。该缓存结构包括N级缓存,N级缓存中的第i级缓存包括至少1个i级缓存节点,每个i级缓存节点包括具有只读权限的i级只读缓存区以及具有读写权限的i级读写缓存区;每多个i级缓存节点共享一个i+1级缓存节点;第N级缓存与外部存储器电连接,每个1级缓存节点与对应的计算单元电连接;N级缓存中的只读缓存区用于缓存矩阵计算中的作为计算输入参数的输入矩阵,以及在外部存储器和多个计算单元之间传输输入矩阵,N级缓存中的读写缓存区用于缓存矩阵计算中的作为计算输出参数的输出矩阵,以及在外部存储器和多个计算单元之间传输输出矩阵。该缓存结构可以有效降低缓存的硬件开销和设计复杂度。

技术研发人员:陈庆,袁庆,华芮,杨宇,容广健,刘洋,肖昊东,潘于

受保护的技术使用者:海光信息技术股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!