存储器接口模块和用于存储器接口模块的方法与流程

本申请涉及存储领域,具体而言,涉及一种存储器接口模块和用于存储器接口模块的方法、电子设备以及非瞬时性计算机可读存储介质。

背景技术:

1、在芯片主机需要拓展存储时,需要通过主机中的存储器接口模块来外接存储器。由于应用场景的不同,存储器接口模块往往需要兼容不同类型的外接存储器。对于同一种类型的外接存储器,往往也会因为生产厂家的不同,具有不同的读写时序要求。

2、本申请的发明人发现,现有的存储器接口模块,在生成读写信号的过程中,通常使用一个状态机把读写过程拆分为多个阶段,并使用数字逻辑控制每个阶段的信号翻转。这种方法具有一定的局限性,例如,当某种外接存储器的读写协议需要更多的阶段或者是在某一个阶段有超过设定阈值的信号需求时,此存储器接口模块则不再能兼容这种外接存储器。

技术实现思路

1、本申请旨在提出一种存储器接口模块和用于存储器接口模块的方法、电子设备以及非瞬时性计算机可读存储介质,以解决存储器接口模块的兼容问题。

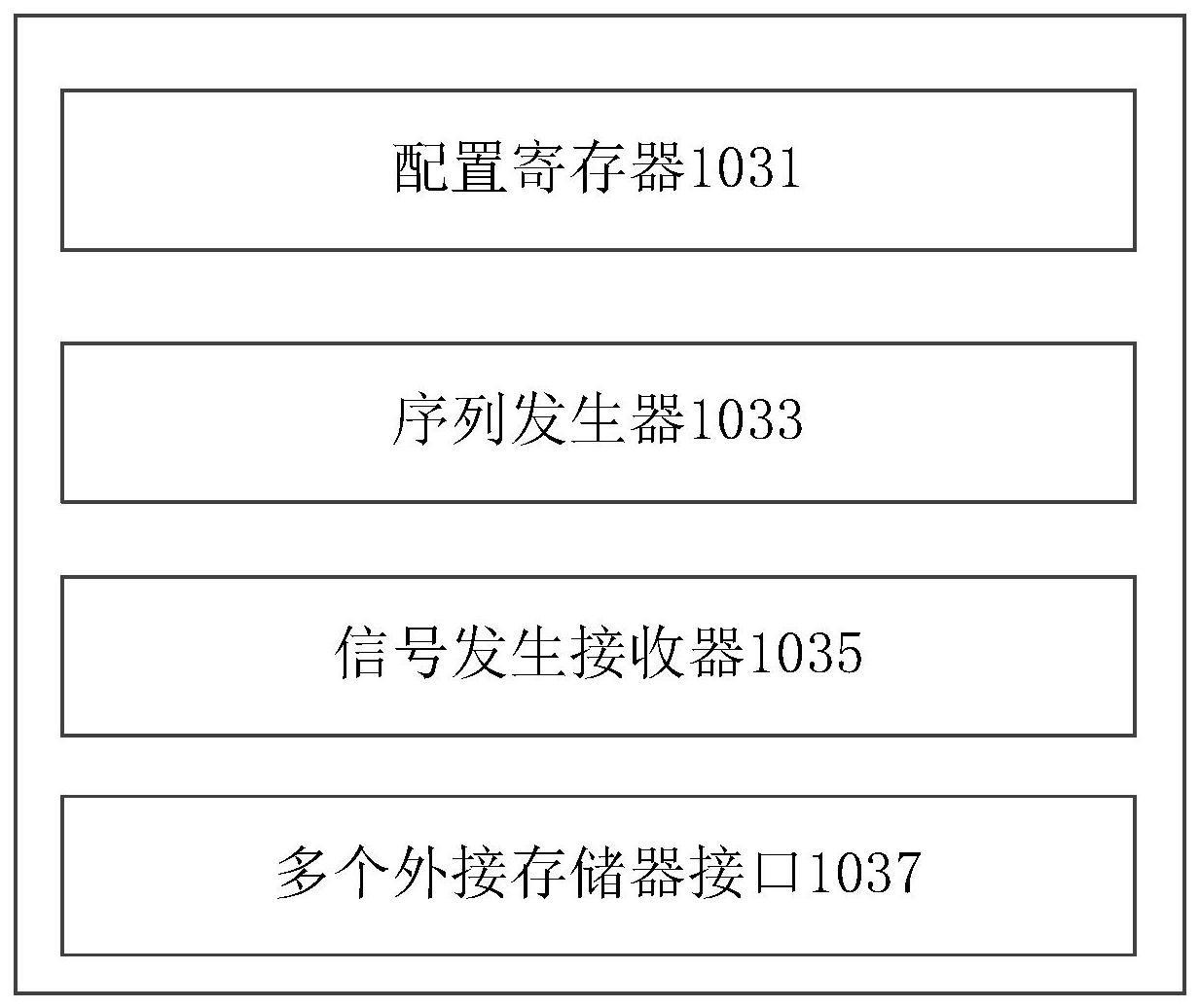

2、根据本申请的一方面,提出一种存储器接口模块,所述存储器接口模块用于连接主处理器和多个外接存储器,所述多个外接存储器遵守多个不同的协议,所述存储器接口模块包括配置寄存器、序列发生器、信号发生接收器和多个外接存储器接口,其中:所述配置寄存器,配置为接收来自主处理器的配置指令和配置数据,并存储所述配置数据;所述序列发生器,配置为根据所述配置寄存器存储的所述配置数据生成计数序列;所述信号发生接收器,配置为接收所述主处理器的读写指令,并根据所述配置寄存器的存储的所述配置数据和所述计数序列通过所述多个外接存储器接口向所述外接存储器输出控制信号。

3、根据一些实施例,所述配置数据包括所述序列发生器的计数周期、所述序列发生器的序列时钟分频系数,所述序列发生器配置为根据所述序列时钟分频系数和所述计数周期生成计数序列。

4、根据一些实施例,所述配置数据还包括所述存储器接口模块的外接存储器的种类、读写信号的时序,所述信号发生接收器还配置为根据所述外接存储器的种类、所述读写信号的时序以及所述序列发生器生成的所述计数序列,通过所述多个外接存储器接口对所述外接存储器执行读写操作。

5、根据一些实施例,所述信号发生接收器还配置为根据所述配置寄存器的存储的所述配置数据,启动、暂停和/或复位所述序列发生器。

6、根据一些实施例,所述信号发生接收器还配置为接收来自所述外接存储器发出的传输发生错误信息,并将所述传输发生错误信息发送给所述主处理器。

7、根据本申请的一方面,提出一种用于存储器接口模块的方法,所述存储器接口模块用于连接主处理器和多个外接存储器,所述多个外接存储器遵守多个不同的协议,所述方法包括:接收来自所述主处理器的配置指令,并根据所述配置指令存储配置数据;接收来自所述主处理器的读写指令,并根据所述配置数据和所述读写指令生成计数序列;接收来自所述主处理器的读写指令,并根据所述计数序列向所述多个外接存储器输出控制信号。

8、根据一些实施例,所述配置数据包括所述序列发生器的计数周期、所述序列发生器的序列时钟分频系数,所述存储器接口模块包括序列发生器,所述根据所述配置数据生成计数序列包括:所述序列发生器根据所述序列时钟分频系数和所述计数周期生成计数序列。

9、根据一些实施例,所述配置数据还包括所述存储器接口模块的外接存储器的种类、读写信号的时序,所述存储器接口模块还包括信号发生接收器和多个外接存储器接口,所述接收来自所述主处理器的读写指令,并根据所述计数序列向所述多个外接存储器输出控制信号包括:所述信号发生接收器接收来自所述主处理器的读写指令,并根据所述外接存储器的种类、所述读写信号的时序和所述计数序列,向所述多个外接存储器输出控制信号。

10、根据一些实施例,所述方法还包括:所述信号发生接收器根据所述主处理器的控制指令和所述外接存储器的反馈信号,启动、暂停和/或复位所述序列发生器。

11、根据一些实施例,所述方法还包括:所述信号发生接收器接收来自所述外接存储器发出的传输发生错误信息,并将所述传输发生错误信息发送给所述主处理器。

12、根据本申请的一方面,提出一种电子设备,包括:处理单元;以及存储单元,存储有计算机程序,当所述计算机程序被所述处理单元执行时,使得所述处理单元执行如前任一实施例所述的方法。

13、根据本申请的一方面,提出一种非瞬时性计算机可读存储介质,其上存储有计算机可读指令,当所述指令被处理器执行时,使得所述处理器执行如前任一实施例所述的方法。

14、根据本申请的实施例,通过产生可配置的多种读写信号,来最大限度的兼容不同类型的外接存储器,从而提升了芯片主机和外接存储器之间的兼容性。

15、应当理解的是,以上的一般描述和后文的细节描述仅是示例性的,并不能限制本申请。

技术特征:

1.一种存储器接口模块,其特征在于,所述存储器接口模块用于连接主处理器和多个外接存储器,所述多个外接存储器遵守多个不同的协议,所述存储器接口模块包括配置寄存器、序列发生器、信号发生接收器和多个外接存储器接口,其中:

2.根据权利要求1所述的存储器接口模块,其特征在于,所述配置数据包括所述序列发生器的计数周期、所述序列发生器的序列时钟分频系数,所述序列发生器配置为根据所述序列时钟分频系数和所述计数周期生成计数序列。

3.根据权利要求2所述的存储器接口模块,其特征在于,所述配置数据还包括所述存储器接口模块的外接存储器的种类、读写信号的时序,所述信号发生接收器还配置为根据所述外接存储器的种类、所述读写信号的时序以及所述序列发生器生成的所述计数序列,通过所述多个外接存储器接口对所述外接存储器执行读写操作。

4.根据权利要求1所述的存储器接口模块,其特征在于,所述信号发生接收器还配置为根据所述配置寄存器的存储的所述配置数据,启动、暂停和/或复位所述序列发生器。

5.根据权利要求1所述的存储器接口模块,其特征在于,所述信号发生接收器还配置为接收来自所述外接存储器发出的传输发生错误信息,并将所述传输发生错误信息发送给所述主处理器。

6.一种用于存储器接口模块的方法,其特征在于,所述存储器接口模块用于连接主处理器和多个外接存储器,所述多个外接存储器遵守多个不同的协议,所述方法包括:

7.根据权利要求6所述的方法,其特征在于,所述配置数据包括所述序列发生器的计数周期、所述序列发生器的序列时钟分频系数,所述存储器接口模块包括序列发生器,所述根据所述配置数据生成计数序列包括:

8.根据权利要求7所述的方法,其特征在于,所述配置数据还包括所述存储器接口模块的外接存储器的种类、读写信号的时序,所述存储器接口模块还包括信号发生接收器和多个外接存储器接口,所述接收来自所述主处理器的读写指令,并根据所述计数序列向所述多个外接存储器输出控制信号包括:

9.根据权利要求8所述的方法,其特征在于,所述方法还包括:

10.根据权利要求8所述的方法,其特征在于,所述方法还包括:

11.一种电子设备,包括:

12.一种非瞬时性计算机可读存储介质,其上存储有计算机可读指令,当所述指令被处理器执行时,使得所述处理器执行如权利要求6-10中任一项所述的方法。

技术总结

本申请提出一种存储器接口模块和用于存储器接口模块的方法、电子设备以及非瞬时性计算机可读存储介质,所述多个外接存储器遵守多个不同的协议,所述存储器接口模块包括配置寄存器、序列发生器、信号发生接收器和多个外接存储器接口,其中:所述配置寄存器,配置为接收来自主处理器的配置指令和配置数据,并存储所述配置数据;所述序列发生器,配置为根据所述配置寄存器存储的所述配置数据生成计数序列;所述信号发生接收器,配置为接收所述主处理器的读写指令,并根据所述配置寄存器的存储的所述配置数据和所述计数序列通过所述多个外接存储器接口向所述外接存储器输出控制信号。根据实施例,提升了存储器接口模块的兼容性。

技术研发人员:张博凯,梁洁,黄健

受保护的技术使用者:国民技术股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!