FPGA硬核IP动态重配置电路和接口电路的制作方法

本发明涉及集成电路技术。

背景技术:

1、现场可编程门阵列fpga(field programmable gate array)作为集成电路一类通用芯片,兼具asic电路的高性能与软件编程的灵活性,在数字逻辑系统、通信系统、工业控制等领域得到了广泛的应用。目前主流fpga都采用了sram来存储配置数据。这种fpga可以进行多次配置,通过配置不同的数据,可以实现不同的功能。

2、目前fpga重配置有三种方式:

3、1、关断重配置,该方法是通过复位fpga或者对fpga重新上电后,通过fpga外部的配置接口进行fpga配置。

4、2、动态重配置,该方法是在fpga启动,用户设计正常工作后,通过fpga内部的配置控制模块提供的配置访问接口,进行全局动态重配置,该方法虽然可以实现动态重配置功能,但是对用户要求较高,用户除了需要对fpga配置数据流的帧结构有充分的了解,还需要清楚fpga底层配置点与配置数据流对应关系,该关系涉及到fpga芯片本身的底层信息,这些信息厂商往往不会提供给用户,用户很难通过该方式实现动态重配置功能。

5、3、局部动态重配置,该方法是在fpga启动,用户设计正常工作后,通过调用fpga内部硬核ip的动态重配置接口进行特定硬核ip的动态重配置。

6、

7、先有技术存在1、配置时间较长;2、配置接口电路太复杂,不方便应用;3、扩展性较差等缺点。

技术实现思路

1、本发明所要解决的技术问题是,提供一种可灵活扩展的fpga硬核ip动态重配置接口电路,以及采用该接口电路的配置电路,能够根据不同硬核ip所需要的配置点数量进行灵活扩展。

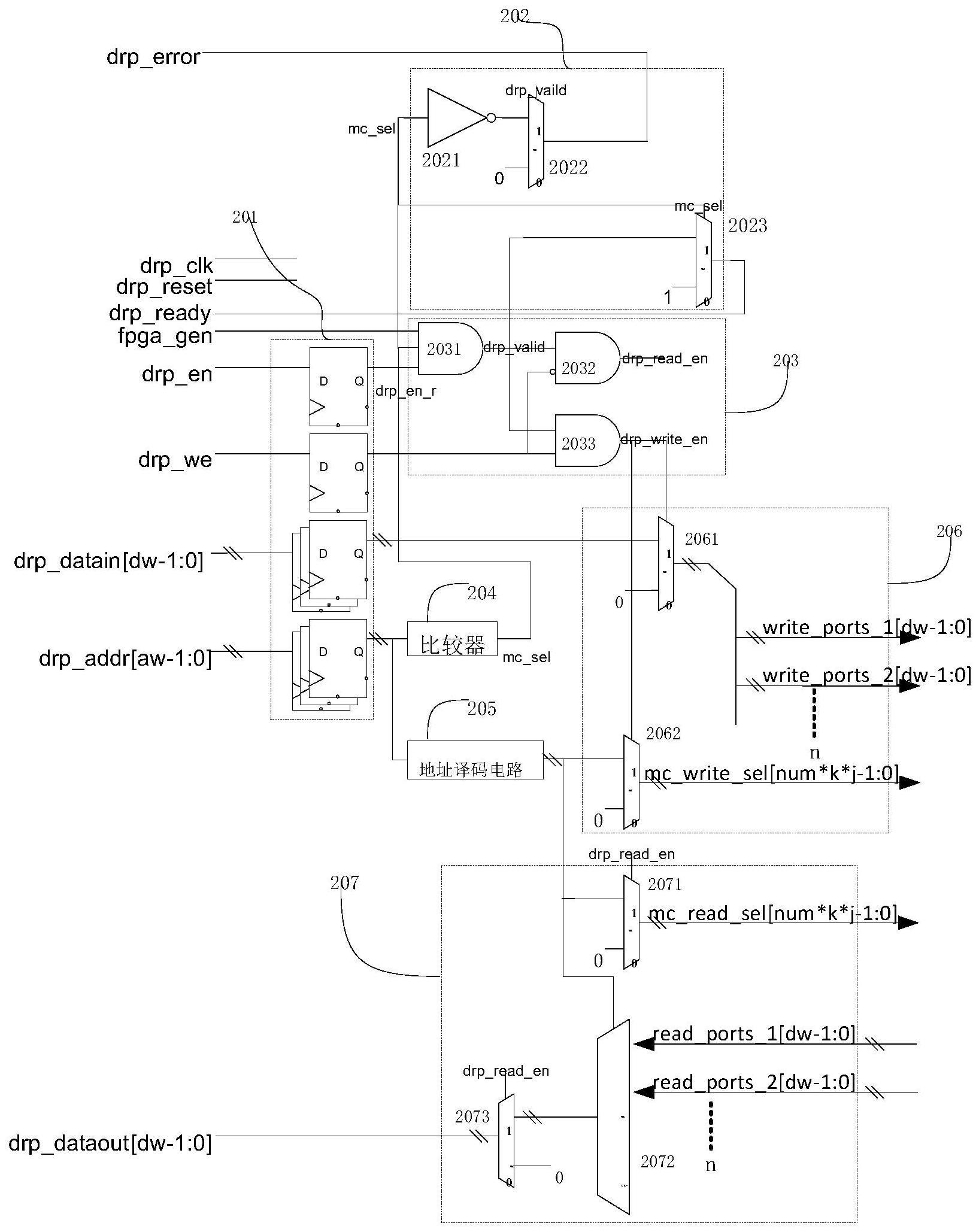

2、本发明解决所述技术问题采用的技术方案是,fpga硬核ip动态重配置接口电路,包括:

3、drp接口信号缓存寄存器(201),用于寄存接口控制信号;

4、输出反馈电路(202),用于反馈读写操作结果状态;

5、读写使能控制电路(203),用于产生读写使能信号;

6、比较器电路(204),用于根据sram阵列大小进行调整设置地址有效范围;

7、地址译码电路(205),用于将输入的二进制地址转换成one hot编码信号;

8、srma阵列写控制电路(206),用于对sram阵列进行写操作;

9、srma阵列读控制电路(207),用于对sram阵列进行读操作;

10、drp接口信号缓存寄存器(201)与读写使能控制电路(203)、比较器电路(204)、地址译码电路(205)和srma阵列写控制电路(206)连接,比较器电路(204)与输出反馈电路(202)和读写使能控制电路(203)连接,地址译码电路(205)连接到srma阵列写控制电路(206)和srma阵列读控制电路(207),读写使能控制电路(203)连接到srma阵列写控制电路(206)。

11、进一步的,

12、drp接口信号缓存寄存器(201)包括:

13、第一d触发器单元,其输入端接drp使能信号;

14、第二d触发器单元,其输入端接drp读写控制信号;

15、第三d触发器单元,其输入端作为动态重配置数据输入端口;

16、第四d触发器单元,其输入端作为动态重配置地址输入端口;

17、比较器电路(204)的一路输入接第四d触发器单元,另一路输入接过滤地址存储器。过滤地址存储器在图中未示出,与其连接的比较器的输入端也未示出,普通技术人员能够理解。

18、第三d触发器单元中的d触发器数量由数据宽度决定,第四d触发器单元中的d触发器数量由地址宽度决定。

19、输出反馈电路(202)包括:

20、输出反馈反相器(2021),其输入端接比较器(204)的输出端;

21、第一输出反馈选择器(2022),其第一输入端接输出反馈反相器,第二输入端接逻辑0,输出端作为读写错误标志输出端;

22、第二输出反馈选择器(2023),其第一输入端接第一读写使能与门(2031)的输出端,第二输入端接逻辑1,输出端作为drp状态输出端。

23、读写使能控制电路(203)包括:

24、第一读写使能与门(2031),其第一输入端接fpga内部全局使能信号输入端,第二输入端接比较器(204)的输出端,第三输入端接第一d触发器单元的输出端;

25、第一读写使能与门(2032),其第一输入端接第一读写使能与门(2031)的输出端,第二输入端通过反相器接第二d触发器的输出端;

26、第三读写使能与门(2033),其第一输入端接第一读写使能与门(2031)的输出端,第二输入端接第二d触发器的输出端。

27、srma阵列写控制电路(206)包括:

28、第一写控制选择器(2061),其控制端接第三读写使能与门(2033)的输出端,第一输入端接第三d触发器单元输出端,第二输入端接逻辑0,输出端接srma阵列电路(102)的写入端口;

29、第二写控制选择器(2062),其控制端接第三读写使能与门(2033)的输出端,第一输入端接地址译码电路(205)输出端,第二输入端接逻辑0,输出端接srma阵列电路(102)的写使能端口。

30、srma阵列读控制电路(207)包括:

31、第一读控制选择器(2071),其控制端接drp读使能信号端,第一输入端接地址译码电路输出端,第二输入端接逻辑0,输出端接srma阵列电路(102)的读使能端口;

32、第二读控制选择器(2072),其控制端接接地址译码电路(205)输出端,输入端接输出端接srma阵列电路(102)的读端口;

33、第三读控制选择器(2073),其控制端接drp读使能信号端,第一输入端接第二读控制选择器(2072)输出端,第二输入端接逻辑0。

34、本发明还提供一种fpga硬核ip动态重配置电路,包括sram阵列电路,sram阵列电路包括sram阵列和配置电路,还包括前述fpga硬核ip动态重配置接口电路,fpga硬核ip动态重配置接口电路通过sram读写控制电路和sram阵列连接。

35、本发明的有益效果:

36、(1)支持不同配置点大小需求的fpga硬核ip。本发明电路结构只需根据配置点大小和数据宽度需求修改相应参数即可。

37、(2)实现硬核ip配置点的快速访问。直接访问硬核ip配置sram,高效且快速的进行修改。

38、(3)电路结构简单,占用面积较小。本发明电路使用逻辑门和寄存器较少,逻辑比较简单,实现比较容易,电路面积也比较小,方便嵌入到fpga硬核ip中。

技术特征:

1.fpga硬核ip动态重配置接口电路,其特征在于,包括:

2.如权利要求1所述的fpga硬核ip动态重配置接口电路,其特征在于,

3.如权利要求2所述的fpga硬核ip动态重配置接口电路,其特征在于,输出反馈电路(202)包括:

4.如权利要求3所述的fpga硬核ip动态重配置接口电路,其特征在于,srma阵列写控制电路(206)包括:

5.如权利要求4所述的fpga硬核ip动态重配置接口电路,其特征在于,srma阵列读控制电路(207)包括:

6.fpga硬核ip动态重配置电路,包括sram阵列电路,sram阵列电路包括sram阵列和配置电路,其特征在于,还包括权利要求1~6中任一项所述的fpga硬核ip动态重配置接口电路,fpga硬核ip动态重配置接口电路通过sram读写控制电路和sram阵列连接。

技术总结

FPGA硬核IP动态重配置接口电路,涉及集成电路技术,本发明包括:drp接口信号缓存寄存器(201),输出反馈电路(202),读写使能控制电路(203),比较器电路(204),地址译码电路(205),SRMA阵列写控制电路(206),SRMA阵列读控制电路(207)。本发明支持不同配置点大小需求的FPGA硬核IP。

技术研发人员:邢亚楠,陶琼,康暄,阙小茜,李显军,田征

受保护的技术使用者:成都华微电子科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!