一种雷达系统中数据流快速恢复方法与流程

本申请涉及通信的领域,尤其是涉及一种雷达系统中数据流快速恢复方法。

背景技术:

1、serial rapid io是一种高性能、低引脚数、基于数据包交换的互连体系结构,是为满足高性能嵌入式系统需求而设计的一种开放式互连技术标准。srio主要应用于嵌入式系统内部互连,支持芯片到芯片、板到板间的通讯,可作为嵌入式设备的背板连接。

2、目前机载雷达处理系统中主要包括数据处理模块、信号处理模块、数据交换模块等,芯片间及板间采用srio互连总线协议来实现数据的大带宽、高可靠性传输。其中针对大数据高带宽通信的需求,在雷达处理单元中设计了基于srio总线的全交换网络,实现了多个模块间以及模块内fpga、cpu以及dsp处理器等多个芯片之间灵活通信的方法。但是数据传输过程中,某级srio节点通信异常会导致整个雷达处理系统的数据流堵塞,导致整个雷达处理系统工作异常。传统的恢复方法是对整个雷达处理系统进行复位,各模块重新启动耗时比较久,复位过程中航电系统没画面,影响飞行员观察和整个系统的连续性。

技术实现思路

1、有鉴于此,本申请提供一种雷达系统中数据流快速恢复方法,解决当前雷达处理系统中由于srio节点通信异常导致数据流恢复时间过长、航电画面消失的问题,通过中断及时通知主控模块,并通过操作错误端口两端的寄存器清除错误,耗时毫秒级别,极大的缩短恢复时间。

2、本申请提供的一种雷达系统中数据流快速恢复方法采用如下的技术方案:

3、一种雷达系统中数据流快速恢复方法,所述雷达系统包括雷达处理单元,雷达处理单元包括预处理模块、信号处理模块和主控模块,信号处理模块和主控模块通过srio总线通信,信号处理模块和预处理模块通过srio总线通信,信号处理模块和主控模块通过bit总线互联,主控模块和预处理模块通过bit总线互联,bit总线独立于srio通信总线;

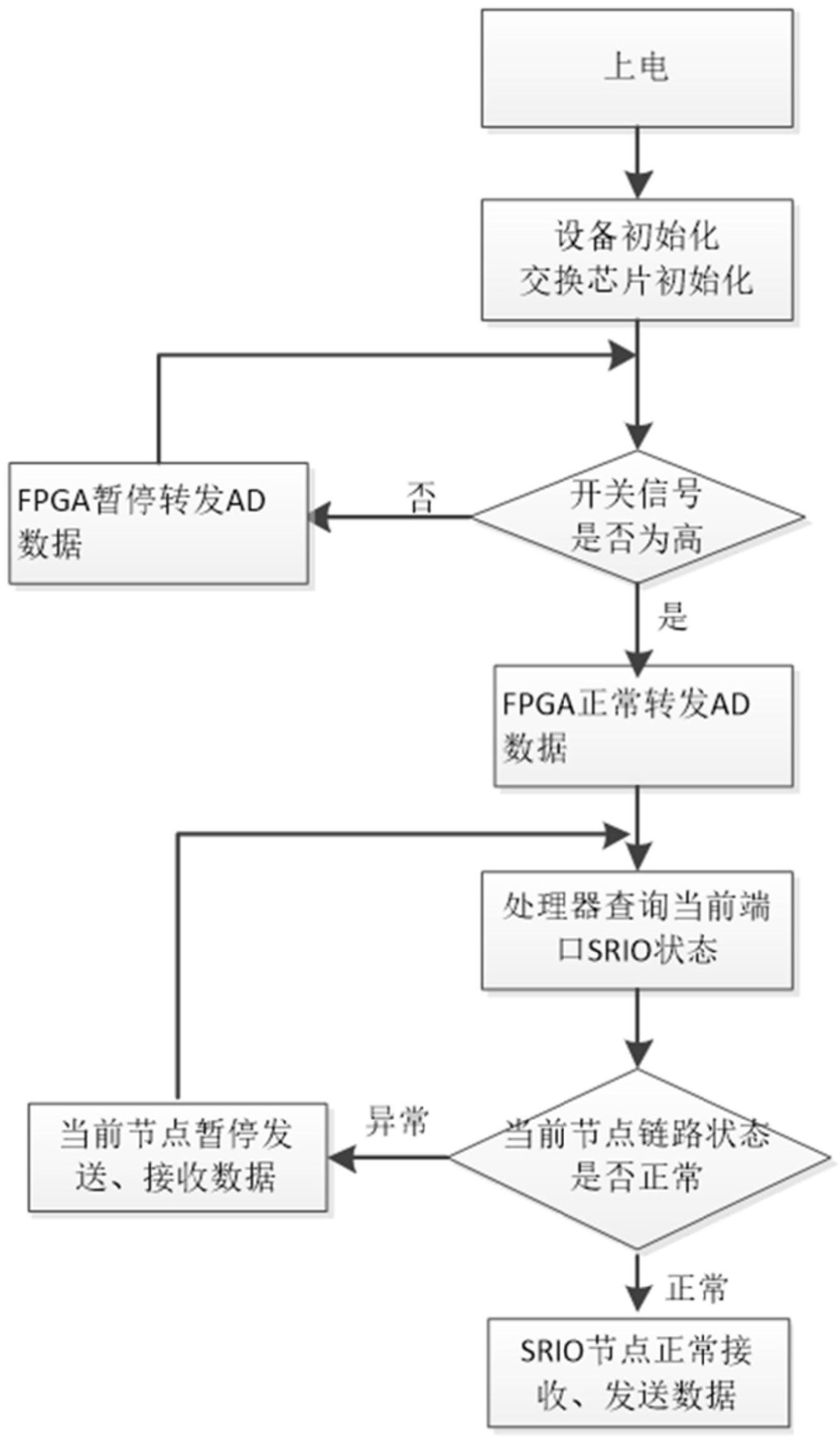

4、所述方法包括如下步骤:

5、当srio交换芯片检测到端口发生异常时,srio交换芯片的中断管脚信号以中断的形式通知主控模块;

6、主控模块通过开关信号通知雷达系统的预处理模块关闭srio数据转发功能;

7、主控模块接收到中断后主动通过bit系统获取srio交换芯片的异常端口,通过bit总线配置srio交换芯片的异常端口对应的寄存器来复位当前的异常端口,并通过当前复位后的端口向对端节点的端口发送复位请求,使当前srio节点错误清除;

8、主控模块检测到错误清除后通过开关信号通知预处理模块开启转发功能,雷达系统数据流恢复正常。

9、可选的,在srio交换芯片的节点上启动srio数据传输时,预设时间戳,在预设的时间内没有完成数据传输,则停止srio数据传输。

10、可选的,预处理模块、信号处理模块和主控模块均包括srio交换芯片和fpga,预处理模块、信号处理模块和主控模块中srio交换芯片的中断管脚irq_n接入各自的fpga。。

11、可选的,预处理模块和信号处理模块还包括dsp,主控模块还包括cpu,预处理模块、信号处理模块和主控模块均包括arm;

12、主控模块的cpu通过本地总线连接至fpga,主控模块上fpga与arm互联完成控制命令下发,预处理模块和信号处理模块上fpga与arm互联完成dsp的bit数据上报,各个模块的arm周期性读取srio交换机内部端口状态寄存器,预处理模块和信号处理模块的arm将所有bit信息整合传输给主控模块内arm芯片,主控模块上arm通过低速接口将雷达处理单元的所有bit信息传输给cpu,cpu再通过fc总线上报航电系统。

13、可选的,fpga通过i2c总线与arm互联。

14、可选的,arm通过i2c接口周期性读取srio交换机内部端口状态寄存器。

15、可选的,arm将所有bit信息整合并通过rs485总线传输给主控模块内arm芯片,主控模块通过rs485访问预处理模块和信号处理模块的arm。

16、综上所述,本申请包括以下有益技术效果:

17、本申请中通过中断及时通知主控模块,并通过操作错误端口两端的寄存器清除错误,耗时毫秒级别,极大的缩短恢复时间。

18、本申请中恢复错误时主控模块依然处于正常状态,可以响应航电系统部分功能,不会导致航电系统出现无画面状态。其他节点处理模块待错误恢复后仍然可以继续srio通信。

19、本申请通过中断的形式通知主控模块,快速关闭雷达处理系统数据源,防止故障节点前端的处理模块由于数据反压全部卡死。也可以防止系统在进行恢复时,srio总线上仍由数据传输,影响srio端口恢复效果。

技术特征:

1.一种雷达系统中数据流快速恢复方法,其特征在于,所述雷达系统包括雷达处理单元,雷达处理单元包括预处理模块、信号处理模块和主控模块,信号处理模块和主控模块通过srio总线通信,信号处理模块和预处理模块通过srio总线通信,信号处理模块和主控模块通过bit总线互联,主控模块和预处理模块通过bit总线互联,bit总线独立于srio通信总线;

2.根据权利要求1所述的雷达系统中数据流快速恢复方法,其特征在于,在srio交换芯片的节点上启动srio数据传输时,预设时间戳,在预设的时间内没有完成数据传输,则停止srio数据传输。

3.根据权利要求1所述的雷达系统中数据流快速恢复方法,其特征在于,预处理模块、信号处理模块和主控模块均包括srio交换芯片和fpga,预处理模块、信号处理模块和主控模块中srio交换芯片的中断管脚irq_n接入各自的fpga。

4.根据权利要求3所述的雷达系统中数据流快速恢复方法,其特征在于,预处理模块和信号处理模块还包括dsp,主控模块还包括cpu,预处理模块、信号处理模块和主控模块均包括arm;

5.根据权利要求4所述的雷达系统中数据流快速恢复方法,其特征在于,fpga通过i2c总线与arm互联。

6.根据权利要求4所述的雷达系统中数据流快速恢复方法,其特征在于,arm通过i2c接口周期性读取srio交换机内部端口状态寄存器。

7.根据权利要求4所述的雷达系统中数据流快速恢复方法,其特征在于,arm将所有bit信息整合并通过rs485总线传输给主控模块内arm芯片,主控模块通过rs485访问预处理模块和信号处理模块的arm。

技术总结

本申请提供了一种雷达系统中数据流快速恢复方法,属于通信的技术领域,具体当SRIO交换芯片检测到端口发生异常时,SRIO交换芯片的中断管脚信号以中断的形式通知主控模块;主控模块通过开关信号通知雷达系统的预处理模块关闭SRIO数据转发功能;主控模块接收到中断后主动通过BIT系统获取SRIO交换芯片的异常端口,通过BIT总线配置SRIO交换芯片的异常端口对应的寄存器来复位当前的异常端口,并通过当前复位后的端口向对端节点的端口发送复位请求,使当前SRIO节点错误清除;通过中断及时通知主控模块,并通过操作错误端口两端的寄存器清除错误,耗时毫秒级别,极大的缩短恢复时间。

技术研发人员:吴彬,檀毛琴,张新刚

受保护的技术使用者:中国航空工业集团公司雷华电子技术研究所

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!