一种基于ARM+FPGA嵌入式异构架构的交互式振动消除应力系统的设计方法

本发明涉及振动设备控制,具体涉及一种基于arm+fpga嵌入式异构架构的交互式振动消除应力系统的设计方法。

背景技术:

1、目前金属工件在生产制造过程中,会导致工件内部产生残余应力,其存在会影响工件的强度和使用寿命,因此消除残余应力对于机械加工等方便有着重要的意义,振动时效消除应力是一种无污染、成本低、高效能的新型时效处理技术,目前振动时效设备控制系统领域正处于快速发展阶段,常见的背景技术包括数字信号处理、硬件加速和嵌入式系统、异构计算、并行计算以及跨平台ui界面开发框架,本发明结合上述几种技术,设计一种基于arm+fpga嵌入式异构架构的交互式振动消除应力系统的设计方法,arm+fpga嵌入式异构架构的优点可以在不减少计算能力的同时降低系统资源的消耗,arm作为核心处理芯片,而fpga作为底层实践、实现者,完成大部分电路驱动和数据采集处理,提高系统处理速度的同时提高系统的效率,还可以提供移动性和便携性。交互式的引入可以使系统的使用操作变得舒适更加贴近用户,降低系统使用难度,减少学习培训成本。

技术实现思路

1、本发明实施例提供一种基于arm+fpga嵌入式异构架构的交互式振动消除应力系统的设计方法,目的在于降低振动时效控制系统的操作学习成本,实现直观且美观的时效操作,加快频谱分析和信号处理的速度,使用更少的系统资源、更低的能耗,实现准确且高效的振动时效处理效果。

2、本发明实施例为实现上述目的采用的技术方案如下:

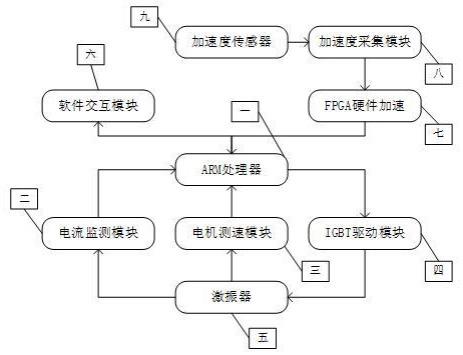

3、一种基于arm+fpga嵌入式异构架构的交互式振动消除应力系统,包括用于操控振动时效处理与时效分析的arm处理器,其所述arm处理器的输入端连接有用于监控激振器电流的电流监测模块、用于测量激振器电机转速的电机测速模块、用于进行人机交互控制的软件交互模块、用于对加速度数据进行频谱分析的fpga硬件加速,所述arm处理器的输出端连接有用于控制激振器电机转速的igbt驱动模块、用于显示时效处理效果和时效分析结论的软件交互模块,所述igbt驱动模块的输出端连接有用于进行振动时效的激振器,所述激振器的输出端连接有用于监控激振器电流的电流监测模块、用于测量激振器电机转速的电机测速模块,所述fpga硬件加速的输入端连接有用于采集加速度数据的加速度采集模块,所述加速度采集模块的输入端有连接用于获取加速度的加速度传感器。

4、一种基于arm+fpga嵌入式异构架构的交互式振动消除应力系统的设计方法,具体步骤如下:

5、步骤一、在arm处理器的系统中打开软件交互模块的操作界面;

6、步骤二、在步骤一打开的操作界面中配置振前扫频的参数,下发振前扫频指令到arm处理器,arm处理器控制igbt驱动模块调节激振器的电机转速完成振前扫频;

7、步骤三、fpga硬件加速实时监控获取振后扫频过程中加速度采集模块上传的加速度值,等待步骤二振前扫频完成,对加速度数据进行fft变换,将变换后的振前扫频频谱数据经过arm处理器上传到软件交互模块的界面进行显示;

8、步骤四、分析频谱数据,得到时效处理的频率值和激振器的电机转速值,在步骤一打开的操作界面中配置时效处理的参数,下发时效处理指令到arm处理器,arm处理器控制igbt驱动模块调节激振器的电机转速完成时效处理;

9、步骤五、在步骤一打开的操作界面中配置振后扫频的参数,下发振后扫频指令到arm处理器,arm处理器控制igbt驱动模块调节激振器的电机转速完成振后扫频;

10、步骤六、fpga硬件加速实时监控获取振后扫频过程中加速度采集模块上传的加速度值,等待步骤五振后扫频完成,对加速度数据进行fft变换,将变换后的振后扫频频谱数据经过arm处理器上传到软件交互模块的界面进行显示;

11、步骤七、在步骤一打开的操作界面中选择时效分析,软件交互模块会将振前扫频和振后扫频两组频谱数据进行比对,打印输出时效分析结果,实现振动消除残余应力。

12、进一步的,所述步骤一中arm处理器为搭载rk3588处理器的嵌入式平台,运行ubuntu22.04系统,所述的软件交互模块的操作界面是用qt编写。

13、进一步的,所述步骤二中arm处理器(一)与igbt驱动模块(四)是通过网口进行连接。

14、进一步的,所述步骤三中fpga硬件加速(七)为 xilinx zcu102开发板,频谱分析使用全相位实时fft算法。

技术特征:

1.一种基于arm+fpga嵌入式异构架构的交互式振动消除应力系统,包括用于操控振动时效处理与时效分析的arm处理器(一),其特征在于:所述arm处理器(一)的输入端连接有用于监控激振器电流的电流监测模块(二)、用于测量激振器电机转速的电机测速模块(三)、用于进行人机交互控制的软件交互模块(六)、用于对加速度数据进行频谱分析的fpga硬件加速(七),所述arm处理器(一)的输出端连接有用于控制激振器电机转速的igbt驱动模块(四)、用于显示时效处理效果和时效分析结论的软件交互模块(六),所述igbt驱动模块(四)的输出端连接有用于进行振动时效的激振器(五),所述激振器(五)的输出端连接有用于监控激振器电流的电流监测模块(二)、用于测量激振器电机转速的电机测速模块(三),所述fpga硬件加速(七)的输入端连接有用于采集加速度数据的加速度采集模块(八),所述加速度采集模块(八)的输入端有连接用于获取加速度的加速度传感器(九)。

2.一种基于arm+fpga嵌入式异构架构的交互式振动消除应力系统的设计方法,具体步骤如下:

3.根据权利要求2所述的一种基于arm+fpga嵌入式异构架构的交互式振动消除应力系统的设计方法,其特征在于:所述步骤一中arm处理器(一) 为搭载rk3588处理器的嵌入式平台,运行ubuntu22.04系统,所述的软件交互模块(六)的操作界面是用qt编写。

4.根据权利要求2所述的一种基于arm+fpga嵌入式异构架构的交互式振动消除应力系统的设计方法,其特征在于:所述步骤二中arm处理器(一)与igbt驱动模块(四)是通过网口进行连接。

5.根据权利要求2所述的一种基于arm+fpga嵌入式异构架构的交互式振动消除应力系统的设计方法,其特征在于:所述步骤三中fpga硬件加速(七)为 xilinx zcu102开发板,频谱分析使用全相位实时fft算法。

技术总结

本发明提供一种基于ARM+FPGA嵌入式异构架构的交互式振动消除应力系统的设计方法,该系统设计的方法可以实现高效并行数据处理、节省系统资源、提高运算速度。包括用于操控振动时效处理与时效分析的ARM处理器,其所述ARM处理器的输入端连接有用于监控激振器电流的电流监测模块、用于测量激振器电机转速的电机测速模块、用于进行人机交互控制的软件交互模块、用于对加速度数据进行频谱分析的FPGA硬件加速,所述ARM处理器的输出端连接有用于控制激振器电机转速的IGBT驱动模块、用于显示时效处理效果和时效分析结论的软件交互模块,所述IGBT驱动模块的输出端连接有用于进行振动时效的激振器,所述激振器的输出端连接有用于监控激振器电流的电流监测模块、用于测量激振器电机转速的电机测速模块,所述FPGA硬件加速的输入端连接有用于采集加速度数据的加速度采集模块,所述加速度采集模块的输入端有连接用于获取加速度的加速度传感器。

技术研发人员:李念强,岳炳臣,刘英杰,孔祥灿

受保护的技术使用者:济南大学

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!