一种FPGA开发板的防呆方法、装置、设备及介质与流程

本申请涉及芯片验证,尤其涉及一种fpga开发板的防呆方法、装置、设备及介质。

背景技术:

1、asic(application specific integrated circuit,专用集成电路)芯片是一种基于为专门目的而设计的集成电路构成的专有应用程序芯片。asic芯片的验证通常使用基于fpga(field programmable gate array,现场可编程逻辑阵列)的原型验证平台。对于中小逻辑规模的asic芯片的原型验证平台通常使用fpga开发板为基本载体。然而,由于各个fpga开发板的采购厂家和版本可能所有不同,经常存在多种fpga开发板在一个项目中同时使用的情况。不同的fpga开发板上fpga芯片与开发板上外设芯片以及扩展接口相连的i/o口的定义均可能存在区别。因此,即使对于同一个项目、同一颗芯片、相同的功能验证,不同的fpga开发板也需要使用不同的比特流文件。

2、目前,在实际项目开发过程中,同一个项目中使用多种fpga开发板,并且对应于多种比特流文件,这就存在fpga开发板和比特流文件的匹配使用问题。如果fpga开发板和比特流文件之间匹配错误,即使比特流文件下载成功,轻则导致原型验证平台功能异常,重则烧毁fpga开发板。

技术实现思路

1、本申请实施例提供了一种fpga开发板的防呆方法、装置、设备及介质,用以解决现有技术存在的fpga开发板和比特流文件匹配错误导致fpga开发板损坏的问题。

2、本申请实施例提供的技术方案如下:

3、一方面,本申请实施例提供了一种fpga开发板的防呆方法,包括:

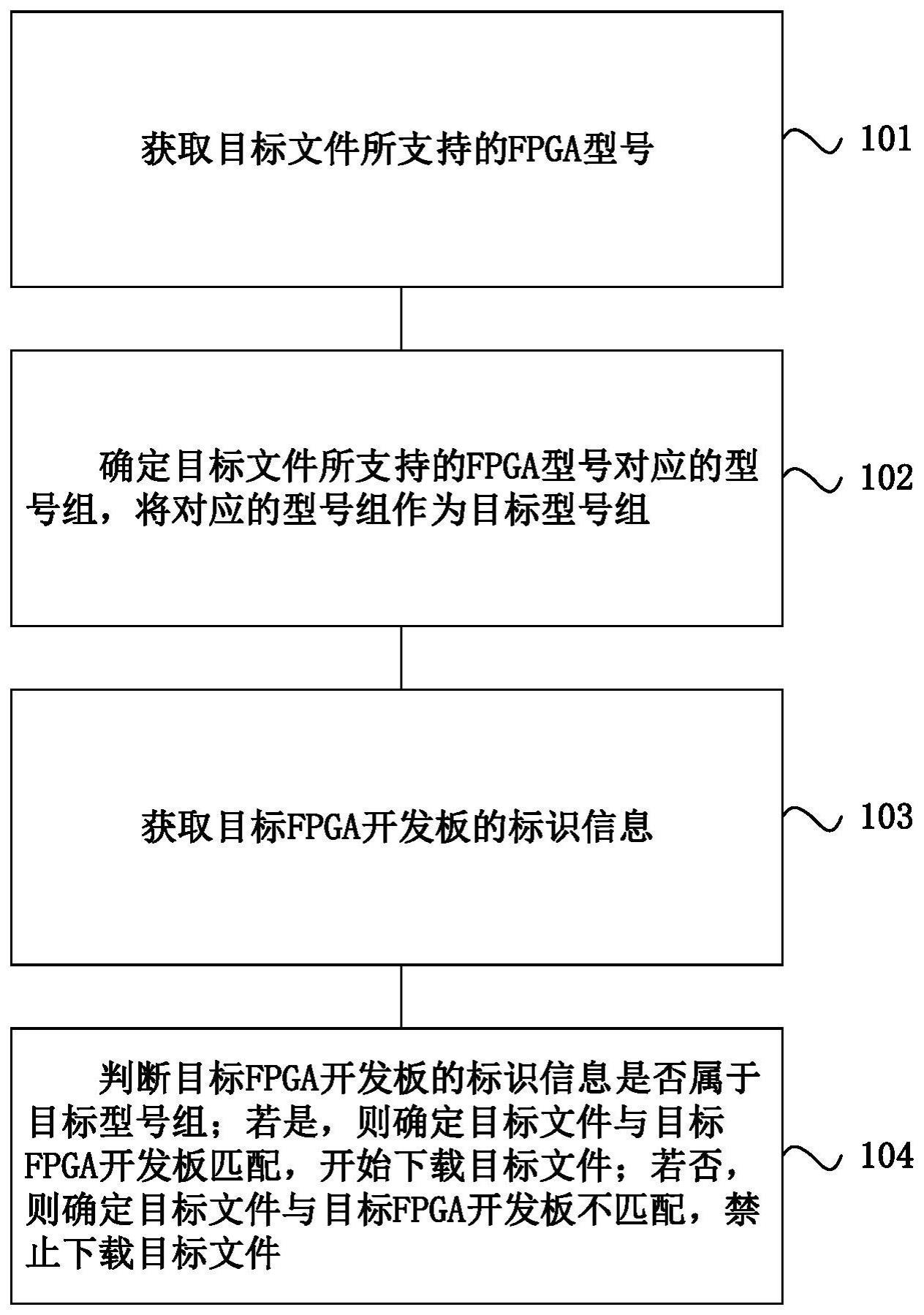

4、获取目标文件所支持的fpga型号;

5、确定目标文件所支持的fpga型号对应的型号组,将对应的型号组作为目标型号组;

6、获取目标fpga开发板的标识信息;

7、判断目标fpga开发板的标识信息是否属于目标型号组;

8、若是,则确定目标文件与目标fpga开发板匹配,开始下载目标文件;

9、若否,则确定目标文件与目标fpga开发板不匹配,禁止下载目标文件。

10、在一种可能的实施方式中,获取目标文件所支持的fpga型号的步骤,包括:

11、从下载脚本中读取目标文件;

12、解析目标文件的头部信息,基于目标文件的头部信息的存储格式确定目标文件所支持的fpga型号。

13、在一种可能的实施方式中,获取目标fpga开发板的标识信息,包括:

14、建立与目标fpga开发板的连接,发送标识信息读取指令至目标fpga开发板;

15、接收目标fpga开发板发送的目标fpga开发板的标识信息。

16、在一种可能的实施方式中,确定目标文件与目标fpga开发板不匹配,禁止下载目标文件之后,还包括:

17、发送目标文件与目标fpga开发板不匹配的信息至下载脚本的运行终端,以使运行终端显示匹配失败提示。

18、在一种可能的实施方式中,获取目标文件所支持的fpga型号之前,还包括:

19、获取当前所有的fpga开发板的型号和标识信息;

20、按照型号将当前所有的fpga开发板的标识信息划分为至少一个型号组。

21、在一种可能的实施方式中,型号组与fpga开发板的型号一一对应,每个型号组中包括当前所有fpga开发板中对应型号的fpga开发板的标识信息。

22、另一方面,本申请实施例提供了一种fpga开发板的防呆装置,包括:

23、第一信息获取单元,用于获取目标文件所支持的fpga型号;

24、型号组确定单元,用于确定目标文件所支持的fpga型号对应的型号组,将对应的型号组作为目标型号组;

25、第二信息获取单元,用于获取目标fpga开发板的标识信息;

26、匹配判断单元,用于判断目标fpga开发板的标识信息是否属于目标型号组;

27、第一执行单元,用于目标fpga开发板的标识信息属于目标型号组时,确定目标文件与目标fpga开发板匹配,开始下载目标文件;

28、第二执行单元,用于目标fpga开发板的标识信息不属于目标型号组时,确定目标文件与目标fpga开发板不匹配,禁止下载目标文件。

29、在一种可能的实施方式中,fpga开发板的防呆装置还包括:

30、第三信息获取单元,用于获取当前所有的fpga开发板的型号和标识信息;

31、分组单元,用于按照型号将当前所有的fpga开发板的标识信息划分为至少一个型号组。

32、另一方面,本申请实施例提供了一种电子设备,包括:存储器、处理器和存储在存储器上并可在处理器上运行的计算机程序,处理器执行计算机程序时实现本申请实施例提供的fpga开发板的防呆方法。

33、另一方面,本申请实施例还提供了一种计算机可读存储介质,计算机可读存储介质存储有计算机指令,计算机指令被处理器执行时实现本申请实施例提供的fpga开发板的防呆方法。

34、本申请实施例的有益效果如下:

35、本申请实施例中,通过获取目标文件所支持的fpga型号,确定所述目标文件所支持的fpga型号对应的型号组作为目标型号组,获取目标fpga开发板的标识信息,判断所述目标fpga开发板的标识信息属于所述目标型号组,则确定所述目标文件与所述目标fpga开发板匹配,开始否则确定所述目标文件与所述目标fpga开发板不匹配,禁止下载所述目标文件,可以在目标文件下载前确定目标文件与目标fpga开发板是否匹配,仅在两者匹配的情况下进行文件的下载,避免fpga开发板和比特流文件匹配错误导致fpga开发板损坏的情况。

36、本申请的其它特征和优点将在随后的说明书中阐述,并且,部分地可以从说明书中变得显而易见,或者通过实施本申请而了解。本申请的目的和其他优点可通过在所写的说明书、权利要求书、以及附图中特别指出的结构来实现和获得。

技术特征:

1.一种fpga开发板的防呆方法,其特征在于,包括:

2.如权利要求1所述的fpga开发板的防呆方法,其特征在于,所述获取目标文件所支持的fpga型号的步骤,包括:

3.如权利要求1所述的fpga开发板的防呆方法,其特征在于,所述获取所述目标fpga开发板的标识信息,包括:

4.如权利要求1所述的fpga开发板的防呆方法,其特征在于,确定目标文件与所述目标fpga开发板不匹配,禁止下载所述目标文件之后,还包括:

5.如权利要求1-4任一项所述的fpga开发板的防呆方法,其特征在于,所述获取目标文件所支持的fpga型号之前,还包括:

6.如权利要求5所述的fpga开发板的防呆方法,其特征在于,所述型号组与所述fpga开发板的型号一一对应,每个所述型号组中包括当前所有fpga开发板中对应型号的fpga开发板的标识信息。

7.一种fpga开发板的防呆装置,其特征在于,包括:

8.如权利要求7所述的fpga开发板的防呆装置,其特征在于,还包括:

9.一种电子设备,其特征在于,包括:存储器、处理器和存储在所述存储器上并可在所述处理器上运行的计算机程序,所述处理器执行所述计算机程序时实现如权利要求1-6任一项所述的fpga开发板的防呆方法。

10.一种计算机可读存储介质,其特征在于,所述计算机可读存储介质存储有计算机指令,所述计算机指令被处理器执行时实现如权利要求1-6任一项所述的fpga开发板的防呆方法。

技术总结

本申请公开了一种FPGA开发板的防呆方法、装置、设备及介质,应用于芯片验证技术领域,用以解决现有技术中存在的FPGA开发板和比特流文件匹配错误导致FPGA开发板损坏的问题。具体为:获取目标文件所支持的FPGA型号,并确定目标文件所支持的FPGA型号对应的型号组作为目标型号组;获取目标FPGA开发板的标识信息,并判断目标FPGA开发板的标识信息是否属于目标型号组;若是,则确定目标文件与目标FPGA开发板匹配,开始下载目标文件;若否,则确定目标文件与目标FPGA开发板不匹配,禁止下载目标文件。这样,可以避免FPGA开发板和比特流文件匹配错误导致FPGA开发板损坏的情况。

技术研发人员:张跃,李锡广,陈金霞

受保护的技术使用者:昆腾微电子股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!