一种SRAMPUF安全芯片

本发明涉及集成电路领域,特别是涉及一种sram puf安全芯片。

背景技术:

1、密码是保障信息安全的基础支撑。传统密码学利用非易失性存储器保存密钥,其安全性比较脆弱。已有许多可行的物理攻击手段,例如微探针、侧信道攻击等,使存储的密钥存在被窃取、被篡改的风险。

2、针对上述问题,物理不可克隆函数(physical unclonable function,puf)被认为是提高计算机系统安全性、抵抗物理攻击的有效手段。puf安全芯片利用了集成电路在生产制造过程中不可避免的随机工艺偏差,产生唯一的芯片标识符,作为“物理指纹”。由于生产制造过程中的工艺偏差一般无法进行人为控制,puf芯片的“物理指纹”具有不可预测且不易克隆的特点;此外,puf芯片的“物理指纹”具有上电可读、掉电即失的特性,进一步提升了其安全性;最后,puf芯片的“物理指纹”完全依赖于芯片本身的物理特性,因此无需额外的存储器来保存身份信息,这使得puf芯片具有低硬件成本的优点,有利于在资源稀缺的应用场景中实现轻量级的安全保护。puf芯片的上述优势使其能够在身份认证、信息加密、芯片水印等应用中提供固有、唯一的信任根,在硬件安全、物联网安全领域具有广阔的发展前景。

3、目前,以静态随机访问存储器(static random access memory,sram)为核心电路的sram puf是一种典型的puf安全芯片。sram puf利用了sram单元在上电时存储数据的随机性,并通过设置激励读取特定存储单元的上电初始值作为随机响应。sram puf具有较高的可靠性,能够在温度、供电电压等因素的影响下,提供相对稳定的响应输出。然而,srampuf所能支持的激励-响应关系数量有限,其激励-响应关系数量随sram单元数的增长仅呈线性增长的趋势,限制了sram puf的应用场景。

技术实现思路

1、基于此,本发明实施例提供一种sram puf安全芯片,能够在同等硬件资源的情况下,产生两倍数量的激励-响应关系,扩大sram puf的应用场景。

2、为实现上述目的,本发明实施例提供了如下方案:

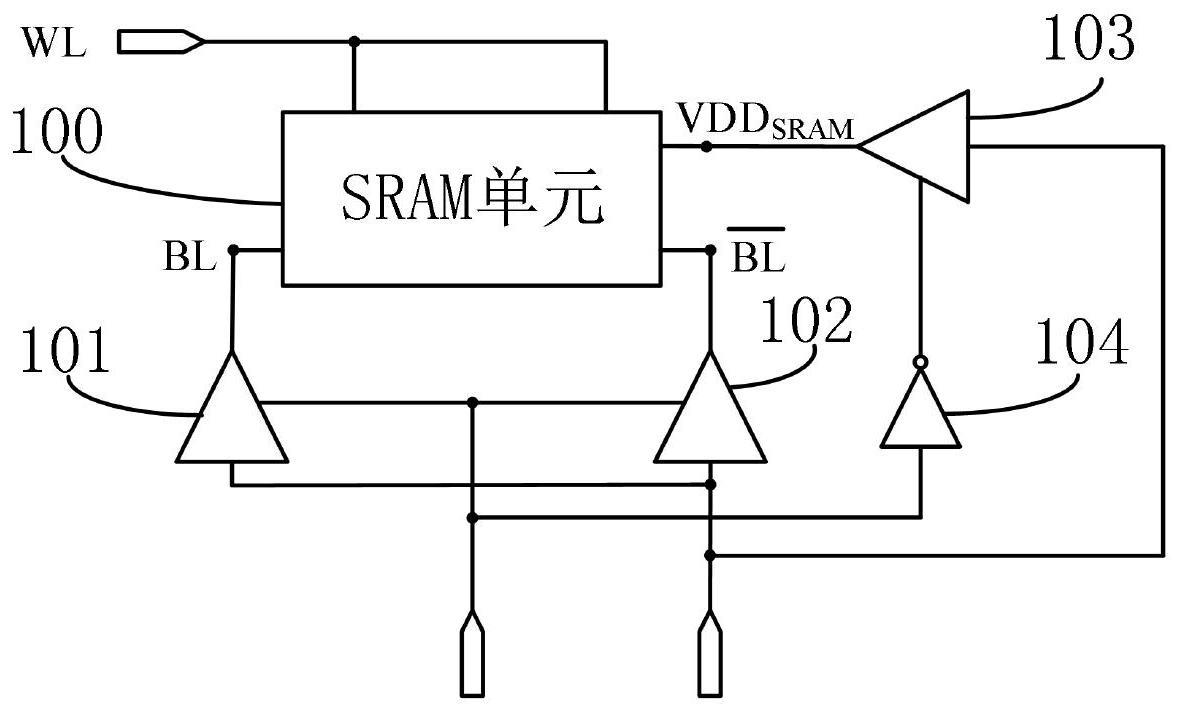

3、一种sram puf安全芯片,包括:sram单元和第一预充电控制电路;所述第一预充电控制电路,包括:第一三态门、第二三态门、第三三态门和第一非门;

4、所述第一三态门的输入端、所述第二三态门的输入端和所述第三三态门的输入端均与第一电源连接;所述第一三态门的控制端和所述第二三态门的控制端均与预充电使能信号连接;所述第一非门的输入端与所述预充电使能信号连接;所述第一非门的输出端与所述第三三态门的控制端连接;所述第一三态门的输出端与所述sram单元的位线连接;所述第二三态门的输出端与所述sram单元的取反位线连接;所述第三三态门的输出端与第二电源连接;所述第一电源作为安全芯片的电源;所述第二电源作为所述sram单元的电源。

5、可选地,所述sram单元,包括:锁存器单元、第一传输晶体管和第二传输晶体管;

6、所述第一传输晶体管的栅极和所述第二传输晶体管的栅极均与字线连接;所述第一传输晶体管的漏极与位线连接;所述第二传输晶体管的漏极与取反位线连接;

7、所述锁存器单元的第一输入端与所述第二电源连接;所述锁存器单元的第二输入端与所述第一传输晶体管的源极连接;所述锁存器单元的第三输入端与所述第二传输晶体管的源极与连接;所述第二输入端和所述第三输入端的逻辑电压值相反。

8、可选地,所述锁存器单元,包括:第一晶体管、第二晶体管、第三晶体管和第四晶体管;

9、所述第一晶体管和所述第三晶体管连接形成第二非门;所述第二晶体管和所述第四晶体管连接形成第三非门;所述第二非门的输入端与所述第三非门的输出端连接;所述第三非门的输入端与所述第二非门的输出端连接;所述第二非门的输入端作为所述锁存器单元的第二输入端;所述第三非门的输入端作为所述锁存器单元的第三输入端;所述第二非门和所述第三非门均与所述第二电源连接。

10、本发明还提供了一种sram puf安全芯片,包括:sram阵列和第二预充电电路;所述sram阵列,包括:2m行、n列的sram单元;所述第二预充电电路,包括:n个三态门单元、一个第四三态门和一个第四非门;

11、所述三态门单元,包括:第五三态门和第六三态门;一列sram单元对应连接一个三态门单元;

12、对于所述sram阵列中的第m行,第m列中的所有sram单元的字线连接形成一个字线连接端;1≤m≤2m;

13、对于所述sram阵列中的第n列,第n列中的所有sram单元的位线连接形成位线连接端,第n列中的所有sram单元的取反位线连接,形成取反位线连接端;第n个三态门单元中的第五三态门和第六三态门的控制端均与预充电使能信号连接;第n个三态门单元中的第五三态门和第六三态门的输入端均与第一电源连接;第n个三态门单元中的第五三态门的输出端与所述取位线连接端连接;第n个三态门单元中的第六三态门的输出端与所述取反位线连接端连接;1≤n≤n;

14、所述第四非门的输入端与所述预充电使能信号连接;所述第四非门的输出端与所述第四三态门的控制端连接;所述第四三态门的输入端与所述第一电源连接;所述第四三态门的输出端与第二电源连接;所述第一电源作为安全芯片的电源;所述第二电源作为所述sram单元的电源。

15、可选地,所述sram puf安全芯片,还包括:m位的地址译码器;

16、所述地址译码器的输出端与所有的字线连接端连接。

17、可选地,所述sram puf安全芯片,还包括:数据控制器;

18、所述数据控制器包括:n个输入输出双向接口;一个所述输入输出双向接口连接一个三态门单元。

19、根据本发明提供的具体实施例,本发明公开了以下技术效果:

20、本发明实施例提出的sram puf安全芯片,通过在芯片中加入预充电控制电路,从而在芯片上电时通过对其中的sram单元进行预充电控制,产生可变的激励-响应关系,提高其激励-响应关系的数量,本发明实施例利用对sram单元进行上电前预充电来产生可变的激励-响应关系,相较于传统的sram puf安全芯片,能够在同等硬件资源的情况下,产生两倍数量的激励-响应关系,从而扩大sram puf的应用场景。

技术特征:

1.一种sram puf安全芯片,其特征在于,包括:sram单元和第一预充电控制电路;所述第一预充电控制电路,包括:第一三态门、第二三态门、第三三态门和第一非门;

2.根据权利要求1所述的sram puf安全芯片,其特征在于,所述sram单元,包括:锁存器单元、第一传输晶体管和第二传输晶体管;

3.根据权利要求2所述的sram puf安全芯片,其特征在于,所述锁存器单元,包括:第一晶体管、第二晶体管、第三晶体管和第四晶体管;

4.一种sram puf安全芯片,其特征在于,包括:sram阵列和第二预充电电路;所述sram阵列,包括:2m行、n列的sram单元;所述第二预充电电路,包括:n个三态门单元、一个第四三态门和一个第四非门;

5.根据权利要求4所述的sram puf安全芯片,其特征在于,还包括:m位的地址译码器;

6.根据权利要求4所述的sram puf安全芯片,其特征在于,还包括:数据控制器;

技术总结

本发明公开了一种SRAM PUF安全芯片,涉及集成电路领域,该SRAM PUF安全芯片,包括:SRAM单元、第一三态门、第二三态门、第三三态门和第一非门;第一三态门、第二三态门和第三三态门的输入端均与安全芯片的电源连接;第一三态门和第二三态门的控制端均与预充电使能信号连接;第一非门的输入端与预充电使能信号连接;第一非门的输出端与第三三态门的控制端连接;第一三态门的输出端与SRAM单元的位线连接;第二三态门的输出端与SRAM单元的取反位线连接;第三三态门的输出端与SRAM单元的电源连接。本发明能够在同等硬件资源的情况下,产生两倍数量的激励‑响应关系,扩大SRAM PUF的应用场景。

技术研发人员:段圣宇,曹晨红,赛高乐

受保护的技术使用者:上海大学

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!