一种基于RISC-V的防止流水线冲刷系统的制作方法

本发明涉及高性能处理器内核架构,具体为一种基于risc-v的防止流水线冲刷系统。

背景技术:

1、早期的经典流水线是五级流水线,分别为取指、译码、执行、访存和写回。现代的处理器往往具有极深的流水线级数,譬如高达十几级,或者二十几级的深度。

2、现有技术中,流水线的级数越多,意味着流水线被切得越细,每一级流水线内容纳的硬件逻辑便越少。熟悉数字同步电路设计的读者应该比较熟悉,在两级寄存器之间的硬件逻辑越少,则意味能够运行到更高的主频。流水线的主频越高也就意味着流水线的吞吐率越高,从而性能越高,这就是流水线加深的正面意义。

3、但是,较深的处理器流水线有一个问题,那就是在流水线的取指令阶段无法得知条件跳转的结果是跳还是不跳,因此只能进行预测,而只有到了流水线的执行阶段才能知道到底是跳转还是不跳转。因此如果执行的结果与之前预测的结果不相符,那就说明会预测失败,就需要将所有预取的错误指令流全部丢弃掉,重新取指令,因此就会面临流水线的冲刷,如果流水线的深度越深,意味着已经预取了更多的错误指令,就更加增加了性能的损失。

技术实现思路

1、本发明的目的在于提供一种基于risc-v的防止流水线冲刷系统,以解决上述背景技术中提出的问题。

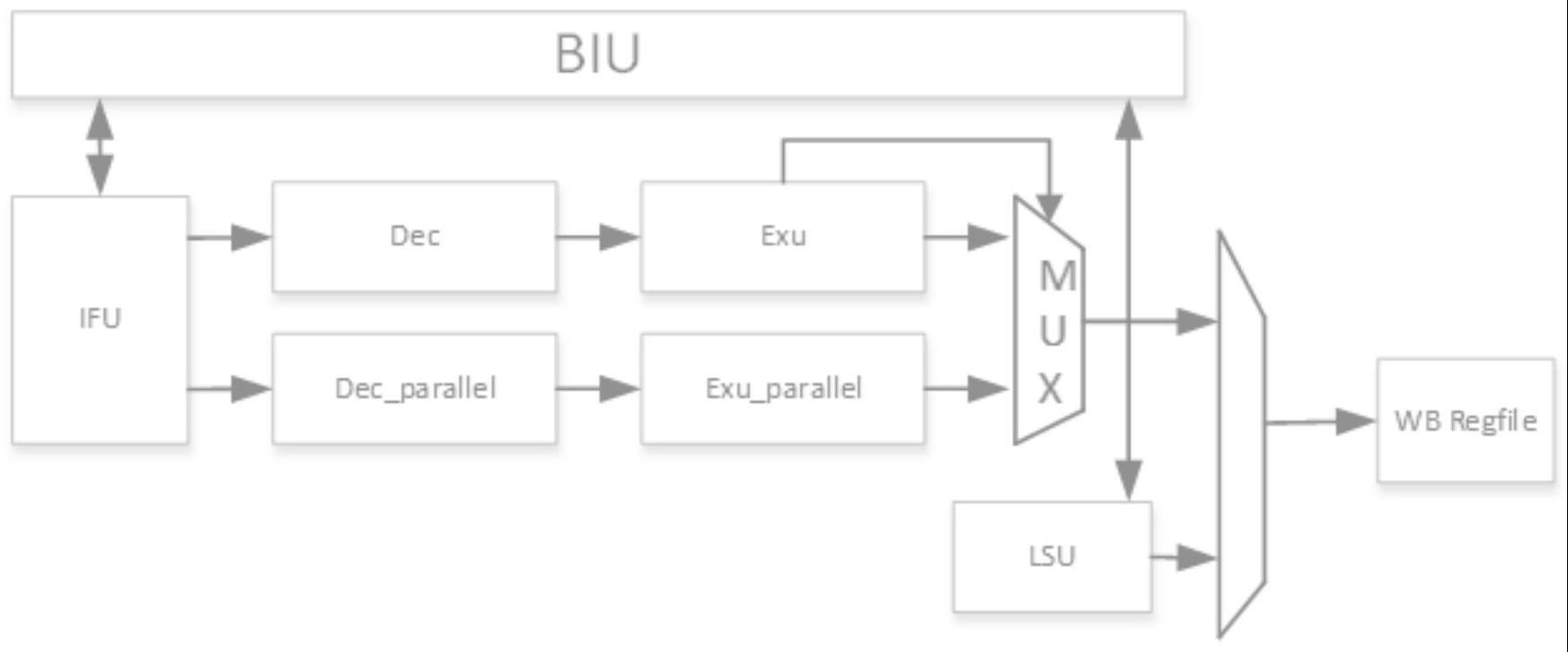

2、为实现上述目的,本发明提供如下技术方案:一种基于risc-v的防止流水线冲刷系统,所述系统由取指令单元、译码单元、执行单元一、访存单元、写回单元,以及并行的译码、执行单元二,以及双路译码器、整数通用寄存器和总线接口单元组成;

3、取指单元设有分支跳转判断逻辑,以及pc值累加器,取指单元会对取出的地址进行简单译码判断是哪种类型的指令,如果判断的是分支跳转指令,则取指单元里会产生两路pc值用于下一次的取指,译码单元得到指令需要的操作数寄存器索引,从通用寄存器组中将操作数读出,执行单元对得到的操作数进行执行,并判断是否需要跳转,双路译码器会根据分支跳转指令执行结果对两路执行单元的执行结果进行选择。

4、优选的,取指令单元包括:simple-decode模块、全局分支预测器、pc生成模块和icb总线控制模块、指令传输总线和指令高速缓存存储器。

5、优选的,sample-decode模块用于对取回的指令进行简单的译码;

6、全局分支预测器不会进行跳转方向预测,会采用btb技术进行跳转的地址预测;

7、pc生成模块根据分支预测的地址预测结果生成两个pc值;

8、icb总线控制模块,用于根据指令的pc值访问指令传输总线或总线接口单元;

9、指令传输总线,用于辅助指令传输;

10、指令高速缓存存储器,用于缓存多条指令。

11、优选的,执行单元包括:译码与派遣模块、滞外指令追踪先入先出缓存模块以及算术逻辑单元。

12、优选的,译码与派遣模块,用于对取指令单元发送来的指令进行译码并在读取操作数后将译码后的指令派遣到多个运算单元进行运算;

13、滞外指令追踪先入先出缓存模块,用于检测指令的相关性;

14、算术逻辑单元,用于根据指令进行运算。

15、优选的,所述双路译码器包括:执行结果译码模块,多路复用器,以及仲裁模块。

16、优选的,所述双路译码器模块包括:多路复用器,以及仲裁模块。接受执行单元的结果之后,对结果进行判断,判断是否需要跳转,将判断结果送给多路复用器,选择正确结果,再通过仲裁模块写回通用寄存器组里面。

17、与现有技术相比,本发明的有益效果是:

18、本发明提出的基于risc-v的防止流水线冲刷系统,取消了分支预测的方向预测,直接在取指阶段判断是否是分支跳转指令,并在下一次指令时将需要跳转的pc地址和不需要跳转的pc地址的指令同时取出,输送给并行的译码和执行单元,最终根据分支跳转指令执行的结果判断应该选取跳转的执行结果还是非跳转的执行结果,避免了传统的分支预测错误,预取了很多错误指令造成的处理器性能损失问题,而且仅对分支跳转指令进行判断,不是分支跳转指令会按传统的流水线方式进行。

技术特征:

1.一种基于risc-v的防止流水线冲刷系统,其特征在于:所述系统由取指令单元、译码单元、执行单元一、访存单元、写回单元,以及并行的译码、执行单元二,以及双路译码器、整数通用寄存器和总线接口单元组成;

2.根据权利要求1所述的一种基于risc-v的防止流水线冲刷系统,其特征在于:取指令单元包括:simple-decode模块、全局分支预测器、pc生成模块和icb总线控制模块、指令传输总线和指令高速缓存存储器。

3.根据权利要求2所述的一种基于risc-v的防止流水线冲刷系统,其特征在于:sample-decode模块用于对取回的指令进行简单的译码;

4.根据权利要求1所述的一种基于risc-v的防止流水线冲刷系统,其特征在于:执行单元包括:译码与派遣模块、滞外指令追踪先入先出缓存模块以及算术逻辑单元。

5.根据权利要求4所述的一种基于risc-v的防止流水线冲刷系统,其特征在于:译码与派遣模块,用于对取指令单元发送来的指令进行译码并在读取操作数后将译码后的指令派遣到多个运算单元进行运算;

6.根据权利要求1所述的一种基于risc-v的防止流水线冲刷系统,其特征在于:所述双路译码器包括:执行结果译码模块,多路复用器,以及仲裁模块。

7.根据权利要求6所述的一种基于risc-v的防止流水线冲刷系统,其特征在于:所述双路译码器模块包括:多路复用器,以及仲裁模块。接受执行单元的结果之后,对结果进行判断,判断是否需要跳转,将判断结果送给多路复用器,选择正确结果,再通过仲裁模块写回通用寄存器组里面。

技术总结

本发明涉及高性能处理器内核架构技术领域,具体为一种基于RISC‑V的防止流水线冲刷系统,系统由取指令单元、译码单元、执行单元一、访存单元、写回单元,以及并行的译码、执行单元二,以及双路译码器、整数通用寄存器和总线接口单元组成;有益效果为:本发明提出的基于RISC‑V的防止流水线冲刷系统,取消了分支预测的方向预测,直接在取指阶段判断是否是分支跳转指令,并在下一次指令时将需要跳转的PC地址和不需要跳转的PC地址的指令同时取出,输送给并行的译码和执行单元,最终根据分支跳转指令执行的结果判断应该选取跳转的执行结果还是非跳转的执行结果,避免了传统的分支预测错误,预取了很多错误指令造成的处理器性能损失问题。

技术研发人员:许桂龙,赵鑫鑫,姜凯,李锐

受保护的技术使用者:山东浪潮科学研究院有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!