处理器、计算芯片和计算设备的制作方法

本发明涉及计算机领域。具体而言,本发明涉及一种处理器以及包括该处理器的计算芯片和计算设备,特别适用于神经网络相关的计算。

背景技术:

1、在神经网络相关的应用场景中,通常需要利用处理器进行大量运算。处理器的运算效率、功耗、面积等对于整个计算设备的效率和成本至关重要。期望实现一种高效率、低功耗的处理器,从而提高计算效率,降低生产成本和运行成本。

2、因此,存在对于新技术的需求。

技术实现思路

1、本公开的目的之一是提供一种改进的处理器。

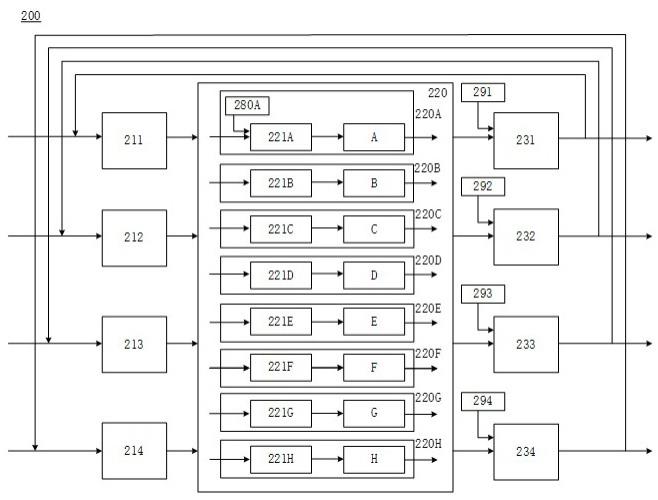

2、根据本发明的一个方面,提供了一种处理器,其包括:n个寄存器;算术逻辑单元,包括多个算术逻辑子单元,每个算术逻辑子单元用于执行一种运算,并且每个算术逻辑子单元的输入耦接到n个寄存器的输出;以及n个多路复用器,每个多路复用器的输入耦接到算术逻辑单元的每一个算术逻辑子单元的输出,并且每个多路复用器根据该多路复用器的控制信号选择对应的一个算术逻辑子单元的输出,其中,每个算术逻辑子单元包括:选择模块,耦接到n个寄存器的输出,用于根据该算术逻辑子单元的控制信号选择对应的一个寄存器的输出并将其传递到运算模块,或者不选择任何一个寄存器的输出并将表示不选择任何一个寄存器的输出的预定值传递到运算模块;以及运算模块,用于针对选择模块传递的寄存器的输出来进行运算,其中,n是大于或等于2且小于或等于算术逻辑子单元的数量的整数。

3、根据本发明的另一个方面,提供了一种计算芯片,其包括一个或多个上述处理器。

4、根据本发明的又一个方面,提供了一种计算设备,其包括一个或多个上述计算芯片。

5、根据参照附图的以下描述,本发明的其它特性特征和优点将变得清晰。

技术特征:

1.一种处理器,包括:

2.如权利要求1所述的处理器,其中第1至n个多路复用器的输出分别耦接到第1至n个寄存器的输入,同时耦接到处理器的输出。

3.如权利要求2所述的处理器,其中第1至n个多路复用器的控制信号分别选择与第1至n个寄存器对应的算术逻辑子单元的输出。

4.如权利要求1所述的处理器,其中第1至n-1个多路复用器的输出分别耦接到第2至n个寄存器的输入,并且第n个多路复用器的输出耦接到处理器的输出。

5.如权利要求4所述的处理器,其中第1至n个多路复用器的控制信号分别选择与第1至n个寄存器对应的算术逻辑子单元的输出。

6.如权利要求2所述的处理器,其中第2至n个多路复用器的控制信号分别选择与第1至n-1个寄存器对应的算术逻辑子单元的输出,并且第1个多路复用器的控制信号选择与第n个寄存器对应的算术逻辑子单元的输出。

7.如权利要求1-6中任一项所述的处理器,其中表示不选择任何一个寄存器的输出的所述预定值为零。

8.如权利要求1-6中任一项所述的处理器,其中每个算术逻辑子单元的控制信号包括n个值,分别对应于n个寄存器。

9.如权利要求8所述的处理器,其中每个算术逻辑子单元的选择模块包括:

10.如权利要求8所述的处理器,其中每个算术逻辑子单元的选择模块包括:

11.如权利要求1-6中任一项所述的处理器,其中每个多路复用器由逻辑门器件实现。

12.如权利要求1-6中任一项所述的处理器,其中n为4。

13.如权利要求1-6中任一项所述的处理器,其中多个算术逻辑子单元中的每一个用于进行以下运算中的一者:加、减、乘、除、移位、截断、求倒数、取模。

14.一种计算芯片,包括一个或多个如权利要求1-13中任一项所述的处理器。

15.一种计算设备,包括一个或多个如权利要求14所述的计算芯片。

技术总结

本公开涉及处理器、计算芯片和计算设备。公开了一种处理器,其包括:N个寄存器;算术逻辑单元,包括多个算术逻辑子单元,每个算术逻辑子单元执行一种运算,其输入耦接到N个寄存器的输出;以及N个多路复用器,每个多路复用器的输入耦接到每个算术逻辑子单元的输出,每个多路复用器根据控制信号选择对应的一个算术逻辑子单元的输出,每个算术逻辑子单元包括:选择模块,耦接到N个寄存器的输出,根据控制信号选择对应的一个寄存器的输出并将其传递到运算模块,或者不选择任何一个寄存器的输出并将预定值传递到运算模块;以及运算模块,针对选择模块传递的寄存器的输出进行运算,其中,N是大于或等于2且小于或等于算术逻辑子单元的数量的整数。

技术研发人员:王丹阳,翟云,范志军,杨作兴

受保护的技术使用者:深圳比特微电子科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!