一种指令执行结果写入装置、方法、设备及存储介质与流程

本发明涉及处理器内核架构,特别涉及一种指令执行结果写入装置、方法、设备及存储介质。

背景技术:

1、随着科技的发展,人们对计算机处理速度的要求越来越高。为了提高微处理器的性能,人们提出了超标量流水线技术。超标量技术是指cpu(central processing unit,即中央处理器)在每个时钟周期内可以完成一条以上指令的并行执行技术。实现多指令并行执行的关键在于乱序执行。乱序执行是指不按照指令原始顺序执行的技术。而实现指令乱序执行的关键是用到了寄存器重命名技术。寄存器重命名是用一个或者多个虚拟寄存器来代替真实的数据寄存器的硬件猜测方法。重排序缓冲器(rob,即reorder buffer)是超标量处理器中基于寄存器重命名技术的一种实现结构,在系列处理器中得到了广泛的应用。

2、传统的cpu的rob通常以允许多端口同时读写的寄存器堆的方式实现,一个n指令发射的超标量处理器的流水线中,至少需要2n个读端口,以及n个写端口,这样能保证n条指令在一个时钟周期内将2个指令执行的操作数从rob读出来或者将指令的执行结果写入rob中。但这样的多端口寄存器堆会增加设计的复杂度,带来时序变差以及面积变大等影响。因此,如何降低设计的复杂度的同时仍然实现在一个时钟周期内将2个指令执行的操作数是需要解决的。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种指令执行结果写入装置、方法、设备及存储介质,能够在减少重排序缓存单元端口数量的同时,仍可以实现同时读写指令处理结果的效果。其具体方案如下:

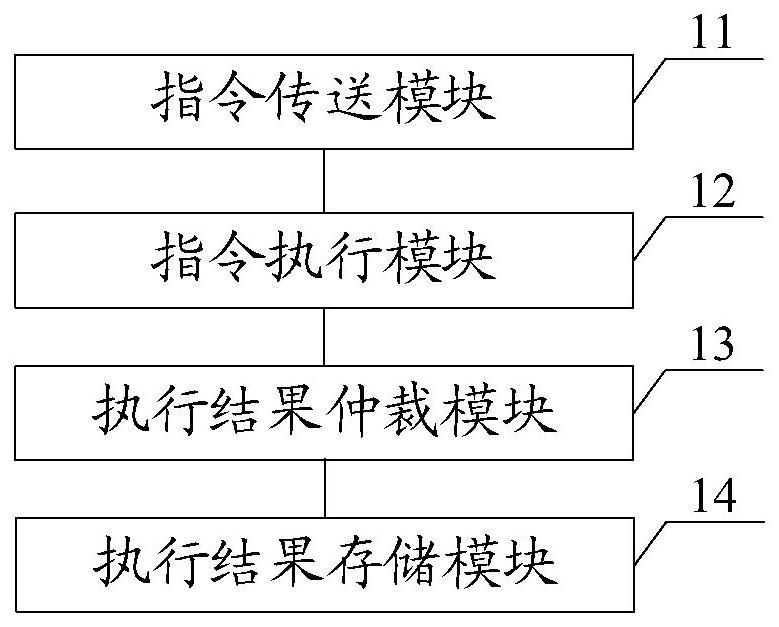

2、第一方面,本申请公开了一种指令执行结果写入装置,包括:

3、指令传送模块,用于对获取的各待执行指令进行编译以得到对应的编译后指令,并将各所述编译后指令发送至预设指令发射队列;

4、指令执行模块,用于通过若干个指令执行工具获取所述预设指令发射队列发送的所述编译后指令进行执行以生成对应的执行结果;

5、执行结果仲裁模块,用于基于各所述执行结果之间的数据相关性将各所述执行结果分别分配至对应的预设重排序缓存单元中;

6、执行结果存储模块,用于从所述预设重排序缓存单元读取各所述执行结果,并通过预设写回仲裁工具将各所述执行结果写入至本地寄存器组中。

7、可选的,所述指令传送模块,包括:

8、指令译码单元,用于根据获取的待执行指令的执行顺序对所述待执行指令标记对应的标识号,以得到编译后指令,并将所述编译后指令发送至预设指令发射队列中。

9、可选的,所述指令执行结果写入装置,还包括:

10、执行结果译码单元,用于基于与所述执行结果对应的所述编译后指令的指令标识号对所述执行结果进行标记,以使标记后得到的所述执行结果的结果标识号与所述指令标识号相一致。

11、可选的,所述执行结果存储模块,包括:

12、结果顺序存储单元,用于从所述预设重排序缓存单元读取各所述执行结果,并基于预设写回仲裁工具和各所述执行结果的结果标识号将各所述执行结果写入至本地寄存器组中。

13、可选的,所述执行结果仲裁模块,包括:

14、执行结果判断子模块,用于判断将各所述执行结果之间是否存在数据相关性;

15、第一结果分配子模块,用于将存在数据相关性的各所述执行结果分配至不同的预设重排序缓存单元中;

16、第二结果分配子模块,用于将不存在数据相关性的各所述执行结果分配至不同或相同的预设重排序缓存单元中。

17、可选的,所述执行结果判断子模块,包括:

18、结果标识号判断单元,用于判断各所述执行结果之间的结果标识号是否相邻;

19、相应的,所述第一结果分配子模块,包括:

20、第一结果分配单元,用于将结果标识号相邻的各所述执行结果分配至不同的预设重排序缓存单元中;

21、所述第二结果分配子模块,包括:

22、第二结果分配单元,用于将结果标识号不相邻的各所述执行结果分配至不同或相同的预设重排序缓存单元中。

23、可选的,所述执行结果仲裁模块,还包括:

24、执行结果读取单元,用于从所述预设重排序缓存单元中读取所述编译后指令执行所需的执行数据;其中,所述执行数据为其他编译后指令的执行结果;

25、执行结果传递单元,用于将所述执行数据传递至所述编译后指令对应的指令执行工具中。

26、第二方面,本申请公开了一种指令执行结果写入方法,包括:

27、对获取的各待执行指令进行编译以得到对应的编译后指令,并将各所述编译后指令发送至预设指令发射队列中;

28、通过若干个指令执行工具获取所述预设指令发射队列发送的所述编译后指令进行执行以生成对应的执行结果;

29、基于各所述执行结果之间的数据相关性将各所述执行结果分别分配至对应的预设重排序缓存单元中;

30、从所述预设重排序缓存单元读取各所述执行结果,并通过预设写回仲裁工具将各所述执行结果写入至本地寄存器组中。

31、第三方面,本申请公开了一种电子设备,包括:

32、存储器,用于保存计算机程序;

33、处理器,用于执行所述计算机程序以实现前述的指令执行结果写入方法。

34、第四方面,本申请公开了一种计算机可读存储介质,用于保存计算机程序,所述计算机程序被处理器执行时实现前述的指令执行结果写入方法。

35、可见,本申请中,指令传送模块,用于对获取的各待执行指令进行编译以得到对应的编译后指令,并将各所述编译后指令发送至预设指令发射队列;指令执行模块,用于通过若干个指令执行工具获取所述预设指令发射队列发送的所述编译后指令进行执行以生成对应的执行结果;执行结果仲裁模块,用于基于各所述执行结果之间的数据相关性将各所述执行结果分别分配至对应的预设重排序缓存单元中;执行结果存储模块,用于从所述预设重排序缓存单元读取各所述执行结果,并通过预设写回仲裁工具将各所述执行结果写入至本地寄存器组中。通过基于各执行结果之间的数据相关性,将所述各执行结果分别分配至对应的预设重排序缓存单元中,从而可以实现在一个时钟周期内将两个或两个以上的指令执行的操作数从rob读出来或者将指令的执行结果写入rob中,这样一来,针对一个n指令发射的超标量处理器的流水线中,至少需要2n个读端口,以及n个写端口的rob可以只需要n个读端口,以及n个写端口即可实现n条指令在一个时钟周期内将2个指令执行的操作数从rob读出来或者将指令的执行结果写入rob中。这样通过减少寄存器堆中的端口数,大大降低了寄存器堆设计的复杂度。

技术特征:

1.一种指令执行结果写入装置,其特征在于,包括:

2.根据权利要求1所述的指令执行结果写入装置,其特征在于,所述指令传送模块,包括:

3.根据权利要求2所述的指令执行结果写入装置,其特征在于,还包括:

4.根据权利要求3所述的指令执行结果写入装置,其特征在于,所述执行结果存储模块,包括:

5.根据权利要求2所述的指令执行结果写入装置,其特征在于,所述执行结果仲裁模块,包括:

6.根据权利要求5所述的指令执行结果写入装置,其特征在于,所述执行结果判断子模块,包括:

7.根据权利要求1至6任一项所述的指令执行结果写入装置,其特征在于,所述执行结果仲裁模块,还包括:

8.一种指令执行结果写入方法,其特征在于,包括:

9.一种电子设备,其特征在于,包括:

10.一种计算机可读存储介质,其特征在于,用于保存计算机程序,所述计算机程序被处理器执行时实现如权利要求8所述的指令执行结果写入方法。

技术总结

本申请公开了一种指令执行结果写入装置、方法、设备及存储介质,涉及处理器内核架构技术领域,包括:指令传送模块,用于对获取的各待执行指令进行编译以得到对应的编译后指令,并将各所述编译后指令发送至预设指令发射队列;指令执行模块,用于通过若干个指令执行工具获取所述编译后指令进行执行以生成对应的执行结果;执行结果仲裁模块,用于基于各所述执行结果之间的数据相关性将各所述执行结果分别分配至对应的预设重排序缓存单元中;执行结果存储模块,用于读取各所述执行结果,并通过预设写回仲裁工具将各所述执行结果写入至本地寄存器组中。这样一来,可以在减少重排序缓存单元端口数量的同时,仍可以实现同时读写指令处理结果的效果。

技术研发人员:许桂龙,赵鑫鑫,姜凯

受保护的技术使用者:山东浪潮科学研究院有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!