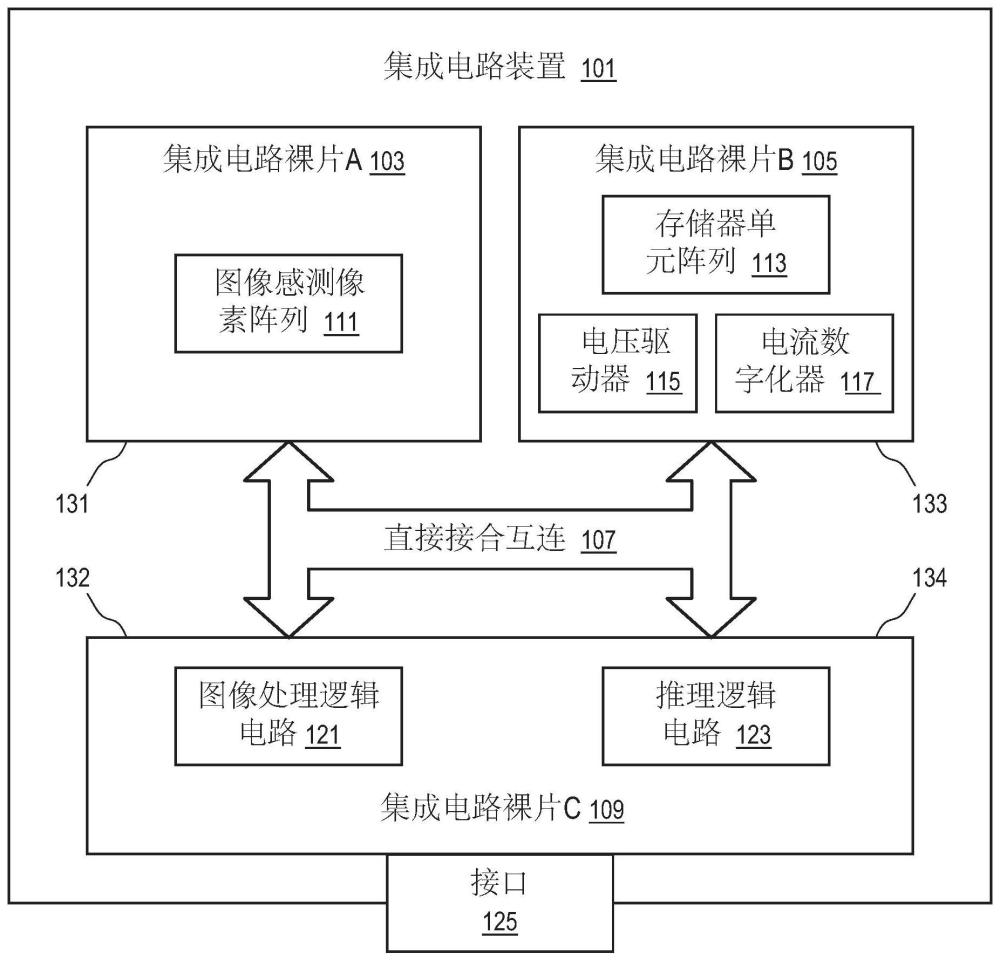

使用具有模拟推理能力的集成电路装置的冗余计算的制作方法

本文公开的至少一些实施例大体上涉及冗余计算,且更特定来说涉及(但不限于)使用乘法及累加电路执行的计算。

背景技术:

1、图像传感器可产生大量数据。将图像数据从图像传感器传输到通用微处理器(例如,中央处理单元(cpu))用于一些应用的处理是低效的,例如图像分割、对象辨识、特征提取等。

2、一些图像处理可包含涉及用于累加的元素的列或矩阵的乘法的密集计算。已开发一些专用电路来加速乘法及累加运算。例如,可使用一组并联计算逻辑电路来实施乘法器-累加器(mac单元),以实现比通用微处理器更高的计算性能。例如,可使用忆阻器交叉开关来实施乘法器-累加器(mac单元)。

技术实现思路

1、根据本公开的实施例,提供一种装置。所述装置包括:存储器单元阵列,其中所述存储器单元阵列中的每一相应存储器单元具有阈值电压,其能以第一模式编程以执行乘法及累加运算,且能以与所述第一模式不同的第二模式编程以存储数据;及逻辑电路;其中所述存储器单元阵列具有能并行操作以执行乘法及累加的冗余运算的多个区;且其中所述逻辑电路经配置以比较从分别使用所述多个区执行的所述乘法及累加的冗余运算产生的多个结果,以从所述多个结果选择输出结果。

技术特征:

1.一种装置,其包括:

2.根据权利要求1所述的装置,其中所述多个区中的存储器单元以所述第一模式进行编程,以分别存储权重数据的多个冗余副本;且所述逻辑电路经配置以响应于彼此不同的所述多个结果而将至少一个区标识为具有损坏权重编程。

3.根据权利要求2所述的装置,其中当以所述第一模式编程且施加预定读取电压时,所述相应存储器单元经配置以输出:

4.根据权利要求3所述的装置,其中所述存储器单元阵列中的所述相应存储器单元经配置以当以所述第一模式编程时每单元存储一个位,且当以所述第二模式编程时每单元存储多于一个位。

5.根据权利要求4所述的装置,其中所述逻辑电路经配置以将具有连接到所述至少一个区中的位线中的输出电流的存储器单元的列标识为具有损坏权重编程。

6.根据权利要求4所述的装置,其中所述逻辑电路经配置以将具有连接到所述至少一个区中的位线的子集中的输出电流的存储器单元的列的子集标识为具有损坏权重编程。

7.根据权利要求4所述的装置,其中所述存储器单元阵列经配置为多个层,所述层中的每一者具有拥有分别连接到多个位线的输出电流的存储器单元的多个列,所述层中的每一者具有分别连接到字线以接收所施加电压的存储器单元的行。

8.根据权利要求7所述的装置,其中所述层中的每一者具有字线,所述字线是根据输入位的列来选择以具有同时施加的所述预定读取电压用于逐位乘法以将电流输出到所述位线中;且所述装置进一步包括模/数转换器,其经配置以将所述位线中的求和电流数字化为所述预定量的电流的倍数。

9.根据权利要求8所述的装置,其中所述多个区中的每一相应区配置在与由除所述相应区外的所述多个区使用的层分离的一组一或多个层中。

10.根据权利要求8所述的装置,其中所述多个区配置在由所述多个区共享的一或多个层的不同区段中。

技术总结

本申请的实施例涉及使用具有模拟推理能力的集成电路装置的冗余计算。一种装置,其配置有冗余计算以改进使用存储器单元来执行乘法及累加运算的可靠性。所述装置能具有存储器单元阵列及逻辑电路。所述存储器单元阵列中的每一相应存储器单元具有阈值电压,其能以第一模式编程以执行乘法及累加运算,且能以与所述第一模式不同的第二模式编程以存储数据。所述存储器单元阵列具有能并行操作以执行乘法及累加的冗余运算的多个区。所述逻辑电路经配置以比较从分别使用所述多个区执行的乘法及累加的冗余运算产生的多个结果,以从所述多个结果选择输出结果。

技术研发人员:P·卡利

受保护的技术使用者:美光科技公司

技术研发日:

技术公布日:2024/3/11

- 还没有人留言评论。精彩留言会获得点赞!