一种芯片封装设计中获取走线伴随区域的方法与流程

本申请涉及芯片封装,具体涉及一种芯片封装设计中获取走线伴随区域的方法。

背景技术:

1、高速芯片封装设计时对信号质量和性能要求较高,因此为了避免高速信号之间的相互干扰,在进行高速芯片的封装设计时,需要使高速信号伴随地或伴随电源走线,高速信号伴随走线时需要为走线周围的模块预留出伴随区域,而高速芯片封装设计中走线数量多,为节省空间,要求走线周围的模块之间的铜皮(还可以称为shpae或者trace)设置为工艺要求的最小铜皮,较大的铜皮不能满足高速芯片的封装设计要求。

2、目前想要在两个模块之间实现高速信号的伴随地或伴随电源走线,只能通过芯片封装设计工具微调两个模块的位置以修改模块之间的铜皮宽度,然后测量模块之间的铜皮宽度,重复该步骤直至模块之间的铜皮宽度满足了高速芯片的封装设计要求,这种方式的缺点在于:一方面,需要人工手动操作,不能快速完成模块之间的铜皮的铺设;另一方面,人工调整过程不能精准控制模块之间的铜皮宽度,且失误的概率大,如调整过程中可能会因为设置模块的间距过小导致模块之间的铜皮消失,需要再次拉大模块之间的距离,重新测量模块之间的铜皮宽度,进一步浪费了芯片封装设计的大量时间,降低了芯片封装设计的效率。

技术实现思路

1、鉴于以上问题,本申请提供一种芯片封装设计中获取走线伴随区域的方法,以解决上述技术问题。

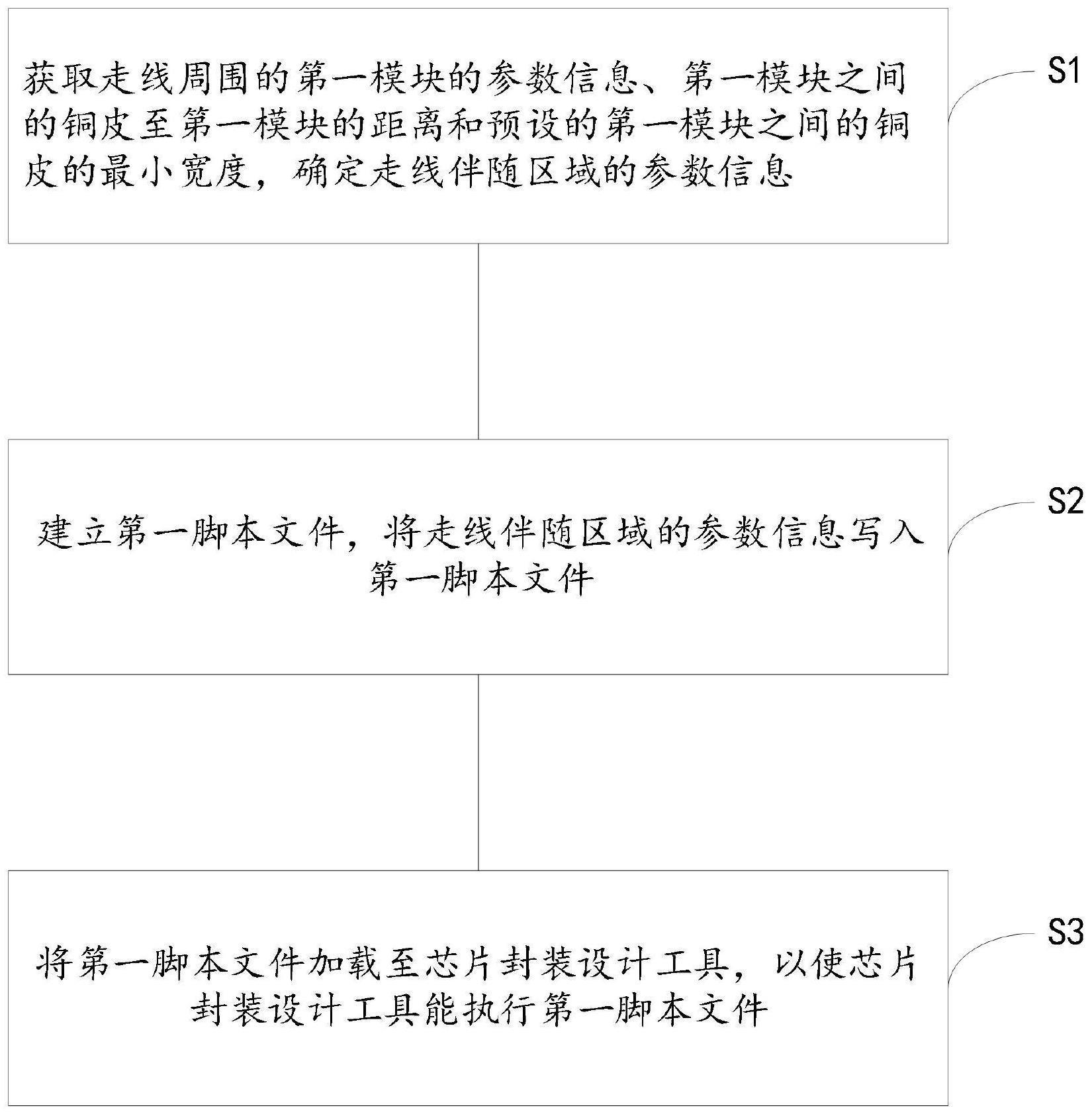

2、本申请提供的一种芯片封装设计中获取走线伴随区域的方法,包括:

3、获取走线周围的第一模块的参数信息、所述第一模块之间的铜皮至第一模块的距离和预设的所述第一模块之间的铜皮的最小宽度,确定走线伴随区域的参数信息;

4、建立第一脚本文件,将所述走线伴随区域的参数信息写入所述第一脚本文件;

5、将所述第一脚本文件加载至芯片封装设计工具,以使所述芯片封装设计工具能执行所述第一脚本文件。

6、在一些实施例中,本申请提供的一种芯片封装设计中获取走线伴随区域的方法中,所述第一模块包括芯片封装设计中的金手指或者过孔或者管脚;

7、所述第一模块为所述金手指,所述第一模块的参数信息包括所述金手指的长度和所述金手指的宽度;

8、所述第一模块为所述过孔,所述第一模块的参数信息包括所述过孔的直径;

9、所述第一模块为所述管脚,所述第一模块的参数信息包括所述管脚的直径。

10、在一些实施例中,本申请提供的一种芯片封装设计中获取走线伴随区域的方法中,所述第一模块的参数信息和所述第一模块之间的铜皮至第一模块的距离通过芯片封装设计工具导出。

11、在一些实施例中,本申请提供的一种芯片封装设计中获取走线伴随区域的方法中,确定走线伴随区域的参数信息,包括:

12、确定所述第一模块至所述走线伴随区域边界的距离,所述第一模块至所述走线伴随区域边界的距离为:第一模块之间的铜皮至第一模块的距离的一倍与所述第一模块之间的铜皮的最小宽度之和。

13、在一些实施例中,本申请提供的一种芯片封装设计中获取走线伴随区域的方法中,所述将所述第一脚本文件加载至芯片封装设计工具,以使所述芯片封装设计工具能执行所述第一脚本文件,包括:

14、将所述第一脚本文件存储至所述芯片封装设计工具的根目录;

15、通过所述芯片封装设计工具执行第一命令,所述第一命令用于加载脚本文件。

16、在一些实施例中,本申请提供的一种芯片封装设计中获取走线伴随区域的方法中,所述将所述第一脚本文件加载至芯片封装设计工具,以使所述芯片封装设计工具能执行所述第一脚本文件,还包括:

17、通过所述芯片封装设计工具新建第二命令,将所述第二命令与所述第一脚本文件关联,所述第二命令区别于所述芯片封装设计工具现有的命令。

18、在一些实施例中,本申请提供的一种芯片封装设计中获取走线伴随区域的方法中,所述第一脚本文件的内容通过sql语言描述。

19、本申请提供的一种芯片封装设计中获取走线伴随区域的方法,包括获取走线周围的第一模块的参数信息、所述第一模块之间的铜皮至第一模块的距离和预设的所述第一模块之间的铜皮的最小宽度,确定走线伴随区域的参数信息;建立第一脚本文件,将所述走线伴随区域的参数信息写入所述第一脚本文件;将所述第一脚本文件加载至芯片封装设计工具,以使所述芯片封装设计工具能执行所述第一脚本文件。本申请使用第一脚本文件获取走线伴随区域,避免了芯片封装设计工程师为满足信号质量及工艺要求反复修正走线伴随区域的操作,提高了芯片封装设计效率。

技术特征:

1.一种芯片封装设计中获取走线伴随区域的方法,其特征在于,包括:

2.如权利要求1所述的一种芯片封装设计中获取走线伴随区域的方法,其特征在于,所述第一模块包括芯片封装设计中的金手指或者过孔或者管脚;

3.如权利要求1所述的一种芯片封装设计中获取走线伴随区域的方法,其特征在于,

4.如权利要求1所述的一种芯片封装设计中获取走线伴随区域的方法,其特征在于,确定走线伴随区域的参数信息,包括:

5.如权利要求1所述的一种芯片封装设计中获取走线伴随区域的方法,其特征在于,所述将所述第一脚本文件加载至芯片封装设计工具,以使所述芯片封装设计工具能执行所述第一脚本文件,包括:

6.如权利要求5所述的一种芯片封装设计中获取走线伴随区域的方法,其特征在于,所述将所述第一脚本文件加载至芯片封装设计工具,以使所述芯片封装设计工具能执行所述第一脚本文件,还包括:

7.如权利要求1所述的一种芯片封装设计中获取走线伴随区域的方法,其特征在于,所述第一脚本文件通过sql程序语言描述。

技术总结

本申请属于芯片封装技术领域,公开了一种芯片封装设计中获取走线伴随区域的方法。该方法包括:获取走线周围的第一模块的参数信息、所述第一模块之间的铜皮至第一模块的距离和预设的所述第一模块之间的铜皮的最小宽度,确定走线伴随区域的参数信息;建立第一脚本文件,将所述走线伴随区域的参数信息写入所述第一脚本文件;将所述第一脚本文件加载至芯片封装设计工具,以使所述芯片封装设计工具能执行所述第一脚本文件。本申请提供的芯片封装设计中获取走线伴随区域的方法,使用第一脚本文件获取走线伴随区域,避免了芯片封装设计工程师为满足信号质量及工艺要求而反复手动修正走线伴随区域的操作,提高了芯片封装设计效率。

技术研发人员:张利丹,冯杰,夏君

受保护的技术使用者:深圳市紫光同创电子有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!