快闪存储器装置、快闪存储器控制器及快闪存储器控制器的方法与流程

本发明有关于一种储存装置,尤指一种快闪存储器控制器、快闪存储器装置及相应的方法。

背景技术:

1、一般来说,为了将一或多个数据部分写入至快闪存储器装置的一实体页面单元,传统的快闪存储器控制器需要产生一或多个适当的虚拟数据部分以形成一个整页数据,并将该整页数据从传统的快闪存储器控制器传送到快闪存储器装置。类似地,为了从快闪存储器装置的一实体页面单元读取出一或多个数据部分,传统的快闪存储器控制器也需要从快闪存储器装置接收包括有一或多个数据部分与一或多个虚拟数据部分的一个整页数据。也就是说,一或多个虚拟数据部分的数据内容和大小赱是由传统快闪存储器控制器所决定及所产生的,因此传统快闪存储器控制器和快闪存储器装置之间的大量的数据传输量是无法被有效地降低的,因而传统快闪存储器控制器的性能是受限的。

技术实现思路

1、因此本发明的目的之一在于提供一种储存装置,尤其是一种快闪存储器控制器、快闪存储器装置及相应的方法,以解决上述问题。

2、根据本发明的实施例,揭露了一种快闪存储器控制器。快闪存储器控制器用于一储存装置并通过一特定通信接口耦接于该储存装置的一快闪存储器装置,以及该快闪存储器控制器包括一输入/输出电路与一处理器。输入/输出电路通过该特定通信接口耦接到该快闪存储器装置,并用于在该快闪存储器装置和一处理器之间发送多个命令和数据。该处理器耦接于该输入/输出电路,并用于控制该输入/输出电路使用一设定特征信号并传送该设定特征信号至该快闪存储器装置,该设定特征信号携带一设定特征命令、一特征地址及一相应的参数资讯。该特征地址对应于一有效数据部分或该有效数据部分之后的一虚拟数据部分,该有效数据部分和该虚拟数据部分均被包含在一整页数据中,该整页数据要被写入至该快闪存储器装置的一实体页面单元中或要被从该实体页面单元中所读取出。该相应的参数资讯被用于记录该有效数据部分的一行地址和一数据长度、用于记录该虚拟数据部分的一行地址和一数据长度、用于记录该虚拟数据部分的该行地址和该有效数据部分的该行地址或者用于记录该虚拟数据部分的该数据长度和该有效数据部分的该数据长度。

3、根据实施例,揭露了一种快闪存储器控制器的方法。该快闪存储器控制器使用于一储存装置中并通过一特定通信接口耦接到该储存装置的一快闪存储器装置。该方法包括:提供一输入/输出电路通过该特定通信接口耦接到该快闪存储器装置,以在该快闪存储器装置和一处理器之间发送多个命令和数据;以及控制该输入/输出电路使用一设定特征信号并传送该设定特征信号至该快闪存储器装置,该设定特征信号携带一设定特征命令、一特征地址及一相应的参数资讯;该特征地址对应于一有效数据部分或该有效数据部分之后的一虚拟数据部分,该有效数据部分和该虚拟数据部分均被包含在一整页数据中,该整页数据要被写入至该快闪存储器装置的一实体页面单元中或要被从该实体页面单元中所读取出;该相应的参数资讯被用于记录该有效数据部分的一行地址和一数据长度、用于记录该虚拟数据部分的一行地址和一数据长度、用于记录该虚拟数据部分的该行地址和该有效数据部分的该行地址或者用于记录该虚拟数据部分的该数据长度和该有效数据部分的该数据长度。

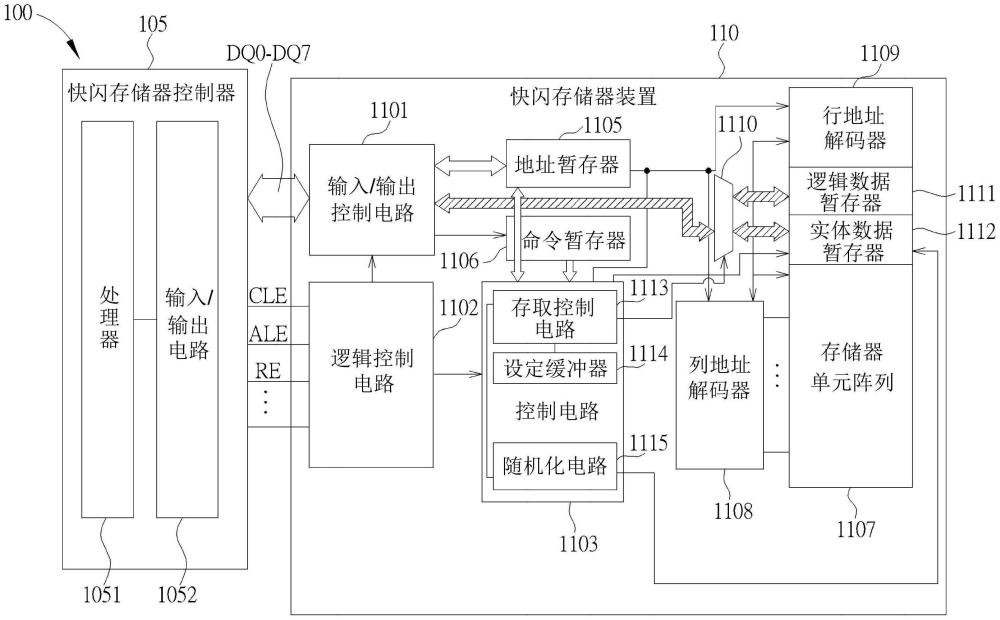

4、根据实施例,揭露了一种快闪存储器装置。该快闪存储器装置用于一储存装置并通过一特定通信接口连接到该储存装置的一快闪存储器控制器,该快闪存储器装置包括一输入/输出控制电路、一命令暂存器、一地址暂存器、一存储器单元阵列、一实体数据暂存器、一逻辑数据暂存器、一多工器以及一控制电路。输入/输出控制电路通过该特定通信接口耦接于该快闪存储器控制器。命令暂存器耦接该输入/输出控制电路,并用以缓冲该快闪存储器控制器所发送并通过该输入/输出控制电路所传送的一读取命令。地址暂存器耦接该输入/输出控制电路,并用于缓冲该快闪存储器控制器所发送并通过该输入/输出控制电路所传送的一地址资讯。存储器单元阵列至少具有一实体页面单元。实体数据暂存器耦接到该存储器单元阵列。逻辑数据暂存器耦接到该实体数据暂存器。多工器耦接该实体数据暂存器、该逻辑数据暂存器以及该输入/输出控制电路。控制电路耦接到该存储器单元阵列、该实体数据暂存器、该逻辑数据暂存器和该多工器,并用以:因应于该读取命令和所缓冲的该地址资讯,控制该实体页面单元从该存储器单元阵列的该实体页面单元传输一整页数据到该实体数据暂存器;控制该实体数据暂存器传送该整页数据中的至少一有效数据部分而不将该整页数据中的多个其他剩余数据部分从该实体数据暂存器传送到该逻辑数据暂存器中;控制该多工器选择并传送缓冲在该逻辑数据缓冲器中的该至少一有效数据部分至该输入/输出控制电路,以使该输入/输出控制电路通过该特定通信接口输出并传送该整页数据的该至少一有效数据部分至该快闪存储器控制器,而不发送该整页数据的该多个其他剩余数据部分。

5、根据实施例,揭露了一种快闪存储器装置。该快闪存储器装置用于一储存装置中并通过一特定通信接口耦接到该储存装置的一快闪存储器控制器,该快闪存储器装置包括一输入/输出控制电路、一命令暂存器、一地址暂存器、一存储器单元阵列、一实体数据暂存器、一逻辑数据暂存器、一多工器以及一控制电路。输入/输出控制电路通过该特定通信接口耦接于该快闪存储器控制器。命令暂存器耦接于该输入/输出控制电路,并用以缓冲该快闪存储器控制器所发送并通过该输入/输出控制电路所传送的一写入命令。地址暂存器耦接于该输入/输出控制电路,并用于缓冲该快闪存储器控制器通过该输入/输出控制电路所传送的一地址资讯。存储器单元阵列至少具有一实体页面单元。实体数据暂存器耦接到该存储器单元阵列。逻辑数据暂存器耦接到该实体数据暂存器。多工器耦接于该实体数据暂存器、该逻辑数据暂存器以及该输入/输出控制电路。控制电路,耦接到该存储器单元阵列、该实体数据暂存器、该逻辑数据暂存器和多工器,并用以:因应于该写入命令,控制该多工器从该输入/输出控制电路选择并传送至少一有效数据部分至该逻辑数据暂存器;产生并插入至少一虚拟数据部分,将该至少一有效数据部分与该至少一虚拟数据部分结合以形成一整页数据,并将该整页数据传送并缓冲到该实体数据暂存器中;以及根据所缓冲的该地址资讯,控制该实体数据暂存器将该实体数据暂存器中的该整页数据传输到该存储器单元阵列的该实体页面单元中,以将该整页数据写入至该实体页面单元中。

技术特征:

1.一种快闪存储器控制器,用于一储存装置并通过一特定通信接口耦接于该储存装置的一快闪存储器装置,以及该快闪存储器控制器包括:

2.如权利要求1所述的快闪存储器控制器,其特征在于,该处理器控制该输入/输出电路传送另一设定特征信号至该快闪存储器装置,该另一设定特征信号携带该设定特征命令、一不同的特征地址以及一不同的参数资讯,该不同的特征地址和该不同的参数资讯用于指示出是否要启用或要禁用该快闪存储器装置自动产生或自动丢弃该虚拟数据部分的一操作。

3.如权利要求1所述的快闪存储器控制器,其特征在于,该处理器控制该输入/输出电路传送另一设定特征信号至该快闪存储器装置,该另一设定特征信号携带该设定特征命令、一不同的特征地址以一及不同的参数资讯;该不同的特征地址对应于该虚拟数据部分的一设置;该不同的参数资讯包括一第一参数数据、一第二参数数据和一第三参数数据;如果该第一参数数据指示出一第一逻辑位元,则该虚拟数据部分会基于一页面地址所决定;如果该第一参数数据指示出一第二逻辑位元,则该虚拟数据部分会基于一设定值所决定;以及,如果该第一参数数据指示出该第二逻辑位元,则该第二参数数据和该第三参数数据会被用来指示出该设定值的一内容。

4.如权利要求1所述的快闪存储器控制器,其特征在于,该处理器控制该输入/输出电路传送一获取特征信号至该快闪存储器装置,令该快闪存储器装置将该设定特征信号之前所携带的该相应的参数资讯回传给该快闪存储器控制器,其中该获取特征信号携带该设定特征命令及该特征地址。

5.如权利要求1所述的快闪存储器控制器,其特征在于,对于执行一读取操作,该处理器会控制该输入/输出电路依顺序地向该快闪存储器装置发送一读取命令、一逻辑行地址、一逻辑列地址和一读取执行命令,令该快闪存储器装置从该实体页面单元读取该整页数据、根据该设定特征信号丢弃该整页数据的该虚拟数据部分并传输该整页数据的该有效数据部分而不发送该整页数据的该虚拟数据部分传送至该快闪存储器控制器,其中该有效数据部分包括一使用者数据部分和一奇偶校验数据部分。

6.如权利要求1所述的快闪存储器控制器,其特征在于,对于执行一写入操作,该处理器会控制该输入/输出电路依顺序地传输一写入命令、一逻辑行地址、一逻辑列地址、一整页数据的一有效数据部分、以及一写入执行命令至该快闪存储器装置,令该快闪存储器装置根据该设定特征信号产生该虚拟数据部分并接着将该有效数据部分和所产生的该虚拟数据部分写入至该快闪存储器的该实体页面单元中。

7.如权利要求1所述的快闪存储器控制器,其特征在于,对于执行一读取操作,该处理器会控制该输入/输出电路另外将一特定命令插入到该读取操作的一读取命令序列中,以及将该读取命令序列传送到该快闪存储器装置,使该快闪存储器装置从该实体页面单元读取该整页数据、根据该设定特征信号丢弃该整页数据的该虚拟数据部分以及在不发送该整页数据的该虚拟数据的情况下传输该整页数据的该有效数据部分到该快闪存储器控制器;以及,该特定命令位于一读取命令之前的一位置、或位于该读取命令与一逻辑列地址之间的一位置或者是位于一逻辑列地址与一读取执行命令之间的一位置。

8.如权利要求1所述的快闪存储器控制器,其特征在于,对于执行一写入操作,该处理器会控制该输入/输出电路另外将一特定命令插入到该写入操作的一写入命令序列中,并将该写入命令序列发送到该快闪存储器装置,使该快闪存储器装置根据该设定特征信号产生该虚拟数据部分、接着将该有效数据部分和所产生的该虚拟数据部分写入至该快闪存储器装置的该实体页面单元中;以及,该特定命令是在一写入命令之前的一位置、或在该写入命令和一逻辑列地址之间的一位置、或在一逻辑列地址和该有效数据部分的一开头之间的一位置或者是在该有效数据部分的一结尾和一写入执行命令之间的一位置。

9.一种快闪存储器控制器的方法,该快闪存储器控制器使用于一储存装置中并通过一特定通信接口耦接到该储存装置的一快闪存储器装置,该方法包括:

10.一种快闪存储器装置,该快闪存储器装置用于一储存装置并通过一特定通信接口连接到该储存装置的一快闪存储器控制器,该快闪存储器装置包括:

11.如权利要求10所述的快闪存储器装置,其特征在于,该多个其他剩余数据部分为多个虚拟数据部分,该控制电路包括:

12.如权利要求11所述的快闪存储器装置,其特征在于,该设定缓冲器用于储存该快闪存储器控制器所发送的一设定特征信号的一特征地址和一相应的参数资讯,该特征地址对应于该虚拟数据部分,该相应的参数资讯记录了该虚拟数据部分的该数据长度和该行地址。

13.如权利要求10所述的快闪存储器储器,其特征在于,该多个其他剩余数据部分为多个虚拟数据部分,该实体数据暂存器中的该整页数据包括多个有效数据部分,每个有效数据部分后面跟着一虚拟数据部分,以及该控制电路包括:

14.一种快闪存储器装置,该快闪存储器装置用于一储存装置中并通过一特定通信接口耦接到该储存装置的一快闪存储器控制器,该快闪存储器装置包括:

15.如权利要求14所述的快闪存储器装置,其特征在于,该控制电路包括:

16.如权利要求15所述的快闪存储器装置,其特征在于,该设定缓冲器用以储存该快闪存储器控制器所传送的一设定特征信号的一特征地址及一相应的参数资讯,该特征地址对应于该随机化电路的操作,而该相应的参数资讯记录了是否启用或关闭该随机化电路之操作的资讯以及该设定值的资讯。

17.如权利要求14所述的快闪存储器装置,其特征在于,该控制电路包括:

技术总结

本发明涉及一种快闪存储器装置、快闪存储器控制器及快闪存储器控制器的方法。该方法包括:传送设定特征信号至快闪存储器装置,设定特征信号携带设定特征命令、特征地址及相应的参数资讯;特征地址对应于有效数据部分或有效数据部分之后的虚拟数据部分,有效数据部分和虚拟数据部分均被包含在整页数据中,整页数据要被写入至快闪存储器装置的实体页面单元中或要被从实体页面单元中所读取出;相应的参数资讯记录有效数据部分的行地址和数据长度、虚拟数据部分的行地址和数据长度、虚拟数据部分的行地址和有效数据部分的行地址或者虚拟数据部分的数据长度和有效数据部分的数据长度。

技术研发人员:吕祖汉,颜孝昌

受保护的技术使用者:慧荣科技股份有限公司

技术研发日:

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!