一种基于强化学习的集成电路长线布线方法

本发明属于集成电路和计算机,特别涉及一种集成电路布局布线技术。

背景技术:

1、集成电路(integrated circuit,ic)是一种微型电子器件或部件。采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;其中所有元件在结构上已组成一个整体,使电子元件向着微小型化、低功耗、智能化和高可靠性方面迈进了一大步。当今半导体工业大多数应用的是基于硅的集成电路。集成电路按集成度高低的不同可分为:小规模集成电路(small scale integratedcircuits)、中规模集成电路(medium scale integrated circuits)、大规模集成电路(large scale integrated circuits)和vlsic超大规模集成电路(very large scaleintegrated circuits)等。

2、在集成电路设计中,布线的目的是在规定的布线区域内实现集成电路内部各个标准单元之间的物理连接。它是集成电路后端设计中的重要环节。随着科技的进步和工艺特征尺寸的缩放,集成电路变得越来越复杂,集成度越来越高,在单位面积中的晶体管的数量不断增加,从而集成电路设计中的布线问题变得越来越复杂。

3、在集成电路设计中布线是一个非常重要和挑战的环节,布线的优劣直接关系到芯片的面积和性能。布线算法是一个极为复杂的问题。在现代集成电路中,线延迟非常明显,28nm时约占比30-40%;进入14nm,尤其在后端设计中,长线经常成为最大延迟,比例提升到40-50%左右。因此,在集成电路设计中长线的布线是一个非常棘手的问题,尤其是当长线比较多的时候,不仅会导致时序难以收敛,而且会导致非常高的功耗。

技术实现思路

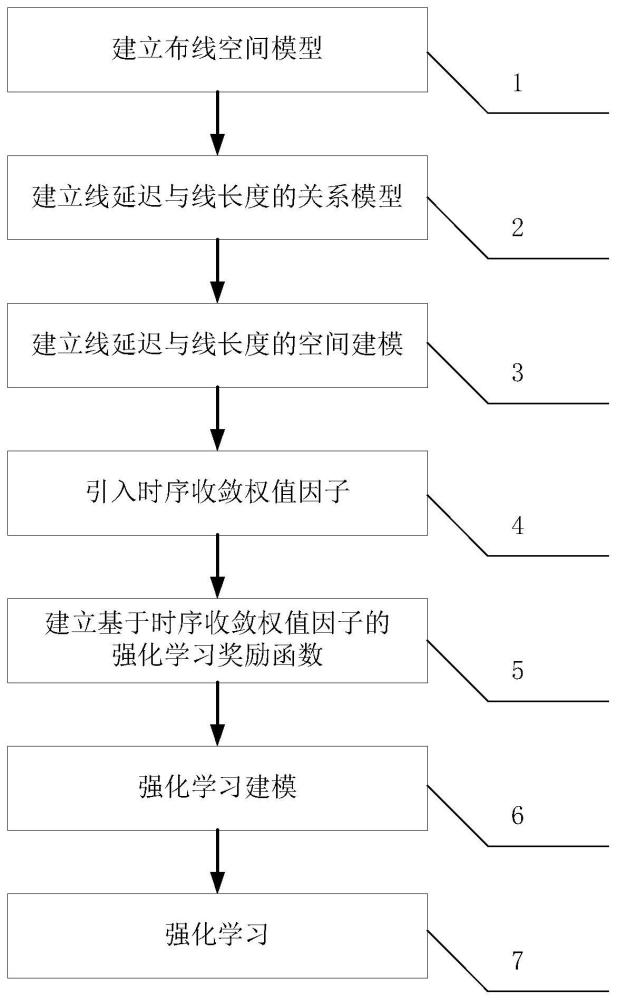

1、为解决上述技术问题,本发明提出一种基于强化学习的集成电路长线布线方法,基于强化学习,实现对长线布线的时序快速收敛。

2、本发明采用的技术方案为:一种基于强化学习的集成电路长线布线方法,包括:

3、s1、将集成电路布线空间模型建模为高斯分布;

4、s2、建立集成电路中线延迟与布线长度的关系模型,表达式为:τnet=k*lα,

5、其中为线延迟τnet,l为线长度,α为线长度的幂值,k为比例因子;

6、s3、根据步骤s1的高斯模型、步骤s2的关系模型,建模集成电路的线延迟与线长度的高斯分布空间:

7、s4、构建时序收敛权值因子:ω=t-τcell;其中t为相应路径的时钟周期,τcell为逻辑单元有关的延迟;

8、s5、建立基于时序收敛权值因子的强化学习奖励函数:τi为第i条长线的线延迟,n为长线布线的数量;

9、s6、建立集成电路长线布线强化学习模型,通过ω限定有效的可选的布线分布空间,通过ω选择可能的环境状态和可能的动作;基于时序收敛权值因子的强化学习奖励函数用来确定对应的奖励;

10、s7、根据步骤s6所建立的集成电路长线布线强化学习模型,对当前集成电路长线布线进行强化学习,得到最优的长线布线结果。

11、本发明的有益效果:本发明针对集成电路电路长线布线提出了几种模型,引入了时序收敛权值因子,并结合强化学习设计了基于时序收敛权值因子的强化学习奖励函数,以实现对长线布线的快速收敛。

技术特征:

1.一种基于强化学习的集成电路长线布线方法,其特征在于,包括:

2.根据权利要求1所述的一种基于强化学习的集成电路长线布线方法,其特征在于,步骤s2所述的关系模型的表达式为:

3.根据权利要求2所述的一种基于强化学习的集成电路长线布线方法,其特征在于,强化学习奖励函数表达式为:

技术总结

本发明公开一种基于强化学习的集成电路长线布线方法,应用于集成电路布局布线领域,针对现有技术中存在的当长线比较多的时候,不仅会导致时序难以收敛,而且会导致非常高的功耗的问题;本发明基于强化学习,针对集成电路电路长线布线提出了几种模型,引入了时序收敛权值因子,并结合强化学习设计了基于时序收敛权值因子的强化学习奖励函数,以实现对长线布线的快速收敛。

技术研发人员:李磊,周婉婷

受保护的技术使用者:电子科技大学长三角研究院(湖州)

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!