一种测试芯片总线输入信号判决电平容限的方法及装置与流程

本发明涉及信号测试,特别是一种测试芯片总线输入信号判决电平容限的方法及装置。

背景技术:

1、在芯片设计和制造过程中,需要对芯片进行各种测试,以确保芯片的性能符合规格要求。其中,总线输入信号判决电平容限是一个重要的测试参数,该测试参数反映了芯片对总线输入信号的判决能力,对芯片的性能评估具有重要意义。总线输入信号判决电平容限是指在总线通信中,接收器能够正确判断输入信号是逻辑高电平还是逻辑低电平的电压容限范围。通常情况下,逻辑高电平被定义为接近于总线电平的电压值,而逻辑低电平则被定义为接近于地或负极性电源的电压值。判决电平容限是一种容许一定范围内的电压波动,而仍能正确判断信号逻辑状态的设计要求。这样可以使得在总线通信中,即使存在一定的电压噪声或信号衰减,接收器仍能准确地解读输入信号。

2、目前,常用的总线输入信号判决电平容限测试方法是使用示波器或万用表测量逻辑高电平和逻辑低电平的电压值,根据总线通信协议的要求,判断输入信号是否在规定的判决电平容限范围内。然而,这种方法需要手动调节示波器的触发电平和采样率,不仅效率低下,而且容易出现误差,并且需要专门的测试设备和测试流程,成本较高且测试时间较长,不利于芯片的快速开发和生产。

技术实现思路

1、鉴于此,本发明提供一种测试芯片总线输入信号判决电平容限的方法及装置,采用了电平转换芯片对输入信号进行转换,避免了频繁手动调节示波器触发电平等,提升了芯片测试的效率和准确性;同时,方法和装置简单易行,适用于各种类型的芯片测试。

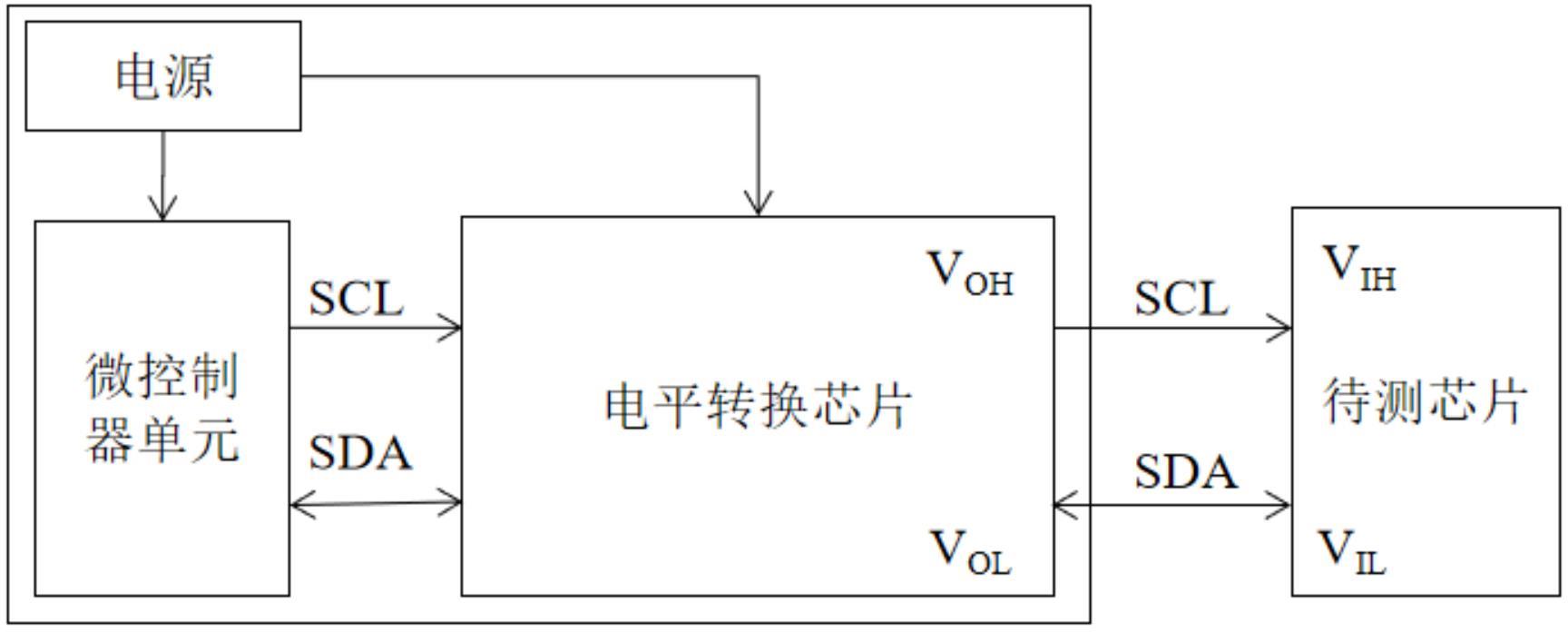

2、本发明公开了一种测试芯片总线输入信号判决电平容限的装置,其包括微控制器单元、电平转换芯片和待测芯片;微控制器单元通过电平转换芯片与待测芯片连接;

3、微控制器单元用于提供总线时钟,通过改变脉冲宽度调制占空比,调控电平转换芯片的输入端总线信号的高电平和低电平;同时,接收并分析待测芯片输出的反馈信号;

4、电平转换芯片用于将微控制器单元的输出总线信号转换为高电平和低电平,并实现高电平在高电平容限范围内线性调整,低电平在低电平容限范围内线性调整;

5、待测芯片用于接收电平转换芯片输出的总线信号,并将该总线信号的高电平和低电平分别与芯片自身设定的高电平判决门限和低电平判决门限进行对比,将对比得到的判断信号输出到微控制器单元,以得到待测芯片的判决电平容限;其中,判断信号为高电平或低电平。

6、进一步地,所述微控制器单元用于通过脉冲宽度调制直流电路控制脉冲的占空比,实现在一个周期内平均输出不同电平;通过在一段时间内改变脉冲的宽度调制直流信号的电平,并通过运算放大器将输入信号进行放大,使得信号达到所需的幅度后,输出至电平转换芯片;其中,脉冲宽度调制直流电路由电阻和运算放大器串联构成;电阻和微控制器单元的输出端连接,运算放大器的输出端与电平转换芯片的输入端连接。

7、进一步地,所述微控制器单元用于对待测芯片输出的反馈信号进行分析和处理,得到待测芯片的判决电平容限。

8、进一步地,微控制器单元还具体用于:

9、确保其与待测芯片之间的物理接口连接正确,确保其能够读取待测芯片的输出信号,即使用其的输入和输出引脚或者模拟输入功能,采集待测芯片的输出信号;对采集到的信号进行数字化处理;根据待测芯片输出的信号特性,编写微控制器单元的控制程序分析信号;并将检测到的总线信号的电平数据存储在内部存储器中,以供进一步分析或监控;该控制程序在一个循环中运行,以持续监测待测芯片输出的总线的高低电平信号。

10、进一步地,所述微控制器单元用于在调整电平转换芯片的供电电压后,根据是否能够读取待测芯片中寄存器的返回值,判断待测芯片的串行接口电平门限。

11、进一步地,若微控制器单元的输出端接入一个低通滤波器,低通滤波器的带宽远小于脉冲宽度调制频率;脉冲宽度调制经过低通滤波后的直流电压相当于脉冲宽度调制的高电平和低电平的差与脉冲宽度调制占空比的乘积。

12、进一步地,所述电平转换芯片的工作电压输出端与电平转换芯片之间增加一个单位增益同相放大器,即电压缓冲器,则电压缓冲器的输出电压等于同相输入端的输入电压,并且电压缓冲器的输出电流可为电平转换芯片提供正常工作所需的电流;只需要修改脉冲宽度调制占空比,就可以改变电压缓冲器的输出电压和电平转换芯片的供电电压,从而改变电平转换芯片输出的高电平电压。

13、本发明还公开了一种测试芯片总线输入信号判决电平容限的方法,其包括:

14、通过微控制器单元控制电平转换芯片实现高电平和低电平转换;

15、将经过高电平和低电平转换后的一系列总线信号发送给待测芯片;

16、测量待测芯片的信号电平,并将测量结果反馈给微控制器单元;

17、待测芯片根据接收到的总线信号,得到待测芯片的判决电平容限;

18、判断总线信号判决电平容限是否符合所要求的信号判决电平容限。

19、进一步地,所述待测芯片根据接收到的总线信号,得到待测芯片的判决电平容限,包括:

20、待测芯片接收电平转换芯片转换后的总线信号,并将该总线信号的高电平和低电平分别与芯片自身设定的高电平判决门限和低电平判决门限进行对比,将对比得到的判断信号输出到微控制器单元,以得到待测芯片的判决电平容限;其中,判断信号为高电平或低电平。

21、进一步地,若总线信号判决电平容限符合要求,则测试通过;若不符合要求,则测试失败。

22、由于采用了上述技术方案,本发明具有如下的优点:采用了电平转换芯片对输入信号的高电平和低电平进行线性调整,低成本实现scl(serial clock,串行时钟线)/sda(serial data,串行数据线)信号高电平和低电平线性输出,能有效的验证待测芯片scl/sda总线输入信号实际的判决电平门限,从而识别待测芯片判决电平门限与理论值的差异,得出待测芯片电平识别的容忍度;本发明的方法和装置简单、成本低,可扩展到其他总线芯片输入信号判决电平测试,例如串行外设接口和精简引脚总线。

技术特征:

1.一种测试芯片总线输入信号判决电平容限的装置,其特征在于,包括微控制器单元、电平转换芯片和待测芯片;微控制器单元通过电平转换芯片与待测芯片连接;

2.根据权利要求1所述的测试芯片总线输入信号判决电平容限的装置,其特征在于,所述微控制器单元用于通过脉冲宽度调制直流电路控制脉冲的占空比,实现在一个周期内平均输出不同电平;通过在一段时间内改变脉冲的宽度调制直流信号的电平,并通过运算放大器将输入信号进行放大,使得信号达到所需的幅度后,输出至电平转换芯片;其中,脉冲宽度调制直流电路由电阻和运算放大器串联构成;电阻和微控制器单元的输出端连接,运算放大器的输出端与电平转换芯片的输入端连接。

3.根据权利要求2所述的测试芯片总线输入信号判决电平容限的装置,其特征在于,所述微控制器单元用于对待测芯片输出的反馈信号进行分析和处理,得到待测芯片的判决电平容限。

4.根据权利要求1所述的测试芯片总线输入信号判决电平容限的装置,其特征在于,微控制器单元还具体用于:

5.根据权利要求1所述的测试芯片总线输入信号判决电平容限的装置,其特征在于,所述微控制器单元用于在调整电平转换芯片的供电电压后,根据是否能够读取待测芯片中寄存器的返回值,判断待测芯片的串行接口电平门限。

6.根据权利要求1所述的测试芯片总线输入信号判决电平容限的装置,其特征在于,若微控制器单元的输出端接入一个低通滤波器,低通滤波器的带宽远小于脉冲宽度调制频率;脉冲宽度调制经过低通滤波后的直流电压相当于脉冲宽度调制的高电平和低电平的差与脉冲宽度调制占空比的乘积。

7.根据权利要求6所述的测试芯片总线输入信号判决电平容限的装置,其特征在于,所述电平转换芯片的工作电压输出端与电平转换芯片之间增加一个单位增益同相放大器,即电压缓冲器,则电压缓冲器的输出电压等于同相输入端的输入电压,并且电压缓冲器的输出电流可为电平转换芯片提供正常工作所需的电流;只需要修改脉冲宽度调制占空比,就可以改变电压缓冲器的输出电压和电平转换芯片的供电电压,从而改变电平转换芯片输出的高电平电压。

8.一种测试芯片总线输入信号判决电平容限的方法,其特征在于,包括:

9.根据权利要求8所述的方法,其特征在于,所述待测芯片根据接收到的总线信号,得到待测芯片的判决电平容限,包括:

10.根据权利要求8所述的方法,其特征在于,若总线信号判决电平容限符合要求,则测试通过;若不符合要求,则测试失败。

技术总结

本发明公开了一种测试芯片总线输入信号判决电平容限的方法及装置,该装置的微控制器单元用于提供总线时钟,通过改变脉冲宽度调制占空比,调控电平转换芯片的输入端总线信号的高低电平;同时,接收并分析待测芯片输出的反馈信号;电平转换芯片用于实现微控制器单元输出的总线信号转换为高低电平,并实现高电平在高电平容限范围内线性调整,低电平在低电平容限范围内线性调整;待测芯片用于接收电平转换芯片输出的总线信号,并将该总线信号的高低电平与芯片自身设定的高低电平判决门限进行对比,将对比得到的判断信号输出到微控制器单元,以得到待测芯片的判决电平容限。本发明简单、成本低,可扩展到其他总线芯片输入信号判决电平测试。

技术研发人员:彭云武,王金辉,秦思林,刘雅婷

受保护的技术使用者:成都电科星拓科技有限公司

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!