用于执行用于复数的融合乘-加指令的系统和方法与流程

本文中描述的实施例总体上涉及指令集架构。更具体地,所描述的实施例总体上涉及用于执行用于复数的融合乘-加指令的系统和方法。

背景技术:

1、在计算中、尤其在高性能计算中,执行复数乘法和累加的指令是常见的。处理器的指令集架构常包括用于执行复数算术的指令。由于此类指令是常见的,因此对性能和功耗的改进(包括降低的寄存器堆压力、降低的存储器压力和减少数量的所需指令)可使总体性能受益。

技术实现思路

技术特征:

1.一种处理器,包括:

2.如权利要求1所述的处理器,其中,所述对应的实数结果值包括所述第一实数乘积与所述第二实数乘积之间的差和对应的紧缩累加实数值的和,并且所述对应的虚数结果值包括对应的紧缩累加虚数值、所述第一虚数乘积和所述第二虚数乘积的和。

3.如权利要求1所述的处理器,其中,所述对应的实数结果值包括所述对应的紧缩累加实数值、所述第一实数乘积和所述第二实数乘积的和,并且所述对应的虚数结果值包括所述第一虚数乘积与所述第二虚数乘积之间的差和所述紧缩累加虚数值的和。

4.如权利要求1所述的处理器,其中,所述第一多个紧缩源复数、所述第二多个紧缩源复数和所述多个紧缩累加复数中的每一个都是单精度浮点值。

5.如权利要求1所述的处理器,其中,所述第一多个紧缩源复数和所述第二多个紧缩源复数中的复数包括32位的数,并且所述紧缩累加复数大于32位。

6.如权利要求1所述的处理器,其中,所述专用逻辑包括一个或多个专用核,其中,所述一个或多个专用核和所述一个或多个核在单个管芯上。

7.如权利要求1所述的处理器,进一步包括:

8.如权利要求7所述的处理器,进一步包括:

9.一种装置,包括:

10.一种处理器核,包括:

11.如权利要求10所述的处理器核,其特征在于,所述向量单元是16宽向量处理单元(vpu),所述vpu执行整型、单精度浮点以及双精度浮点指令中的一个或多个。

12.如权利要求11所述的处理器核,其特征在于,所述vpu通过混合单元支持对寄存器输入的混合、通过数值转换单元支持数值转换,并通过复制单元支持对存储器输入的复制。

13.一种方法,包括:

技术总结

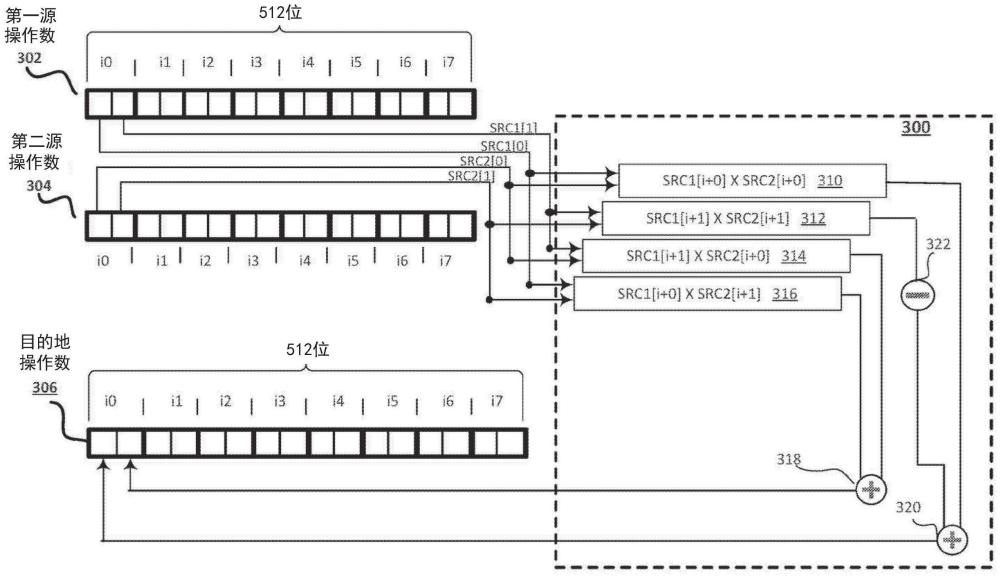

本申请公开了用于执行用于复数的融合乘‑加指令的系统和方法。在一个实施例中,一种方法包括:取出指令,该指令的格式包括操作码、第一源操作数标识符、第二源操作数标识符和目的地操作数标识符,其中,标识符中的每个标识符用于标识存储包括至少一个复数的紧缩数据的位置;对指令解码;检取与第一和第二源操作数标识符相关联的数据;以及执行经解码的指令,以:对于所标识的第一和第二源操作数的每个紧缩数据元素位置,交叉相乘实部和虚部以生成四个乘积:实部的乘积、虚部的乘积以及两个混合乘积;通过根据指令对这四个乘积求和来生成复数结果;以及将结果存储到所标识的目的地操作数的对应位置。

技术研发人员:R·S·杜波茨夫,R·凡伦天,J·考博尔,M·吉尔卡尔,E·乌尔德-阿迈德-瓦尔

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!