耦合可调的量子比特及其驱动方法、装置与系统与流程

本发明涉及量子计算,特别涉及一种耦合可调的量子比特及其驱动方法、装置与系统。

背景技术:

1、单磁通量子脉冲器件具有速度快、功耗低、与半导体加工工艺兼容等优点。单磁通量子脉冲频率高,可以直接对量子比特驱动,不需要与微波源进行混频。

2、目前,基于单磁通量子脉冲的两比特门方案主要基于固定耦合芯片,无法把两比特门的之间的耦合关闭,无法对相位进行初始化,增加比特之间的串扰。通过调节一个量子比特的能级难以实现对两比特门耦合强度的调节。

技术实现思路

1、为了解决现有技术中,单磁通量子脉冲驱动的两比比特门耦合强度无法调节,导致其中一个量子比特进行初始化时,极易受到与其耦合的量子比特的干扰,导致态泄漏,进而难以使比特初始化;以及两比特门能级系统难以调节至非等间距能级的问题,本发明采用如下技术方案。

2、第一方面,提供一种耦合可调的量子比特,量子比特由单磁通量子脉冲驱动,包括:第一量子比特,第二量子比特,耦合器,第一电容,第二电容,第三电容,磁通偏置线;第一量子比特串联第一电容后与耦合器连接,耦合器串联第二电容后与第二量子比特连接,第三电容的一端与第一量子比特连接,第三电容的另一端与第二量子比特连接,磁通偏置线设置于耦合器外。

3、进一步地,耦合器为超导谐振腔,超导谐振腔制作于半导体衬底表面;沿垂直于半导体衬底表面方向,超导谐振腔平面图形的边缘构成矩形,包括:中央线,第一接地平面,第二接地平面;第一接地平面与第二接地平面之间设置有间隙;中央线沿矩形的长边方向,居中设置于间隙,将间隙分割为第一共面波导间隙,以及第二共面波导间隙,其中,第一共面波导间隙位于中央线与第一接地平面之间,第二共面波导间隙位于中央线与第二接地平面之间;在中央线上,沿中央线长边方向对称设置有第一耦合间隙、第二耦合间隙,第一耦合间隙与第二耦合间隙之间的中央线部分的长度为波导长度。

4、进一步地,波导长度为:l = ( 2 / n ) · λm,其中,l为波导长度,n为自然数,λm为微波波长。

5、进一步地,中央线任一侧的共面波导间隙中设置有超导量子干涉仪。

6、进一步地,超导量子干涉仪为约瑟夫森结器件。

7、进一步地,超导谐振腔的材质为铝。

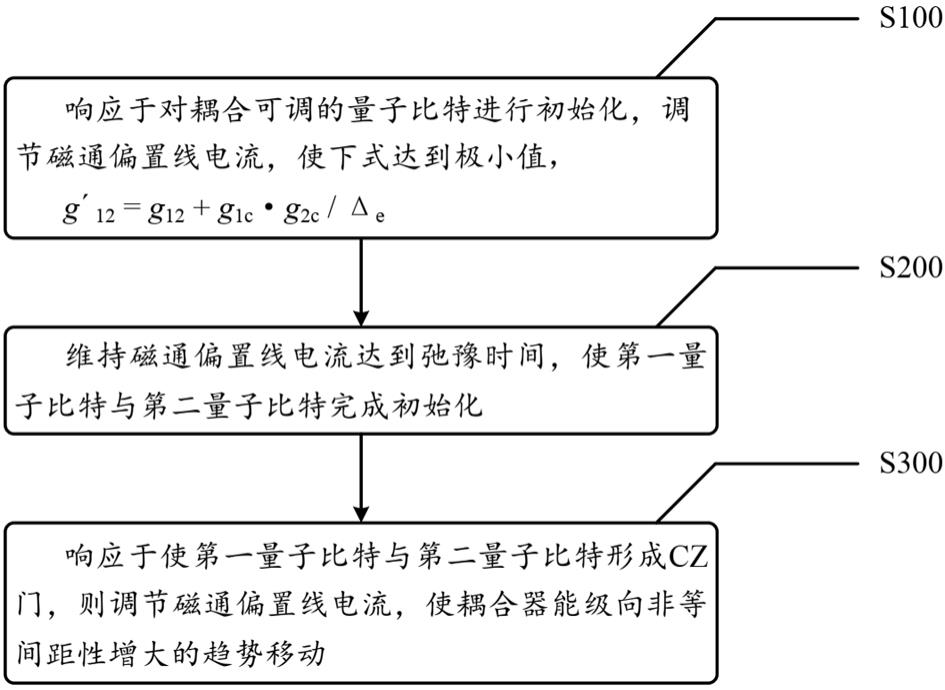

8、进一步地,磁通偏置线平行或垂直于中央线设置;当磁通偏置线平行于中央线设置时,磁通偏置线相对于超导量子干涉仪设置于中央线的另一侧。

9、进一步地,量子比特还包括第一转换器,第四电容;第一量子比特与第四电容的一端电性连接,第四电容的另一端与第一转换器电性连接。

10、进一步地,第一转换器具有:第一电流输入端,第一微波输入端,第一脉冲输出端;第一转换器根据第一电流输入端所接收的第一电流信号,以及第一微波输入端所接收的第一微波信号,由第一脉冲输出端输出具有第一脉冲间隔的第一脉冲信号,以驱动第一量子比特。

11、进一步地,量子比特还包括第二转换器,第五电容;第二量子比特与第五电容的一端电性连接,第五电容的另一端与第二转换器电性连接。

12、进一步地,第二转换器具有:第二电流输入端,第二微波输入端,第二脉冲输出端;所述第二转换器根据所述第二电流输入端所接收的第二电流信号,以及所述第二微波输入端所接收的第二微波信号,由所述第二脉冲输出端输出具有第二脉冲间隔的第二脉冲信号,以驱动所述第二量子比特。

13、第二方面,提供一种耦合可调的量子比特驱动方法,包括:响应于对耦合可调的量子比特进行初始化,调节磁通偏置线电流,使下式达到极小值,g´12 = g12 + g1c·g2c /δe,其中,g´12表示第一量子比特与第二量子比特间的有效耦合强度,g12表示第一量子比特与第二量子比特间的耦合强度,g1c表示第一量子比特与耦合器间的耦合强度,g2c表示第二量子比特与耦合器间的耦合强度,δe = 1 / δ1c + 1 / δ2c,其中,δ1c = ω1 – ωc,δ2c =ω2 – ωc,ω1表示第一量子比特的频率,ω2表示第二量子比特的频率,ωc表示耦合器频率;维持磁通偏置线电流达到弛豫时间,使第一量子比特与第二量子比特完成初始化;响应于使第一量子比特与第二量子比特形成cz门,则调节磁通偏置线电流,使耦合器能级向非等间距性增大的趋势移动。

14、第三方面,提供一种耦合可调的量子比特驱动装置,包括:去耦合模块,用于响应于对耦合可调的量子比特进行初始化,调节磁通偏置线电流,使下式达到极小值,g´12 =g12 + g1c·g2c / δe,其中,g´12表示第一量子比特与第二量子比特间的有效耦合强度,g12表示第一量子比特与第二量子比特间的耦合强度,g1c表示第一量子比特与耦合器间的耦合强度,g2c表示第二量子比特与耦合器间的耦合强度,δe = 1 / δ1c + 1 / δ2c,其中,δ1c= ω1 – ωc,δ2c =ω2 – ωc,ω1表示第一量子比特的频率,ω2表示第二量子比特的频率,ωc表示耦合器频率。

15、初始化模块,用于维持磁通偏置线电流达到弛豫时间,使第一量子比特与第二量子比特完成初始化;强耦合模块,用于响应于使第一量子比特与第二量子比特形成cz门,则调节磁通偏置线电流,使耦合器能级向非等间距性增大的趋势移动。

16、第四方面,提供一种耦合可调的量子比特芯片,包括第一方面记载的耦合可调的量子比特,用于进行量子计算。

17、第五方面,提供一种耦合可调的量子比特驱动系统,包括存储器、处理器及存储在存储器上并可在处理器上运行的耦合可调的量子比特驱动程序,处理器执行耦合可调的量子比特驱动程序时,实现第二方面记载的耦合可调的量子比特驱动方法。

18、第六方面,提供一种计算机可读存储介质,其上存储有耦合可调的量子比特驱动程序,所述耦合可调的量子比特驱动程序被处理器执行时,实现第二方面记载的耦合可调的量子比特驱动方法。

19、本发明实施例提供的技术方案带来的有益效果是:

20、1. 通过调节流过磁通偏置线的电流大小,实现对耦合器频率的调节;

21、2. 通过调节耦合器频率,控制量子比特间的耦合强度;

22、3. 将比特调整至弱耦合状态,进行初始化;

23、4. 将比特调整至强耦合状态,增加能级间的非等间距性,降低比特间的串扰。

技术特征:

1.一种耦合可调的量子比特,其特征在于,所述量子比特由单磁通量子脉冲驱动,包括:第一量子比特,第二量子比特,耦合器,第一电容,第二电容,第三电容,磁通偏置线;

2.根据权利要求1所述耦合可调的量子比特,其特征在于,所述耦合器为超导谐振腔,所述超导谐振腔制作于半导体衬底表面;

3. 根据权利要求2所述耦合可调的量子比特,其特征在于,所述波导长度为:

4.根据权利要求2所述耦合可调的量子比特,其特征在于,所述中央线任一侧的共面波导间隙中设置有超导量子干涉仪。

5.根据权利要求4所述耦合可调的量子比特,其特征在于,所述超导量子干涉仪为约瑟夫森结器件。

6.根据权利要求2所述的耦合可调的量子比特,其特征在于,所述超导谐振腔的材质为铝。

7.根据权利要求4所述耦合可调的量子比特,其特征在于,所述磁通偏置线平行或垂直于所述中央线设置;

8.根据权利要求1所述耦合可调的量子比特,其特征在于,所述量子比特还包括第一转换器,第四电容;

9.根据权利要求8所述耦合可调的量子比特,其特征在于,所述第一转换器具有:第一电流输入端,第一微波输入端,第一脉冲输出端;

10.根据权利要求1所述耦合可调的量子比特,其特征在于,所述量子比特还包括第二转换器,第五电容;

11.根据权利要求10所述耦合可调的量子比特,其特征在于,所述第二转换器具有:第二电流输入端,第二微波输入端,第二脉冲输出端;

12.一种耦合可调的量子比特驱动方法,其特征在于,包括:

13.一种耦合可调的量子比特驱动装置,其特征在于,包括:

14.一种耦合可调的量子比特芯片,其特征在于,包括权利要求1-11任一项所述的耦合可调的量子比特,用于进行量子计算。

15.一种耦合可调的量子比特驱动系统,其特征在于,包括存储器、处理器及存储在存储器上并可在处理器上运行的耦合可调的量子比特驱动程序,所述处理器执行所述耦合可调的量子比特驱动程序时,实现权利要求12所述耦合可调的量子比特驱动方法。

16.一种计算机可读存储介质,其特征在于,其上存储有耦合可调的量子比特驱动程序,所述耦合可调的量子比特驱动程序被处理器执行时,实现权利要求12所述的耦合可调的量子比特驱动方法。

技术总结

本发明公开一种耦合可调的量子比特及其驱动方法、装置与系统,涉及量子计算技术领域。耦合可调的量子比特,由单磁通量子脉冲驱动,包括:第一量子比特,第二量子比特,耦合器,第一电容,第二电容,第三电容,磁通偏置线;第一量子比特串联第一电容后与耦合器连接,耦合器串联第二电容后与第二量子比特连接,第三电容的一端与第一量子比特连接,第三电容的另一端与第二量子比特连接,磁通偏置线设置于耦合器外。通过调节流过磁通偏置线的电流大小,实现对耦合器频率的调节;通过调节耦合器频率,控制量子比特间的耦合强度;将比特调整至弱耦合状态,进行初始化;将比特调整至强耦合状态,增加能级间的非等间距性,降低比特间的串扰。

技术研发人员:王辉,李勇,于晓艳,刘强

受保护的技术使用者:苏州元脑智能科技有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!