多通道速率均衡的高速链路及其数据传输方法与流程

本发明涉及高速链路,具体涉及一种多通道速率均衡的高速链路及其数据传输方法。

背景技术:

1、高速串行链路收发器包含若干功能独立的发射端tx和接收端rx,发射端tx和接收端rx均是由物理媒介适配层(physical media attachment, pma)和物理编码子层(physical codingsublayer, pcs)两个子层组成。pma子层内部集成了高速串并转换电路,预加重电路、接收均衡电路、时钟发生电路和时钟恢复电路。pcs子层内部集成了编/解码电路、弹性缓冲电路、通道绑定电路和时钟修正电路。

2、目前高速io通信协议的物理层普遍采用多通道串行链路,pcs可以绑定多个pma。以pcie为例,一般的设备运行在x1、x2、x4、x8、x16等模式,高性能gpu一般运行在x16模式。多通道串行链路要求每个通道的运行速率必须一致,例如pcie3.0 x16要求16个通道运行速率在8gt/s,pcie4.0 x16要求所有16个通道运行速率在16gt/s。多通道串行链路的通道数固定,无法灵活变化。例如pcie不能支持x15。

3、并且随着多通道串行链路的通道速率的进一步提升,由于生产工艺的限制,对于x16甚至更多通道数的专用通信链路来说,在实际的芯片筛选中,保证连续16个串行链路都可以运行在如此高的速率,会产生很多不良芯片,造成资源的浪费,也间接提高芯片的使用成本。

技术实现思路

1、本发明的目的在于提供一种多通道速率均衡的高速链路及其数据传输方法,在多通道链路存在某些不良通道的情况下,支持动态速率配置修复,保证多通道链路的传输速率满足要求,降低芯片使用成本。

2、为了实现上述目的,本发明提供如下技术方案:

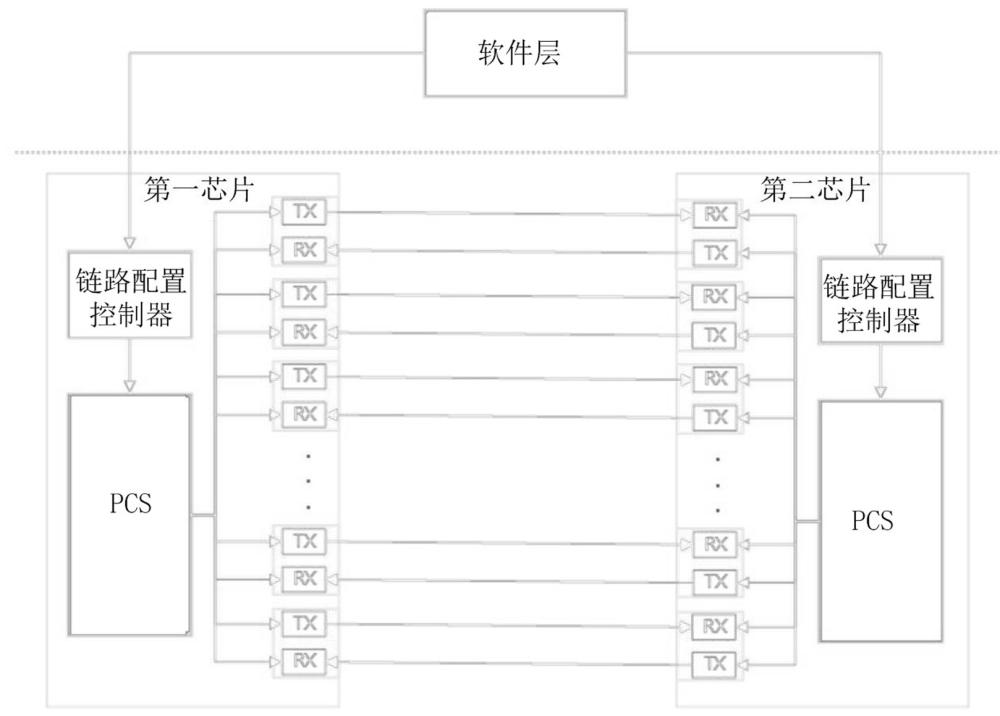

3、一种多通道速率均衡的高速链路,所述高速链路包括第一芯片和第二芯片,所述第一芯片和第二芯片均包括链路配置控制器以及多个发射端和多个接收端,所述第一芯片和第二芯片的发射端、接收端形成多个数据传输链路;每个所述链路支持单独的训练;其中,所述链路配置控制器包括:

4、使能寄存器,用于控制每个所述链路的开关状态;

5、速率寄存器,用于配置每个所述链路的数据传输速率;

6、pcs均衡分包阶段数寄存器,用于标识一个完整数据传输过程中的分包阶段数;

7、均衡阶段分包配置寄存器,用于标识pcs在每个分包阶段是否从对应链路的pma发送/收取数据包;

8、pcs的通道绑定和均衡控制寄存器,用于开启或关闭所述pcs均衡分包阶段数寄存器和均衡阶段分包配置寄存器。

9、较佳地,所述高速链路还包括软件层,用于所述高速链路的软件驱动并配置所述链路配置控制器。

10、一种多通道速率均衡的高速链路的数据传输方法,所述方法包括:

11、配置阶段:

12、所述软件层获取每个所述链路可运行的最高速率并基于所述最高速率配置每个所述链路的速率寄存器;

13、所述软件层启动对每个所述链路的单独训练;

14、所述软件层基于所述速率寄存器中对应的链路速率,获取一个完整数据的分包阶段数以及pcs在每个分包阶段是否从对应链路的pma发送/收取数据包,并为pcs均衡分包阶段数寄存器和均衡阶段分包配置寄存器赋值;

15、所述pcs的通道绑定和均衡控制寄存器开启所述pcs均衡分包阶段数寄存器和均衡阶段分包配置寄存器;

16、传输阶段:

17、一个待传输的完整数据发送时,所述第一芯片的所述pcs将所述完整数据拆分为与所述pcs均衡分包阶段数寄存器和均衡阶段分包配置寄存器相匹配的数据包;

18、由每个所述链路的发送端根据所述速率寄存器、均衡阶段分包配置寄存器、以及均衡阶段分包配置寄存器的配置进行数据发送;

19、所述第二芯片的所述pcs根据所述pcs均衡分包阶段数寄存器和均衡阶段分包配置寄存器的配置,从所述第二芯片的所述pma取出所有数据片并整合成原始的完整数据。

20、较佳地,“所述软件层获取每个所述链路可运行的最高速率并基于所述最高速率配置每个所述链路的速率寄存器”的速率包括:

21、所述速率寄存器预设有速率寄存器值与运行速率的对应关系表,基于每个所述链路的最高速率选取所述对应关系表中可运行的最接近的运行速率,并基于该运行速率为所述速率寄存器赋值。

22、较佳地,“所述软件层获取每个所述链路可运行的最高速率并基于所述最高速率配置每个所述链路的速率寄存器”的速率包括:

23、所述速率寄存器预设有速率寄存器值与运行速率的对应关系表,选取所述对应关系表中可行的运行速率,并基于该运行速率为所述速率寄存器赋值。

24、较佳地,所述pcs均衡分包阶段数寄存器赋予的分包阶段值等于运行速率最快的链路对应的运行速率除以所有链路运行速率的最大公约数。

25、较佳地,所述均衡阶段分包配置寄存器的赋值为:对于运行速率最快的链路,每个分包阶段对应的bit位都设置为1;而运行速率较慢的链路,以运行速率最快链路的时钟为基准,如果当前分包阶段无法完成一个数据包的传输,则该分包阶段bit设置为0,如果当前分包阶段能够完成一个数据包的传输,则该分包阶段bit设置为1。

26、较佳地,所述第一芯片和第二芯片的pcs至少增设一个冗余链路。

27、较佳地,在“所述软件层启动对每个所述通道的单独训练”的步骤之前,所述方法还包括:

28、所述软件层根据每个所述链路不良状态并通过所述使能寄存器关闭不良的链路。

29、较佳地,在所述链路可运行的最高速率小于其最大设计运行速率的一半时关闭该不良链路,利用所述冗余链路替换该不良链路。

30、本发明的优点在于:

31、本发明提供的多通道速率均衡的高速链路及其数据传输方法,在多通道链路存在某些不良通道的情况下,支持动态速率配置修复,保证多通道链路的传输速率满足要求,降低芯片使用成本。

技术特征:

1.一种多通道速率均衡的高速链路,其特征在于,所述高速链路包括第一芯片和第二芯片,所述第一芯片和第二芯片均包括链路配置控制器以及多个发射端和多个接收端,所述第一芯片和第二芯片的发射端、接收端形成多个数据传输链路;每个所述链路支持单独的训练;其中,所述链路配置控制器包括:

2.如权利要求1所述的多通道速率均衡的高速链路,其特征在于,所述高速链路还包括软件层,用于所述高速链路的软件驱动并配置所述链路配置控制器。

3.一种如权利要求2所述的多通道速率均衡的高速链路的数据传输方法,其特征在于,所述方法包括:

4.如权利要求3所述的数据传输方法,其特征在于,“所述软件层获取每个所述链路可运行的最高速率并基于所述最高速率配置每个所述链路的速率寄存器”的速率包括:

5.如权利要求3所述的数据传输方法,其特征在于,“所述软件层获取每个所述链路可运行的最高速率并基于所述最高速率配置每个所述链路的速率寄存器”的速率包括:

6.如权利要求4或5所述的数据传输方法,其特征在于,所述pcs均衡分包阶段数寄存器赋予的分包阶段值等于运行速率最快的链路对应的运行速率除以所有链路运行速率的最大公约数。

7.如权利要求6所述的数据传输方法,其特征在于,所述均衡阶段分包配置寄存器的赋值为:对于运行速率最快的链路,每个分包阶段对应的bit位都设置为1;而运行速率较慢的链路,以运行速率最快链路的时钟为基准,如果当前分包阶段无法完成一个数据包的传输,则该分包阶段bit设置为0,如果当前分包阶段能够完成一个数据包的传输,则该分包阶段bit设置为1。

8.如权利要求3所述的数据传输方法,其特征在于,所述第一芯片和第二芯片的pcs至少增设一个冗余链路。

9.如权利要求8所述的数据传输方法,其特征在于,在“所述软件层启动对每个所述链路的单独训练”的步骤之前,所述方法还包括:

10.如权利要求9所述的数据传输方法,其特征在于,在所述链路可运行的最高速率小于其最大设计运行速率的一半时关闭该不良链路,利用所述冗余链路替换该不良链路。

技术总结

本发明公开一种多通道速率均衡的高速链路及其数据传输方法,高速链路包括第一芯片和第二芯片,第一芯片和第二芯片均包括链路配置控制器以及多个发射端和多个接收端,第一芯片和第二芯片的发射端、接收端形成多个数据传输链路;每个链路支持单独的训练;其中,链路配置控制器包括:使能寄存器、速率寄存器、PCS均衡分包阶段数寄存器、均衡阶段分包配置寄存器以及PCS的通道绑定和均衡控制寄存器。该数据传输方法是基于该高速链路实现。本发明在多通道链路存在某些不良链路的情况下,支持动态速率配置修复,保证多通道链路的传输速率满足要求,降低芯片使用成本。

技术研发人员:江涛

受保护的技术使用者:无锡芯素科技有限公司

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!