一种软件辅助调试模块和芯片的制作方法

本发明涉及软件调试,尤其涉及一种软件辅助调试模块和芯片。

背景技术:

1、大型的soc芯片通常比较复杂,其软件调试比较困难。尤其是在多cpu,多os的情况下,芯片结构复杂使得协同调试非常困难。例如,当软件调试卡死,或者当软件调试出现错误时无法获知具体是哪里发生了错误等,其问题追溯比较困难。

技术实现思路

1、本发明提供了一种软件辅助调试模块和芯片,以用于对芯片进行软件调试,并且在软件调试出错时方便问题追溯。

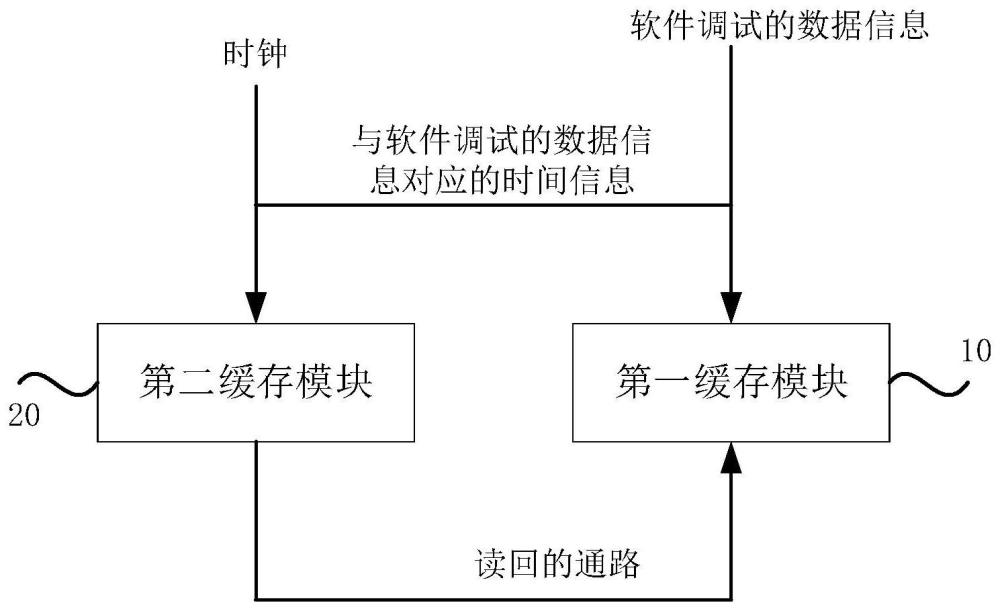

2、根据本发明的一方面,提供了一种软件辅助调试模块,该软件辅助调试模块至少包括:第一缓存模块和第二缓存模块;其中,所述第一缓存模块与所述第二缓存模块电连接;所述第一缓存模块用于存储软件调试的数据信息;所述第二缓存模块用于存储与软件调试的数据信息对应的时间信息。

3、可选地,该软件辅助调试模块还包括第三缓存模块,所述第三缓存模块分别与所述第一缓存模块和所述第二缓存模块电连接;所述第三缓存模块用于存储软件调试的最后一笔数据信息和对应的时间信息。

4、可选地,所述第三缓存模块的存储空间仅能存储一笔数据信息和对应的时间信息。

5、可选地,所述第一缓存模块和所述第二缓存模块的存储空间均大于所述第三缓存模块的存储空间。

6、可选地,所述第一缓存模块、所述第二缓存模块和所述第三缓存模块为数据缓存器。

7、可选地,该软件辅助调试模块还包括时钟模块、写使能模块和逻辑与模块;其中,所述时钟模块与所述逻辑与模块的第一输入端电连接,所述写使能模块分别与所述逻辑与模块的第二输入端和所述第一缓存模块电连接;所述逻辑与模块的输出端与所述第二缓存模块电连接。

8、可选地,所述时钟模块包括全局时钟和异步桥;所述全局时钟与所述异步桥电连接,所述异步桥与所述逻辑与模块的第一输入端电连接。

9、可选地,该软件辅助调试模块还包括apb接口;所述apb接口分别与所述第一缓存模块和所述第二缓存模块电连接。

10、可选地,该软件辅助调试模块还包括系统总线接口,所述总线接口与所述第一缓存模块电连接。

11、根据本发明的另一方面,提供了一种芯片,该芯片包括如第一方面所述的软件辅助调试模块。

12、本发明实施例的技术方案,通过提供一种软件辅助调试模块和芯片,该软件辅助调试模块至少包括:第一缓存模块和第二缓存模块;其中,第一缓存模块与第二缓存模块电连接;第一缓存模块用于存储软件调试的数据信息;第二缓存模块用于存储与软件调试的数据信息对应的时间信息。由此可知,通过该软件辅助调试模块可以实现对芯片进行软件调试,且在调试时,通过设置第一缓存模块实时存储软件调试的数据信息,并且还设置第二缓存模块实时存储与软件调试的数据信息对应的时间信息。从而可以实现当软件调试出错时,通过第一缓存模块和第二缓存模块追溯到出错信息的具体位置、内容以及出错时间。此外,该软件辅助调试模块的结构简单,易于实现和操作。

13、应当理解,本部分所描述的内容并非旨在标识本发明的实施例的关键或重要特征,也不用于限制本发明的范围。本发明的其它特征将通过以下的说明书而变得容易理解。

技术特征:

1.一种软件辅助调试模块,其特征在于,至少包括:第一缓存模块和第二缓存模块;其中,所述第一缓存模块与所述第二缓存模块电连接;所述第一缓存模块用于存储软件调试的数据信息;所述第二缓存模块用于存储与软件调试的数据信息对应的时间信息。

2.根据权利要求1所述的软件辅助调试模块,其特征在于,还包括第三缓存模块,所述第三缓存模块分别与所述第一缓存模块和所述第二缓存模块电连接;所述第三缓存模块用于存储软件调试的最后一笔数据信息和对应的时间信息。

3.根据权利要求2所述的软件辅助调试模块,其特征在于,所述第三缓存模块的存储空间仅能存储一笔数据信息和对应的时间信息。

4.根据权利要求2所述的软件辅助调试模块,其特征在于,所述第一缓存模块和所述第二缓存模块的存储空间均大于所述第三缓存模块的存储空间。

5.根据权利要求2所述的软件辅助调试模块,其特征在于,所述第一缓存模块、所述第二缓存模块和所述第三缓存模块为数据缓存器。

6.根据权利要求2所述的软件辅助调试模块,其特征在于,还包括时钟模块、写使能模块和逻辑与模块;其中,所述时钟模块与所述逻辑与模块的第一输入端电连接,所述写使能模块分别与所述逻辑与模块的第二输入端和所述第一缓存模块电连接;所述逻辑与模块的输出端与所述第二缓存模块电连接。

7.根据权利要求6所述的软件辅助调试模块,其特征在于,所述时钟模块包括全局时钟和异步桥;所述全局时钟与所述异步桥电连接,所述异步桥与所述逻辑与模块的第一输入端电连接。

8.根据权利要求1所述的软件辅助调试模块,其特征在于,还包括apb接口;所述apb接口分别与所述第一缓存模块和所述第二缓存模块电连接。

9.根据权利要求1所述的软件辅助调试模块,其特征在于,还包括系统总线接口,所述总线接口与所述第一缓存模块电连接。

10.一种芯片,其特征在于,包括如权利要求1-9任一项所述的软件辅助调试模块。

技术总结

本发明公开了一种软件辅助调试模块和芯片。该软件辅助调试模块至少包括:第一缓存模块和第二缓存模块;其中,第一缓存模块与第二缓存模块电连接;第一缓存模块用于存储软件调试的数据信息;第二缓存模块用于存储与软件调试的数据信息对应的时间信息。由此可知,通过该软件辅助调试模块可以实现对芯片进行软件调试,且在调试时,通过设置第一缓存模块实时存储软件调试的数据信息,并且还设置第二缓存模块实时存储与软件调试的数据信息对应的时间信息。从而可以实现当软件调试出错时,通过第一缓存模块和第二缓存模块追溯到出错信息的具体位置、内容以及出错时间。此外,该软件辅助调试模块的结构简单,易于实现和操作。

技术研发人员:许锦,姜一舟,张丰,张吉鸿

受保护的技术使用者:芯砺智能科技(江苏)有限公司

技术研发日:

技术公布日:2024/2/19

- 还没有人留言评论。精彩留言会获得点赞!