一种4比特精确查找表乘法器

本发明涉及精确乘法器,特别是涉及一种4比特精确查找表乘法器。

背景技术:

1、随着工艺的发展,集成电路的效率越来越高,体积越来越小,但是在这个过程中集成电路的功耗逐渐成为了制约集成电路发展的瓶颈。因此,降低集成电路的功耗成为了目前需要突破的关键问题。现有相当一部分应用中存在了大量乘法运算,比如机器学习、数据处理和多媒体等,而乘法的功耗占据了应用整体功耗的大部分。所以通过降低应用中的乘法器的功耗可以在一定程度上降低整体应用的功耗,进而提升应用的效率。

2、查找表乘法器是一种基于fpga(field programmable gatearray,现场可编程门阵列)的乘法器。对于现有精确查找表乘法器来说,制约精确查找表乘法器的功耗的因素主要是延迟和面积。精确查找表乘法器的延迟主要受该乘法器的关键路径影响,而面积则主要受查找表的数量影响。通过提高查找表的利用率和优化查找表的排布可以减短查找表乘法器的关键路径和减少查找表的数量。目前的精确4比特查找表乘法器,对于查找表的利用率不高,对于查找表的排布也还有很大的优化空间,以上两点导致了其过大的延迟和面积,进而使其功耗过大,最终制约了该乘法器在应用中的硬件效率。

技术实现思路

1、本发明的目的是提供一种4比特精确查找表乘法器,降低乘法器的计算延迟及功耗。

2、为实现上述目的,本发明提供了如下方案:

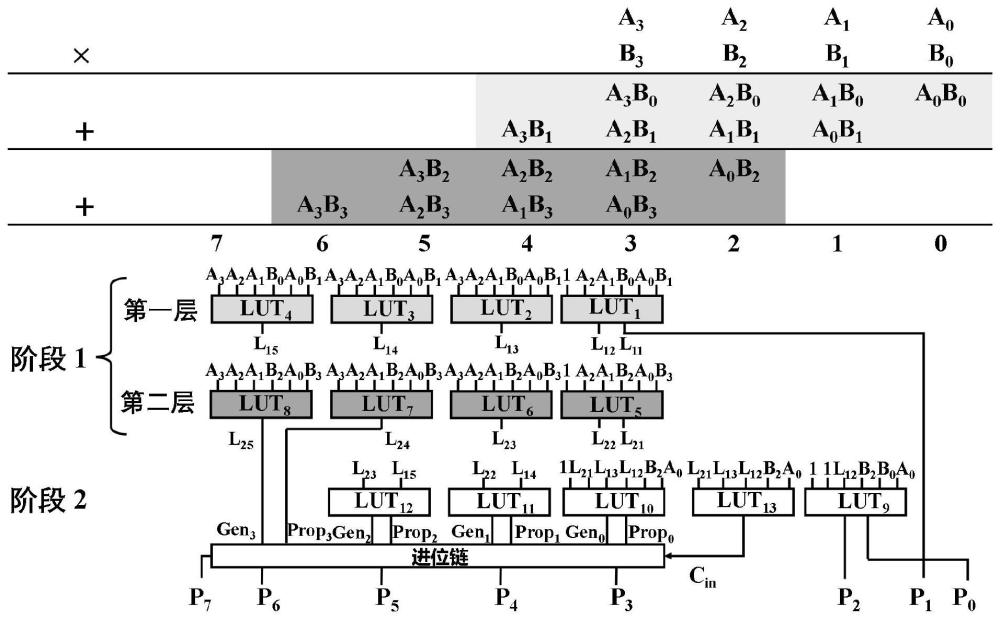

3、本发明提供一种4比特精确查找表乘法器,所述4比特精确查找表乘法器的乘数及被乘数均为四位比特;所述4比特精确查找表乘法器包括十三个查找表及一个进位链;

4、其中,第一查找表、第二查找表、第三查找表及第四查找表构成第一乘积计算层,所述第一乘积计算层用于将所述乘数与所述被乘数中的低位两位比特进行运算,以得到第一部分积信号集合;

5、第五查找表、第六查找表、第七查找表及第八查找表构成第二乘积计算层;所述第二乘积计算层用于将所述乘数与所述被乘数中的高位两位比特进行运算,以得到第二部分积信号集合;所述第一乘积计算层与所述第二乘积计算层为并行运算;

6、第九查找表、第十查找表、第十一查找表、第十二查找表、第十三查找表及所述进位链构成进位信号压缩层;所述进位信号压缩层用于基于所述第一部分积信号集合及所述第二部分积信号集合,依次进行进位信号计算及信号压缩,以得到最终乘积结果。

7、根据本发明提供的具体实施例,本发明公开了以下技术效果:

8、本发明公开一种4比特精确查找表乘法器,通过设置第一乘积计算层、第二乘积计算层及进位信号压缩层,且,第一乘积计算层与第二乘积计算层并行运算,从而能够达到更短的关键路径,实现更低的延迟。本发明仅采用十三个查找表及一个进位链即可实现,相较于现有乘法器所采用的15个查找表,乘法器的面积更小,更小的面积意味着更高的查找表利用率,降低了计算的功耗。综上,本发明优化了乘法器中查找表的排布,提高了查找表的利用率,从而降低了乘法器的延迟,减少了乘法器的面积,进而降低了乘法器的功耗,最终提升了乘法器的硬件效率。

技术特征:

1.一种4比特精确查找表乘法器,其特征在于,所述4比特精确查找表乘法器的乘数及被乘数均为四位比特;所述4比特精确查找表乘法器包括十三个查找表及一个进位链;

2.根据权利要求1所述的4比特精确查找表乘法器,其特征在于,所述进位信号压缩层的具体结构为:

3.根据权利要求1所述的4比特精确查找表乘法器,其特征在于,所述乘数的四位比特为a3a2a1a0;所述被乘数的四位比特为b3b2b1b0;

4.根据权利要求1所述的4比特精确查找表乘法器,其特征在于,所述乘数的四位比特为a3a2a1a0;所述被乘数的四位比特为b3b2b1b0;

5.根据权利要求2所述的4比特精确查找表乘法器,其特征在于,所述乘数的四位比特为a3a2a1a0;所述被乘数的四位比特为b3b2b1b0;所述第一部分积信号集合包括l12、l13;所述第二部分积集合包括l21;

6.根据权利要求2所述的4比特精确查找表乘法器,其特征在于,所述乘数的四位比特为a3a2a1a0;所述被乘数的四位比特为b3b2b1b0;所述第一部分积信号集合包括l13、l14、l15;所述第二部分积集合包括l21、l22、l23;

7.根据权利要求1所述的4比特精确查找表乘法器,其特征在于,所述第一查找表为六输入双输出查找表;所述第二查找表为六输入单输出查找表;所述第三查找表为六输入单输出查找表;所述第四查找表为六输入单输出查找表;所述第五查找表为六输入双输出查找表;所述第六查找表为六输入单输出查找表;所述第七查找表为六输入单输出查找表;所述第八查找表为六输入单输出查找表;所述第九查找表为六输入双输出查找表;所述第十查找表为六输入双输出查找表;所述第十一查找表为六输入双输出查找表;所述第十二查找表为六输入双输出查找表;所述第十三查找表为五输入单输出查找表。

技术总结

本发明公开一种4比特精确查找表乘法器,涉及精确乘法器技术领域,其中,第一查找表、第二查找表、第三查找表及第四查找表构成第一乘积计算层,用于将乘数与被乘数中的低位两位比特进行运算,以得到第一部分积信号集合;第五查找表、第六查找表、第七查找表及第八查找表构成第二乘积计算层,用于将乘数与被乘数中的高位两位比特进行运算,以得到第二部分积信号集合;第九查找表、第十查找表、第十一查找表、第十二查找表、第十三查找表及进位链构成进位信号压缩层;进位信号压缩层用于基于第一部分积信号集合及第二部分积信号集合,依次进行进位信号计算及信号压缩,以得到最终乘积结果。本发明降低了乘法器的计算延迟及功耗。

技术研发人员:周其林,郭怡,陈秀

受保护的技术使用者:云南大学

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!