一种兼顾常态低速和短时高速的信号处理板卡设计方法

本发明涉及一种兼顾常态低速和短时高速的信号处理板卡设计方法,属于遥感通信设备领域。

背景技术:

1、随着微电子技术的发展,越来越多的微小卫星被发射到太空中。微小卫星可以搭载多种遥感载荷,通过组网的方式进行对地观测,能够减少重访时间,且网络整体的可靠性大于传统单颗大卫星的可靠性。微小卫星的工作要求和成本特性决定了它适合大量生产。如果在生产过程中,将星载/机载的信号处理板卡标准化,适配多种载荷,就能够解决一定程度的生产成本问题。

技术实现思路

1、本发明提供一种兼顾常态低速和短时高速的信号处理板卡设计方法,设计的处理板的整体功耗能满足微小卫星的星载电源的要求,稳定性也可以满足太空中辐射环境的要求。

2、本发明采取的技术方案是一种兼顾常态低速和短时高速的信号处理板卡设计方法,包括:

3、确定信号处理板卡的三个处理单元,三个处理单元的类型至少包括dsp、fpga、soc;

4、将dsp、fpga划分到低功耗域,soc划分到高性能域;

5、低功耗域运行可靠性和常时开机任务;高性能域运行性能需求任务;

6、规划信号处理板卡的系统内部之间的连接方式和总线类型,规划信号处理板卡的系统与外部通信的接口类型;

7、规划信号处理板卡的pcb叠层设计、具体布局。

8、优化的,上述兼顾常态低速和短时高速的信号处理板卡设计方法,将dsp、fpga处理单元的存储器配备为可靠性存储器;soc处理单元的存储器配备为存储量存储器。

9、优化的,上述兼顾常态低速和短时高速的信号处理板卡设计方法,低功耗域保持持续开机运行状态;

10、高性能域的电源功耗分成多个等级,各个等级包括:

11、有高性能任务运行时,按照最大功耗或者适合任务的功耗运行;

12、在没有任务时,高性能域进入休眠状态;

13、能源紧急的情况下,高性能域整体进入关机状态。

14、优化的,上述兼顾常态低速和短时高速的信号处理板卡设计方法,低功耗域的dsp、fpga搭配的存储芯片包括eeprom、mram、sdram、raw-flash。

15、优化的,上述兼顾常态低速和短时高速的信号处理板卡设计方法,dsp与fpga之间通过emif总线和gpio连接;dsp与存储芯片之间通过emif总线连接;fpga与soc之间通过spi总线、自定义总线或gpio连接。

16、优化的,上述兼顾常态低速和短时高速的信号处理板卡设计方法,信号处理板卡的系统与外部通信的接口类型包括rs422和lvds接口,rs422和lvds接口都连接到fpga上。

17、优化的,上述兼顾常态低速和短时高速的信号处理板卡设计方法,信号处理板卡的pcb叠层设计时,采用十四层叠层设计;其中,第一层为顶层,第十四层为底层,第二、九、十二层为电源层,第三、五、七、十一层为信号层,第四、六、八、十、十三层为地层。

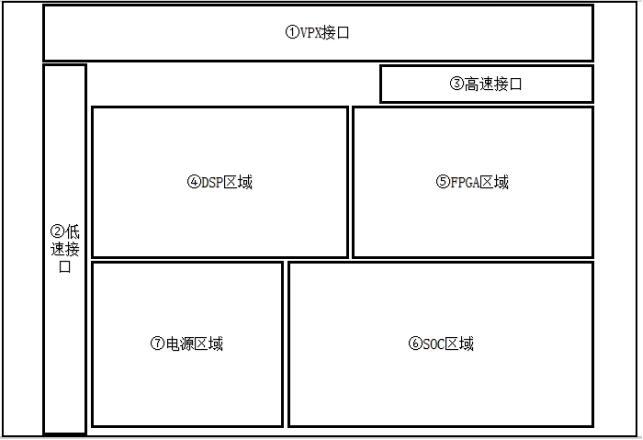

18、优化的,上述兼顾常态低速和短时高速的信号处理板卡设计方法,板卡尺寸采用vpx协议规定的尺寸,包括7个布局区域;一号区域为vpx接口区域,位于pcb的上侧区域;二号区域为低速接口区域,位于pcb的左侧区域;三号区域为高速接口区域,位于pcb的右上侧;四号区域为dsp区域,位于pcb的左侧;五号区域为fpga区域,位于pcb的右侧;六号区域为soc区域,位于pcb的右下侧;七号区域为电源区域,位于pcb的左下侧。

19、优化的,上述兼顾常态低速和短时高速的信号处理板卡设计方法,低速接口区域包括jtag插座j1、j2、j3,db9插座j4,rs422排针j5;

20、高速接口区域包括电平转换芯片u17~u20,lvds排针j6;

21、dsp区域包括dsp处理器u1,sdram芯片u9、u25,marm芯片u29、u30;

22、fpga区域包括fpga芯片u2,nand-flash芯片u16、u23、u24,boot选择开关sw2~sw4,看门狗芯片u6,有源时钟u15;

23、soc区域包括zynq芯片u3,ddr3芯片u27、u28,sd卡插座u26,rj45插座u34,phy芯片u33,phy芯片时钟u13,串口插针j8,soc电源区域开关sw7,有源时钟芯片u5,spi-flash芯片u8,总线开关u11、u12,boot选择开关sw8、sw9;

24、电源区域包括电源插座j7,电源总开关sw1,dc-dc芯片u22、u31、u35,ldo芯片u7。除了上述芯片之外,该pcb还包括488个电容和256个电阻。

25、优化的,上述兼顾常态低速和短时高速的信号处理板卡设计方法,所采用的芯片可以根据具体的任务来更改;

26、dsp选用要求是,峰值功耗不超过3w,且带有emif接口,根据工作环境的不同,可以选用宇航级dsp,用于星上数据处理;也可以选用工业级或者军用级dsp,用于机载数据处理;

27、fpga选用的芯片类型可以是反熔丝型,用于星上数据处理;也可以是sram型,用于机载数据处理;

28、soc选用类型推荐为xilinx公司的zynq系列或者zynqmpsoc系列。

29、本申请的优点在于:本申请采用一种兼顾常态低速和短时高速的信号处理板卡设计方法,使用此方法设计的信号处理板能处理多种星载或机载载荷的数据,它所搭载的处理器除了能部署常规算法之外,还可以部署深度学习算法。并且使用本申请的方法设计的低功耗、高可靠性系统与高性能系统融合的嵌入式数据处理板,便于按照任务的性能要求和稳定性要求,将任务卸载到不同的处理器上,能在恶劣的辐射环境中能够保证高可靠性系统的长时间稳定、高性能系统的短时间稳定。

技术特征:

1.一种兼顾常态低速和短时高速的信号处理板卡设计方法,其特征在于:包括,

2.根据权利要求1所述的兼顾常态低速和短时高速的信号处理板卡设计方法,其特征在于:将dsp、fpga处理单元的存储器配备为可靠性存储器;soc处理单元的存储器配备为存储量存储器。

3.根据权利要求1所述的兼顾常态低速和短时高速的信号处理板卡设计方法,其特征在于:

4.根据权利要求2所述的兼顾常态低速和短时高速的信号处理板卡设计方法,其特征在于:低功耗域的dsp、fpga搭配的存储芯片包括eeprom、mram、sdram、raw-flash。

5.根据权利要求1所述的兼顾常态低速和短时高速的信号处理板卡设计方法,其特征在于:dsp与fpga之间通过emif总线和gpio连接;dsp与存储芯片之间通过emif总线连接;fpga与soc之间通过spi总线、自定义总线或gpio连接。

6.根据权利要求5所述的兼顾常态低速和短时高速的信号处理板卡设计方法,其特征在于:信号处理板卡的系统与外部通信的接口类型包括rs422和lvds接口,rs422和lvds接口都连接到fpga上。

7.根据权利要求1所述的兼顾常态低速和短时高速的信号处理板卡设计方法,其特征在于:信号处理板卡的pcb叠层设计时,采用十四层叠层设计;其中,第一层为顶层,第十四层为底层,第二、九、十二层为电源层,第三、五、七、十一层为信号层,第四、六、八、十、十三层为地层。

技术总结

本申请公开了一种兼顾常态低速和短时高速的信号处理板卡设计方法,属于遥感通信设备领域,解决了现有技术中板卡标准化程度低、成本较高、可靠性和稳定性低的问题。本申请的方法包括:确定信号处理板卡的三个处理单元,三个处理单元的类型至少包括DSP、FPGA、SOC;将DSP、FPGA划分到低功耗域,SOC划分到高性能域;低功耗域运行可靠性和常时开机任务;高性能域运行性能需求任务;规划信号处理板卡的系统内部之间的连接方式和总线类型,规划信号处理板卡的系统与外部通信的接口类型;规划信号处理板卡的PCB叠层设计、具体布局。使用本申请的方法设计的处理板的整体功耗能满足微小卫星的星载电源的要求,稳定性也可以满足太空中辐射环境的要求。

技术研发人员:殷晓斌,胡易成,解歆钰

受保护的技术使用者:中国海洋大学三亚海洋研究院

技术研发日:

技术公布日:2024/1/5

- 还没有人留言评论。精彩留言会获得点赞!