高速总线通讯拓扑、设备、架构以及系统的制作方法

本申请涉及plc系统,尤其涉及一种高速总线通讯拓扑、设备、架构以及系统。

背景技术:

1、大型plc控制系统,一般现场应用的机架上会有控制器和冗余模块、通信模块的高速通信,并且机架上的模块均支持热插拔,方便维修更换。传统plc高速背板总线一般有lvds(low-voltage differential signaling,低电压差分信号)总线、pcie(eripheralcomponent interconnect express,高速串行计算机扩展)总线、以太网总线、485总线、can(controller area network,控制器局域网)总线等。

2、传统的pcie总线拓扑结构下,通常可以满足数据传输速率的要求,但是因为连接器、传输线、芯片管脚等均存在寄生电感、电容,模块热插拔过程中很容易产生的震荡波形,进而产生浪涌电压和冲击电流,这对芯片管脚损害较大,尤其是芯片与连接器直连的管脚。因此传统pcie总线架构方案不支持频繁热插拔。

技术实现思路

1、本申请的主要目的在于提供一种高速总线通讯拓扑、设备、架构以及系统,旨在解决现有技术中传统pcie总线拓扑方案不支持频繁热插拔的技术问题。

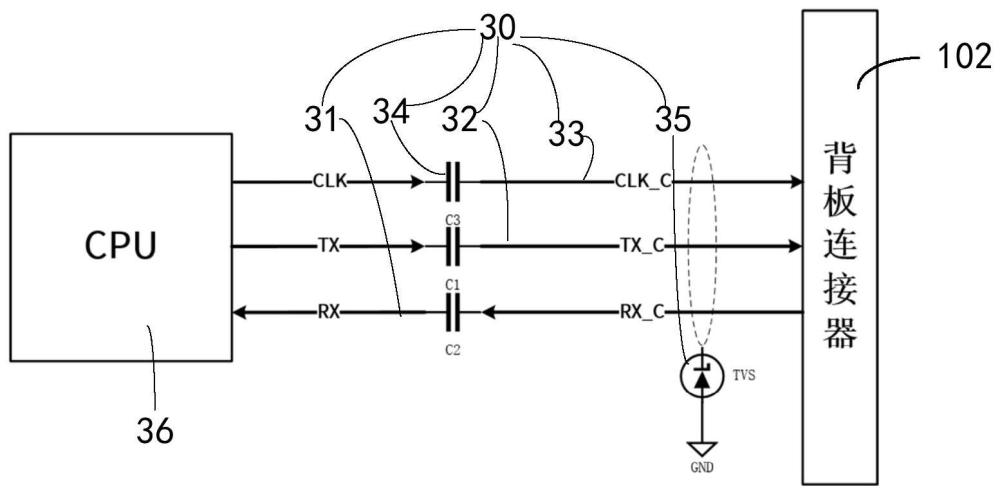

2、为实现上述目的,本申请提供一种高速总线通讯拓扑,所述高速总线通讯拓扑包括:

3、控制单元以及背板连接器,所述控制单元与所述背板连接器之间设置有至少一个数据通信链路,每个所述数据通信链路上设置有电容单元以及静电防护单元,所述电容单元的第一端与所述控制单元连接,所述电容单元的第二端与所述静电防护单元的第一端连接,所述静电防护单元的第二端与所述背板连接器和地连接。

4、可选地,所述电容单元包括至少一个电容,每个所述电容的第一端与所述控制单元连接,每个所述电容的第二端与所述静电防护单元的第一端连接。

5、可选地,所述静电防护单元包括至少一个瞬态电压抑制二极管,每个所述瞬态电压抑制二极管的第一端与所述电容连接,每个所述瞬态电压抑制二极管的第二端与所述背板连接器和地连接。

6、可选地,所述数据通信链路为serdes总线型的通信链路。

7、可选地,所述控制单元为cpu或者fpga。

8、此外,为实现上述目的,本申请还提供一种高速总线通讯设备,所述高速总线通讯设备包括高速总线通讯拓扑。

9、此外,为实现上述目的,本申请还提供一种高速总线通讯架构,高速总线通讯架构包括控制器、机架背板以及至少一个扩展模块,所述控制器和所述扩展模块均包括高速总线通讯拓扑,所述控制器通过所述机架背板与至少一个所述扩展模块连接。

10、所述控制器内部的数据通信链路的数量大于或等于所有扩展模块内的数据通信链路的总数。

11、可选地,所述控制器和所述扩展模块上设置有背板连接器母头,所述机架背板上设置有背板连接器公头,所述背板连接器母头与所述背板连接器公头配合,以使所述控制器和所述扩展模块可插拔设置在所述机架背板上。

12、可选地,所述扩展模块包括冗余模块、通信模块以及电源模块中的至少一种。

13、此外,为实现上述目的,本申请还提供一种高速总线通讯系统,所述高速总线通讯系统包括上位机、被控设备以及上述任一项所述高速总线通讯架构,所述高速总线通讯架构分别与所述上位机以及所述被控设备连接。

14、本申请提供一种高速总线通讯拓扑,所述高速总线通讯拓扑包括:控制单元以及背板连接器,所述控制单元与所述背板连接器之间设置有至少一个数据通信链路,每个所述数据通信链路上设置有电容单元以及静电防护单元,所述电容单元的第一端与所述控制单元连接,所述电容单元的第二端与所述静电防护单元的第一端连接,所述静电防护单元的第二端与所述背板连接器和地连接。本申请提供的高速总线通讯拓扑在数据通信链路上增加了电容单元以及静电防护单元,电容单元以及静电防护单元可以有效隔离模块热插拔时产生的冲击电流,旁路热插拔过程中产生的浪涌电压,从而实现模块的频繁热插拔。

技术特征:

1.一种高速总线通讯拓扑,其特征在于,所述高速总线通讯拓扑包括:

2.如权利要求1所述的高速总线通讯拓扑,其特征在于,所述电容单元包括至少一个电容,每个所述电容的第一端与所述控制单元连接,每个所述电容的第二端与所述静电防护单元的第一端连接。

3.如权利要求2所述的高速总线通讯拓扑,其特征在于,所述静电防护单元包括至少一个瞬态电压抑制二极管,每个所述瞬态电压抑制二极管的第一端与所述电容连接,每个所述瞬态电压抑制二极管的第二端与所述背板连接器和地连接。

4.如权利要求3所述的高速总线通讯拓扑,其特征在于,所述数据通信链路为serdes总线型的通信链路。

5.一种高速总线通讯设备,其特征在于,所述高速总线通讯设备包括权利要求1-4中任一项所述的高速总线通讯拓扑。

6.一种高速总线通讯架构,其特征在于,所述高速总线通讯架构包括控制器、机架背板以及至少一个扩展模块,所述控制器和所述扩展模块均包括权利要求1-4中任一项所述的高速总线通讯拓扑,所述控制器通过所述机架背板与至少一个所述扩展模块连接。

7.如权利要求6所述的高速总线通讯架构,其特征在于,所述控制器内部的数据通信链路的数量大于或等于所有扩展模块内的数据通信链路的总数。

8.如权利要求7所述的高速总线通讯架构,其特征在于,所述控制器和所述扩展模块上设置有背板连接器母头,所述机架背板上设置有背板连接器公头,所述背板连接器母头与所述背板连接器公头配合,以使所述控制器和所述扩展模块可插拔设置在所述机架背板上。

9.如权利要求7所述的高速总线通讯架构,其特征在于,所述扩展模块包括冗余模块、通信模块以及电源模块中的至少一种。

10.一种高速总线通讯系统,其特征在于,所述高速总线通讯系统包括上位机、被控设备以及如权利要求6-9中任一项所述高速总线通讯架构,所述高速总线通讯架构分别与所述上位机以及所述被控设备连接。

技术总结

本申请公开了一种高速总线通讯拓扑、设备、架构以及系统,涉及PLC系统技术领域,通过在所述控制单元与所述背板连接器之间设置至少一个数据通信链路,并在每个所述数据通信链路上设置电容单元以及静电防护单元,其中,所述电容单元的第一端与所述控制单元电连接,所述电容单元的第二端与所述静电防护单元的第一端电连接,所述静电防护单元的第二端与所述背板连接器和地连接。本申请可以解决传统PCIE总线拓扑方案不支持频繁热插拔的技术问题。

技术研发人员:赵腾善

受保护的技术使用者:深圳市汇川技术股份有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!