一种芯片测试模式防护电路及防护方法与流程

本发明涉及soc芯片,具体涉及一种芯片测试模式防护电路及防护方法。

背景技术:

1、通用soc芯片一般都具备测试电路,用于芯片制造后的cp测试和芯片封装后的ft测试。测试内容一般包括电流、电压、时序和功能的验证,用于筛选出制造与封装之后不合格的芯片。通用soc芯片一般具备正常工作模式和测试模式,而正常工作模式和测试模式一般通过芯片默写特定的输入管脚的状态进行区分。与正常工作模式相比,测试模式一般具有对soc内部更大的资源访问权限,从芯片安全的角度考虑,芯片测试模式可能成为攻击者可以利用的安全漏洞。

2、在芯片测试模式保护方面,目前大多数具备测试模式的芯片没有设计关闭测试模式的保护机制。大多数具备关闭测试模式保护机制的芯片,做不到永久关闭测试模式的功能,或者通过某些特定的芯片攻击手段可以绕过测试模式保护机制,重新打开芯片测试模式。

技术实现思路

1、针对现有技术中的缺陷,本发明提供一种芯片测试模式防护电路及防护方法,用以解决目前芯片的测试模式无法关闭或者容易被攻击导致重新打开的问题。

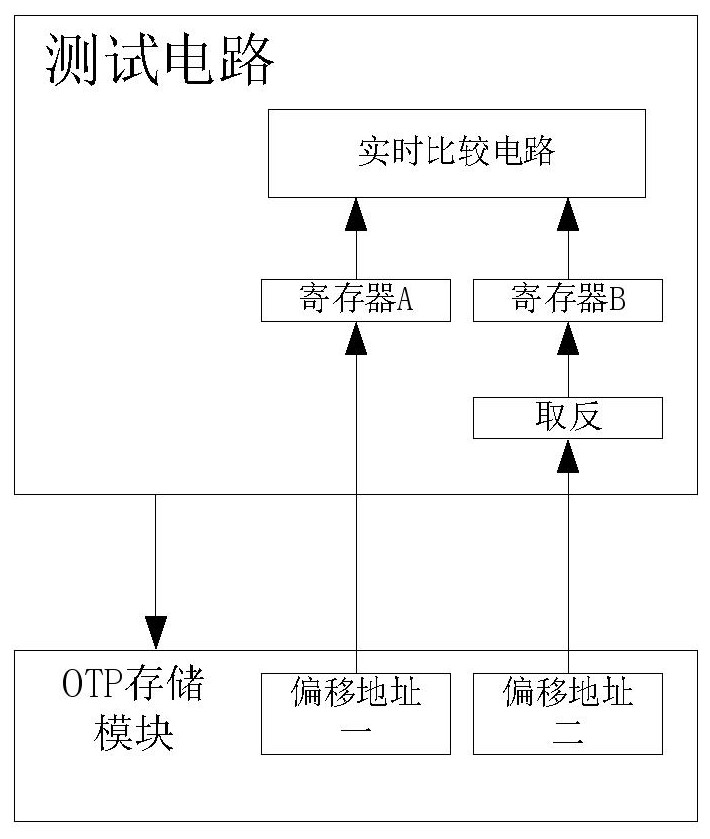

2、第一方面,本发明提供的一种芯片测试模式防护电路,包括:

3、otp存储模块,所述otp存储模块的不同偏移地址内存储有控制字;

4、两组寄存器,分别和所述otp存储模块连接,其中一组寄存器用于存储从所述otp存储模块加载的控制字,另一组寄存器用于存储从所述otp存储模块加载后取反的控制字;所述寄存器由芯片的测试电路进行读写操作。

5、由上述技术方案可知,本发明提供的芯片防护电路,基于otp存储模块只允许编程一次,一旦被编程,数据永久有效的特点,使得存储在otp中的测试模式控制字不会被二次修改;可有效抵抗侵入式攻击与半侵入式攻击对于测试模式保护电路的攻击,从而保证芯片测试模式的不可逆性。

6、可选地,所述otp存储模块的不同偏移地址不连续。偏移地址不连续意味着两个四字节的控制字在物理上的位置也不连续,目的是增加侵入式攻击同时对两个控制字进行物理篡改的难度。

7、可选地,控制字的取反操作是由芯片的测试电路完成的。

8、第二方面,本发明提供的soc芯片,包括第一方面任一种可能实现方式的芯片测试模式防护电路。

9、第三方面,本发明提供的一种芯片测试模式防护方法,基于第二方面提供的soc芯片,包括:

10、从otp存储模块预设的不同偏移地址加载数据至两组寄存器;

11、在两组寄存器加载获得的数据为测试写入控制字及测试写入控制字取反,或在两组寄存器加载获得的数据不互反时,禁止进入测试模式。

12、由上述技术方案可知,本发明提供的芯片测试模式防护方法,在面对测试模式保护电路的攻击时,一旦控制字被写入otp存储模块中,可有效保证测试模式不可逆性,提高芯片安全性。

13、可选地,在测试写入控制字写入所述otp存储模块之前,所述otp存储模块为默认值0,所述方法还包括:

14、在两组寄存器加载获得的数据分别为0x00000000和0xffffffff时,进入cp测试阶段或ft测试阶段进行测试。

15、可选地,芯片的测试电路向所述otp存储模块的不同偏移地址写入测试写入控制字是在完成ft测试阶段之后。

16、第四方面,本发明提供的一种芯片测试模式防护装置,用于执行第三方面所提供的芯片测试模式防护方法。

17、采用上述技术方案,本申请具有如下有益效果:

18、(1)本发明的芯片测试模式防护电路采用otp存储模块,配合两组寄存器用于对测试完成之后写入的控制字实现双备份,其中两组寄存器中存储的测试写入控制字是互反的,可以有效抵抗侵入式攻击与半侵入式攻击对于测试防护电路的攻击,从而保证芯片测试模式的不可逆性。

19、(2)本发明提供的芯片测试模式防护方法,通过对分别存储于两组寄存器的互反的控制字进行实时比较,一旦完成ft测试阶段写入控制字后,增加了侵入式攻击对于控制字的物理纂改难度,提高了芯片的安全性。

技术特征:

1.一种芯片测试模式防护电路,其特征在于,包括:

2.根据权利要求1所述的电路,其特征在于,所述otp存储模块的不同偏移地址不连续。

3.根据权利要求2所述的电路,其特征在于,不同偏移地址内存储的是四字节控制字。

4.根据权利要求3所述的电路,其特征在于,控制字的取反操作是由芯片的测试电路完成的。

5.一种soc芯片,其特征在于,包括权利要求1-4任一所述的芯片测试模式防护电路。

6.一种芯片测试模式防护方法,其特征在于,基于权利要求5所述的soc芯片,包括:

7.根据权利要求6所述的方法,其特征在于,在所述测试写入控制字写入所述otp存储模块之前,所述otp存储模块为默认值0,所述方法还包括:

8.根据权利要求7所述的方法,其特征在于,芯片的测试电路向所述otp存储模块的不同偏移地址写入所述测试写入控制字是在完成ft测试阶段之后。

9.一种芯片测试模式防护装置,其特征在于,用于执行权利要求6-8任一所述的芯片测试模式防护方法。

技术总结

本发明属于SOC芯片技术领域,提供了一种芯片测试模式防护电路及防护方法,其中防护电路包括OTP存储模块和两组寄存器,OTP存储模块的不同偏移地址内存储有控制字;两组寄存器分别和OTP存储模块连接,其中一组寄存器用于存储从OTP存储模块加载的控制字,另一组寄存器用于存储从OTP存储模块加载后取反的控制字;寄存器由芯片的测试电路进行读写操作,CPU不可对其访问,控制字的取反操作可直接由芯片的测试电路完成。本发明的芯片测试模式防护电路采用OTP存储模块,配合两组寄存器用于对测试完成之后写入的控制字实现双备份,防护电路能有效抵抗侵入式攻击与半侵入式攻击,提高芯片测试模式的安全性。

技术研发人员:顾申,孙超,卓越,李成业

受保护的技术使用者:国创芯科技(江苏)有限公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!