串行总线数据自主解析控制器及工作方法与流程

本发明涉及数字电路的,尤其涉及一种串行总线数据自主解析控制器及工作方法。

背景技术:

1、串行总线(包含rs422、rs232和rs485)是一种常用的标准总线接口,具有结构简单、灵活性高等特点,在航空航天领域,机载设备之间存在大量的设备控制串行总线接口。目前,现有的串行数据解析方法是在ram中建立环形缓冲区,处理器循环查询fpga中uart协议ip核的状态信息和数据信息,并将数据存储在环形缓冲区中,依据总线数据icd解析数据,并且考虑到机载设备往往包含多路串行总线接口,因此串行数据解析会造成处理器对fpga和ram等外设的大量访问,导致处理器时间开销增大,明显降低了处理器的使用效率。

2、如何降低处理器解析串行数据的时间开销,提升其使用失效具有重要的工程意义,机载设备通常使用fpga集成uart协议ip核,实现串行总线的协议转换功能,需要设计一种串行总线数据自主解析控制器,以实现了串行数据的自主解析,降低了处理器进行串行数据解析的时间开销,显著提升了处理器使用效率。

技术实现思路

1、有鉴于此,本发明提供的串行总线数据自主解析控制器,降低了处理器进行串行数据解析的时间开销,显著提升了处理器使用效率。

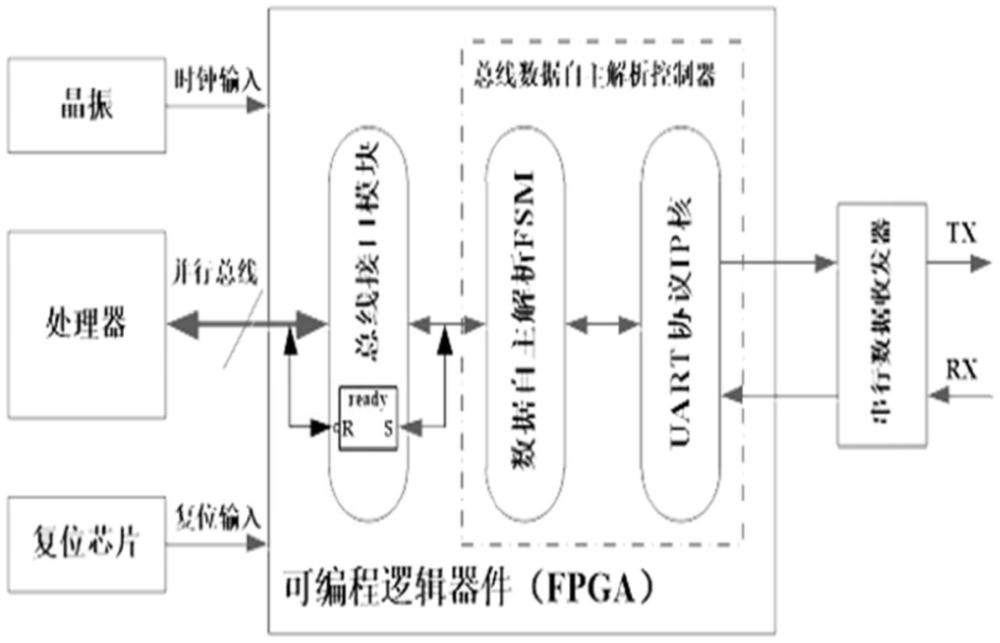

2、一种串行总线数据自主解析控制器,串行总线数据自主解析控制器基于可编程逻辑器件所实现,包含数据自主解析状态机和与所述数据自主解析状态机通讯连接的uart协议ip核,可编程逻辑器件包括总线接口模块,其中,

3、所述数据自主解析状态机根据串行总线数据icd解析并存储数据;

4、所述数据自主解析状态机fsm与总线接口模块相连接,所述总线接口模块通过并行总线与外部的处理器相连接,处理器通过总线接口模块能够读取所述数据自主解析状态机解析并存储的数据;

5、所述uart协议ip核通过单向串行数据线与总线收发器相连接,用于按照串行总线的帧格式实现数据的串并转换;

6、所述数据自主解析状态机周期查询uart协议ip核的状态信息,控制数据自主解析状态机实现状态切换,并根据总线数据icd解析数据,且将存储解析后的数据供处理器读取。

7、其次提供一种串行总线数据自主解析控制器的工作方法,应用在上述所述的串行总线数据解析控制器中,所述数据自主解析状态机配置有临时数据存储区,所述数据自主解析状态机包含idle0、step1、step2、step3、step4和step5共6个状态,所述总线接口模块还包括固定数据存储区,所述工作方法,包括,

8、step0:所述数据自主解析状态机周期地获取uart协议ip核的状态信息,若,状态信息显示ip核接收缓冲区中无数据,则,继续停留在idle0;若,状态信息显示ip核接收缓冲区中有数据,则,将数据读出,且判断数据是否等于8’haa,如是,则跳转到step1,如否,则继续停留在idle0;

9、step1:所述数据自主解析状态机周期地获取uart协议ip核的状态信息,若,状态信息显示ip核接收缓冲区无数据,则,继续停留在step1,若,状态信息显示ip核接收缓冲区中有数据,则,将数据读出,且判断数据是否等于8’h55,如是,则跳转到step2,如否,则跳转到idle0;

10、step2:所述数据自主解析状态机周期地获取uart协议ip核的状态信息,若状态信息显示ip核接收缓冲区中无数据,则,继续停留在step2,若状态信息显示ip核接收缓冲区中有数据,则将数据读出,赋值给帧计数,并跳转到step3;

11、step3:所述数据自主解析状态机周期地获取uart协议ip核的状态信息,若,状态信息显示ip核接收缓冲区中无数据,则,继续停留在step3;若状态信息显示ip核接收缓冲区中有数据,则,将数据读出,赋值给包长和局部变量len,并跳转到step4;

12、step4:所述数据自主解析状态机周期地获取uart协议ip核的状态信息,若状态信息显示ip核接收缓冲区中无数据,则,继续停留在step4,若,状态信息显示ip核接收缓冲区中有数据,则,将数据读出,存储在所述临时数据存储区,同时,所述局部变量len自减1,并判断自减后的len是否等于0,如是,则跳转到step5,如否,则继续停留在step4;

13、step5:所述数据自主解析状态机周期地获取uart协议ip核的状态信息,若,状态信息显示ip核接收缓冲区中无数据,则,继续停留在step5;若,状态信息显示ip核接收缓冲区中有数据,则,将数据读出,赋值给校验和,并将所述临时数据存储区中的数据转存至所述固定数据存储区,并跳转到idle0。

14、有益效果

15、本发明在uart协议ip核的基础上,基于可编程逻辑器件设计了一种串行总线数据自主解析控制器,并依据总线数据icd设计了数据自主解析状态机,通过周期查询uart协议ip核,获取状态信息和数据,控制数据自主解析状态机切换,实现了串行数据的自主解析,减轻了处理器进行串行数据解析的时间开销,显著提升了处理器使用效率,可广泛应用于工业领域。

技术特征:

1.一种串行总线数据自主解析控制器,其特征在于,串行总线数据自主解析控制器基于可编程逻辑器件所实现,包含数据自主解析状态机和与所述数据自主解析状态机通讯连接的uart协议ip核,可编程逻辑器件包括总线接口模块,其中,

2.根据权利要求1所述的串行总线数据自主解析控制器,其特征在于,所述串行总线数据icd包括包头、帧计数、包长、数据和校验和。

3.根据权利要求1所述的串行总线数据自主解析控制器,其特征在于,所述总线接口模块包含用于指示数据自主解析过程是否完成的ready信号,其中,

4.根据权利要求1所述的串行总线数据自主解析控制器,其特征在于,数据自主解析状态机查询uart协议ip核状态信息的周期依据串行总线通讯波特率所确定,其中,

5.一种串行总线数据自主解析控制器的工作方法,应用在如权利要求1至4任意一项所述的串行总线数据解析控制器中,所述数据自主解析状态机配置有临时数据存储区,其特征在于,所述数据自主解析状态机包含idle0、step1、step2、step3、step4和step5共6个状态,所述总线接口模块还包括固定数据存储区,所述工作方法包括,

6.根据权利要求5所述的工作方法,其特征在于,所述step5中所述临时数据存储区中的数据转存至所述固定数据存储区,包括,

技术总结

本发明的串行总线数据自主解析控制器,属于数字电路领域。其在UART协议IP核的基础上,依据串行总线数据ICD,设计了数据自主解析状态机。串行总线数据自主解析控制器通过周期地查询UART协议IP核的状态寄存器和数据寄存器,控制数据自主解析状态机实现6个状态的切换,同时依据总线数据ICD解析串行数据,并存储在指定空间内供处理器读取。本发明针对处理器解析串行数据时间开销大的问题,依据总线数据ICD设计了数据自主解析状态机,实现了串行数据的自主解析,减轻了处理器进行串行数据解析的时间开销,显著提升了处理器使用效率,可广泛应用于工业领域。

技术研发人员:屈盼让,朱天,蔡晓乐,张倩倩,高伟,刘杨

受保护的技术使用者:中国航空工业集团公司西安航空计算技术研究所

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!