用于转移操作的硬件加速器和方法与流程

本公开总体上关于电子学,更具体地,本公开的实施例关于用于执行转移(offload)操作的硬件加速器。

背景技术:

1、处理器或处理器集合执行来自指令集(例如,指令集架构(isa))的指令。指令集是计算机架构的关于编程的部分,并且一般包括原生数据类型、指令、寄存器架构、寻址模式、存储器架构、中断和异常处置以及外部输入和输出(i/o)。应当注意,术语“指令”在本文中可以指宏指令或指微指令,该宏指令例如,提供给处理器供执行的指令,该微指令例如,由处理器的解码器对宏指令解码所产生的指令。

技术实现思路

技术特征:

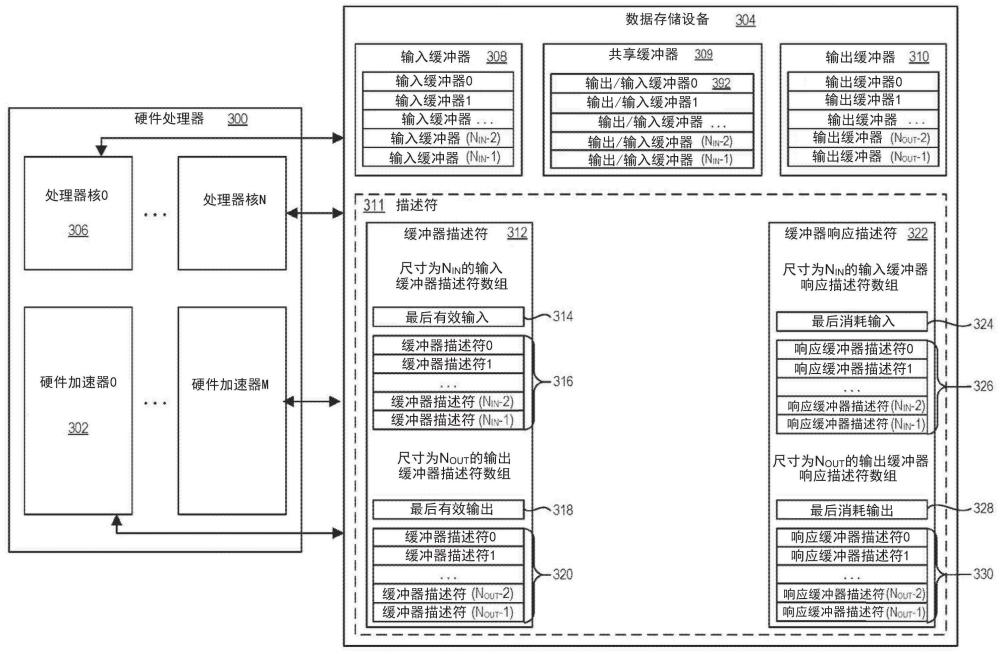

1.一种用于生成输出数据以及消耗输入数据的第一硬件加速器(302);

2.如权利要求1所述的第一硬件加速器(302),其中,所述第一硬件加速器(302)用于将所述输出缓冲器描述符数组的最后有效输出条目的索引与所述输出缓冲器响应描述符数组的最后消耗输出响应条目的索引进行比较,以确定所述第一硬件加速器(302)何时用于执行以生成进入所述多个共享缓冲器(309)的输出数据。

3.如权利要求1或2所述的第一硬件加速器(302),其中,所述第一硬件加速器(302)用于将所述输入缓冲器描述符数组的最后有效输入条目的索引与所述输入缓冲器响应描述符数组的最后消耗输入响应条目的索引进行比较,以确定所述第一硬件加速器(302)何时用于执行以消耗来自所述多个共享缓冲器(309)的输入数据。

4.如权利要求1至3中任一项所述的第一硬件加速器(302),其中,所述第一硬件加速器(302)用于:用所述输出数据加载所述多个共享缓冲器(309);以及加载所述输出缓冲器响应描述符数组中用于每个相应的被消耗的共享缓冲器(309)的对应响应条目。

5.如权利要求1至4中任一项所述的第一硬件加速器(302),其中,所述第一硬件加速器(302)用于:加载所述输入缓冲器响应描述符数组中用于每个相应的被消耗的共享缓冲器(309)的对应响应条目。

6.如权利要求1至5中任一项所述的第一硬件加速器(302),其中,所述输入缓冲器描述符数组中的条目各自都包括存储在相应共享缓冲器(309)中的输入数据的尺寸,所述输入缓冲器响应描述符数组中的对应响应条目各自都包括相应共享缓冲器(309)中剩余的输入数据的尺寸,所述输出缓冲器描述符数组中的条目各自都包括能用于存储输出数据的相应共享缓冲器(309)的尺寸,并且所述输出缓冲器响应描述符数组中的对应响应条目各自都包括存储在相应共享缓冲器(309)中的输出数据的尺寸。

7.如权利要求1至6中任一项所述的第一硬件加速器(302),其中,所述第一硬件加速器(302)由包括核心(306)的硬件处理器(300)构成,其中所述核心(306)用于:分配所述多个共享缓冲器(309);以及加载所述输入缓冲器描述符数组中用于每个相应共享缓冲器(309)的条目。

8.如权利要求1至7中任一项所述的第一硬件加速器(302),其中,所述核心(306)用于:加载所述输出缓冲器描述符数组中用于每个相应的共享缓冲器(309)的条目。

9.一种方法,包括:

10.如权利要求9所述的方法,进一步包括由所述第一硬件加速器(302)将所述输出缓冲器描述符数组的最后有效输出条目的索引与所述输出缓冲器响应描述符数组的最后消耗输出响应条目的索引进行比较,以确定所述第一硬件加速器(302)何时用于执行以生成进入所述多个共享缓冲器(309)的输出数据。

11.如权利要求9或10所述的方法,进一步包括由所述第一硬件加速器(302)与第二硬件加速器(302)一起将所述输入缓冲器描述符数组的最后有效输入条目的索引与所述输入缓冲器响应描述符数组的最后消耗输入响应条目的索引进行比较,以确定所述第一硬件加速器(302)何时用于执行以消耗来自所述多个共享缓冲器(309)的输入数据。

12.如权利要求9至11中任一项所述的方法,进一步包括:分配所述多个共享缓冲器(309);以及加载所述输入缓冲器描述符数组中用于每个相应共享缓冲器(309)的条目。

13.如权利要求12所述的方法,进一步包括:加载所述输出缓冲器响应描述符数组中用于每个相应的共享缓冲器(309)的条目。

14.如权利要求9至13中任一项所述的方法,进一步包括:用所述输出数据加载所述多个共享缓冲器(309);以及加载所述输出缓冲器响应描述符数组中用于每个相应的被消耗的共享缓冲器(309)的对应响应条目。

15.如权利要求9至14中任一项所述的方法,进一步包括:提供所述输入缓冲器描述符数组中的条目,其各自都包括存储在相应共享缓冲器(309)中的输入数据的尺寸;提供所述输入缓冲器响应描述符数组中的对应响应条目,其各自都包括相应共享缓冲器(309)中剩余的输入数据的尺寸;提供所述输出缓冲器描述符数组中的条目,其各自都包括能用于存储输出数据的相应共享缓冲器(309)的尺寸;以及提供所述输出缓冲器响应描述符数组中的对应响应条目,其各自都包括存储在相应共享缓冲器(309)中的输出数据的尺寸。

16.一种方法,包括:

17.一种处理器核,包括:

18.如权利要求17所述的处理器核,其特征在于,所述向量单元是16宽向量处理单元(vpu),所述vpu执行整型、单精度浮点以及双精度浮点指令中的一个或多个。

19.如权利要求18所述的处理器核,其特征在于,所述vpu通过混合单元支持对寄存器输入的混合、通过数值转换单元支持数值转换,并通过复制单元支持对存储器输入的复制。

技术总结

描述了与转移操作有关的方法和装置。在一个实施例中,硬件处理器包括:核,用于执行线程并转移操作;以及第一硬件加速器和第二硬件加速器,用于执行该操作,其中,第一硬件加速器和第二硬件加速器耦合至多个共享缓冲器、具有用于每个相应共享缓冲器的条目的第二硬件加速器的输入缓冲器描述符数组、具有用于每个相应共享缓冲器的对应响应条目的第二硬件加速器的输入缓冲器响应描述符数组、具有用于每个相应共享缓冲器的条目的第一硬件加速器的输出缓冲器描述符数组、以及具有用于每个相应共享缓冲器的对应响应条目的第一硬件加速器的输出缓冲器响应描述符数组,多个共享缓冲器用于存储来自第一硬件加速器的输出数据并将该输出数据作为输入数据提供给第二硬件加速器。

技术研发人员:T·G·德赖斯代尔,V·戈帕尔,J·D·吉尔福德

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/3/31

- 还没有人留言评论。精彩留言会获得点赞!