一种协处理器以及加解密方法与流程

本申请涉及安全,特别涉及一种协处理器以及加解密方法。

背景技术:

1、随着安全芯片在嵌入式行业应用越来越广泛,安全芯片对数据的处理速度和功耗指标逐渐成为其应用中的技术瓶颈,尤其体现在端设备的低功耗应用。其中,协处理器的性能对安全芯片的性能影响是较大的,如何提升协处理器的性能是目前亟待解决的问题。

技术实现思路

1、有鉴于此,本申请的目的在于提供一种协处理器以及加解密方法,能够提升协处理器的性能。其具体方案如下:

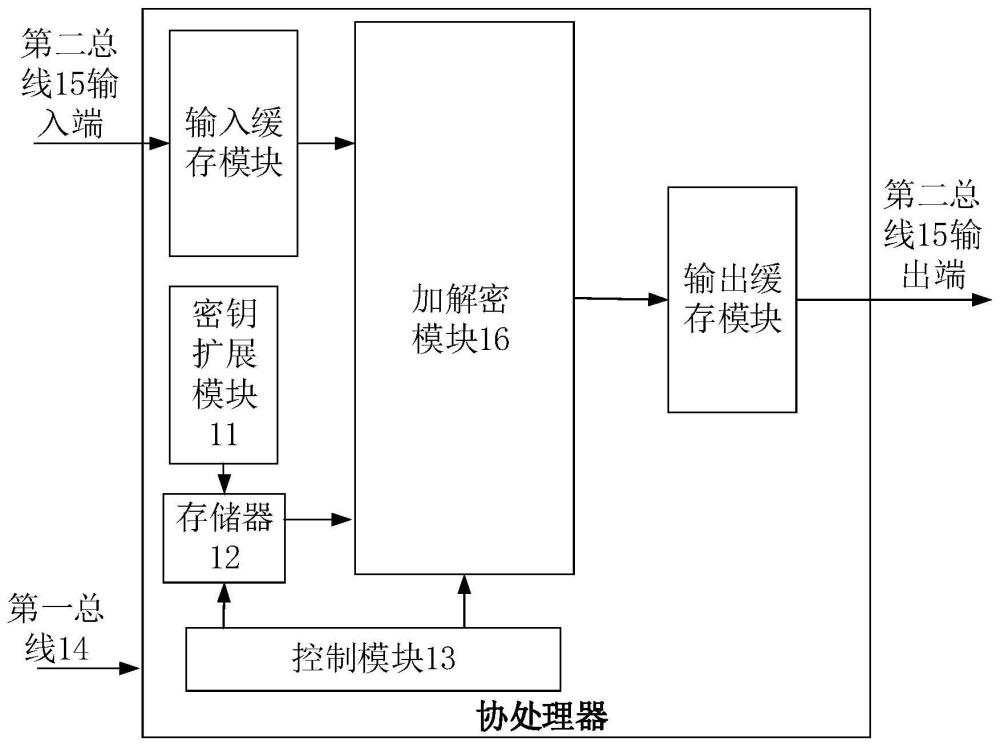

2、第一方面,本申请公开了一种协处理器,包括:

3、密钥扩展模块,用于对主密钥进行扩展,得到轮子密钥;

4、与所述密钥扩展模块连接的存储器,用于存储所述轮子密钥;

5、控制模块以及与所述控制模块连接的第一总线,所述第一总线用于传输寄存器配置信号,以配置所述控制模块中的寄存器;

6、第二总线,所述第二总线包括用于输入数据的输入端以及用于输出数据的输出端;

7、与所述存储器以及所述控制模块连接的加解密模块,用于调用所述存储器中的所述轮子密钥并基于所述寄存器中的配置,将输入数据进行加密或解密处理,得到输出数据。

8、可选的,还包括:

9、与所述输入端连接的输入缓存模块,用于缓存所述输入数据;所述输入缓存模块采用乒乓fifo缓存。

10、可选的,还包括:

11、与所述加解密模块以及所述输出端连接的输出缓存模块,用于缓存所述加解密模块的输出数据;所述输出缓存模块采用乒乓fifo缓存。

12、可选的,所述加解密模块包括一个或多个aes核。

13、可选的,所述加解密模块,具体用于:

14、当存在多个aes核,调用所述存储器中的所述轮子密钥,并利用所述寄存器中配置的核数量个aes核,将输入数据进行加密或解密处理,得到输出数据。

15、可选的,所述加解密模块,具体用于:

16、调用所述存储器中的所述轮子密钥,并基于所述寄存器中配置的aes模式,将输入数据进行加密或解密处理,得到输出数据。

17、可选的,所述第一总线为ahb总线,所述第二总线为axi总线。

18、第二方面,本申请公开了一种加解密方法,应用于协处理器,包括:

19、对主密钥进行扩展,得到轮子密钥;

20、将所述轮子密钥存储至存储器;

21、通过第一总线获取寄存器的配置信号;

22、通过第二总线获取输入数据,调用所述存储器中的所述轮子密钥并基于所述寄存器中的配置,将所述输入数据进行加密或解密处理,得到输出数据并通过第二总线输出所述输出数据。

23、可选的,所述通过第二总线获取输入数据,包括:

24、通过第二总线获取输入数据,并利用输入缓存模块缓存所述输入数据所述输入缓存模块采用乒乓fifo缓存;

25、所述方法还包括:在得到输出数据之后,将所述输出数据缓存至输出缓存模块。

26、可选的,所述调用所述存储器中的所述轮子密钥并基于所述寄存器中的配置,将所述输入数据进行加密或解密处理,包括:

27、调用所述存储器中的所述轮子密钥并基于所述寄存器中配置的aes核数量以及aes模式,将所述输入数据进行加密或解密处理。

28、通过以上方案可知,本申请提供了一种协处理器,包括:密钥扩展模块,用于对主密钥进行扩展,得到轮子密钥;与所述密钥扩展模块连接的存储器,用于存储所述轮子密钥;控制模块以及与所述控制模块连接的第一总线,所述第一总线用于传输寄存器配置信号,以配置所述控制模块中的寄存器;第二总线,所述第二总线包括用于输入数据的输入端以及用于输出数据的输出端;与所述存储器以及所述控制模块连接的加解密模块,用于调用所述存储器中的所述轮子密钥并基于所述寄存器中的配置,将输入数据进行加密或解密处理,得到输出数据。

29、可见,本申请的有益效果为:采用第一总线配置控制模块的寄存器,采用第二总线传输数据,也即采用两套总线架构,两套总线独立工作且互不干扰,并且,先利用密钥扩展模块对主密钥进行扩展,得到轮子密钥,将轮子密钥存储至存储器,在进行加解密时,直接调用存储器中的轮子密钥,无需每次都进行密钥扩展,保障加解密高效进行,能够提升协处理器的性能。

30、相应地,本申请提供的一种加解密方法,也同样具有上述技术效果。

技术特征:

1.一种协处理器,其特征在于,包括:

2.根据权利要求1所述的协处理器,其特征在于,还包括:

3.根据权利要求1所述的协处理器,其特征在于,还包括:

4.根据权利要求1所述的协处理器,其特征在于,所述加解密模块包括一个或多个aes核。

5.根据权利要求4所述的协处理器,其特征在于,所述加解密模块,具体用于:

6.根据权利要求4所述的协处理器,其特征在于,所述加解密模块,具体用于:

7.根据权利要求1所述的协处理器,其特征在于,所述第一总线为ahb总线,所述第二总线为axi总线。

8.一种加解密方法,其特征在于,应用于协处理器,包括:

9.根据权利要求8所述的加解密方法,其特征在于,所述通过第二总线获取输入数据,包括:

10.根据权利要求8所述的加解密方法,其特征在于,所述调用所述存储器中的所述轮子密钥并基于所述寄存器中的配置,将所述输入数据进行加密或解密处理,包括:

技术总结

本申请公开了一种协处理器以及加解密方法,应用于安全技术领域,所述协处理器,包括:密钥扩展模块,用于对主密钥进行扩展,得到轮子密钥;与所述密钥扩展模块连接的存储器,用于存储所述轮子密钥;控制模块以及与所述控制模块连接的第一总线,所述第一总线用于传输寄存器配置信号,以配置所述控制模块中的寄存器;第二总线,所述第二总线包括用于输入数据的输入端以及用于输出数据的输出端;与所述存储器以及所述控制模块连接的加解密模块,用于调用所述存储器中的所述轮子密钥并基于所述寄存器中的配置,将输入数据进行加密或解密处理,得到输出数据。采用两套总线架构,先对主密钥进行扩展并存储,后续直接调用,能够提升协处理器的性能。

技术研发人员:万刘蝉,肖佐楠,钟明富,郑茳,匡启和,汪建强

受保护的技术使用者:苏州国芯科技股份有限公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!