伪装电路、集成电路芯片和伪装电路的设计方法

本申请涉及集成电路,特别是涉及伪装电路、集成电路芯片和伪装电路的设计方法。

背景技术:

1、逆向工程是一种产品设计技术再现过程。在集成电路领域,容易受到逆向工程、未授权的克隆以及由于木马插入导致的知识产权盗窃的影响。例如,逆向工程攻击者可以利用成像技术,对集成电路的物理布局进行逆向工程,获得电路的完整门级网表。因此需要对集成电路进行伪装设计。在相关技术中,通常采用虚拟触点设计伪装单元,即通过对逆向工程中无法区分的真实触点和虚拟触点的不同配置,创建能够实现不同布尔函数功能的伪装单元,以此来实现电路结构伪装。然而,上述方法需要大量晶体管、占用芯片内部较大面积才能组成有效的伪装电路,对伪装单元的制造工艺较为复杂,制造成本过高。

2、目前针对相关技术中集成电路伪装成本高的问题,尚未提出有效的解决方案。

技术实现思路

1、本申请实施例提供了一种伪装电路、集成电路芯片和伪装电路的设计方法,以至少解决相关技术中集成电路伪装成本高的问题。

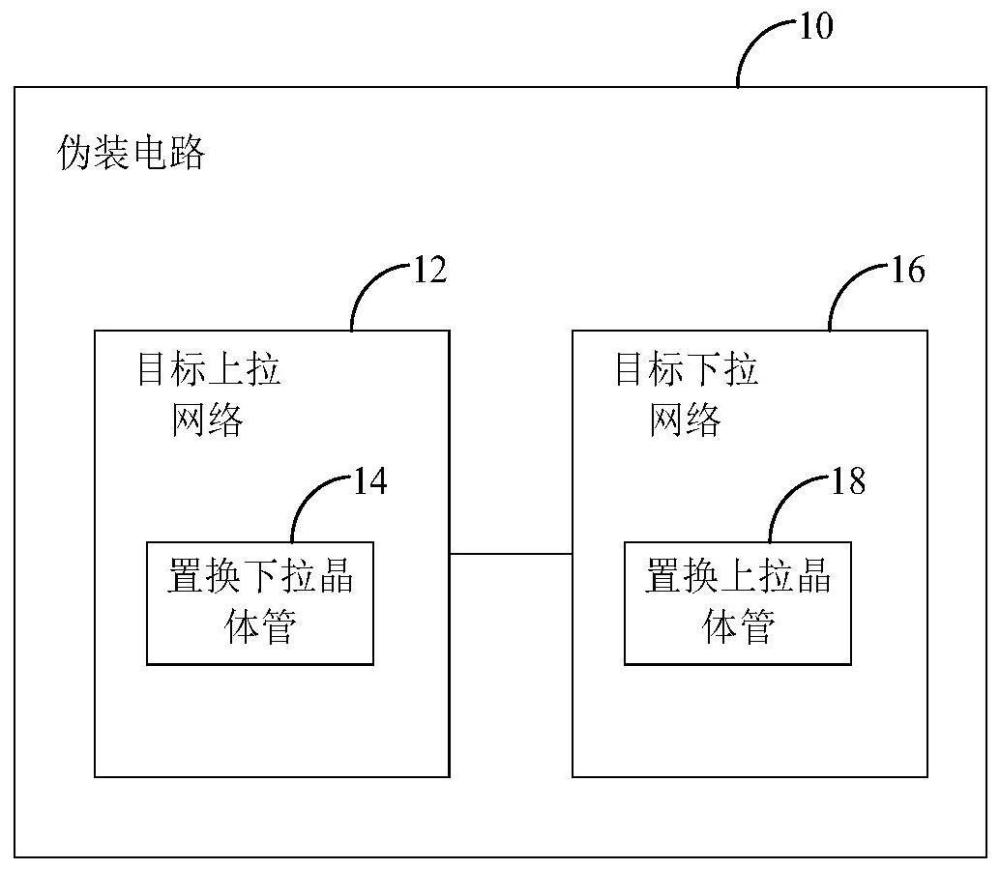

2、第一方面,本申请实施例提供了一种伪装电路,所述电路包括:目标上拉网络和目标下拉网络;

3、所述目标上拉网络和所述目标下拉网络,通过将标准上拉网络中的置换上拉晶体管的位置,与标准下拉网络中的置换下拉晶体管的位置互换形成;

4、其中,所述置换上拉晶体管的输入信号与所述置换下拉晶体管的输入信号相同;且所述置换上拉晶体管不与电源电压直连,或者所述置换下拉晶体管不与接地电压直连。

5、在其中一些实施例中,所述标准上拉网络还包括保持上拉晶体管,且所述标准下拉网络还包括保持下拉晶体管;所述保持上拉晶体管的输入信号与所述保持下拉晶体管的输入信号相同。

6、在其中一些实施例中,所述保持上拉晶体管与所述电源电压直连,或者所述保持下拉晶体管与所述接地电压直连。

7、在其中一些实施例中,所述标准上拉网络和所述标准下拉网络构成二输入标准逻辑门电路;其中,所述标准上拉网络包括两个上拉晶体管,且所述标准下拉网络包括两个下拉晶体管。

8、在其中一些实施例中,所述置换上拉晶体管,为所述上拉晶体管中不与所述电源电压直连的晶体管,且所述置换下拉晶体管,为所述下拉晶体管中与所述置换上拉晶体管的输入信号相同的晶体管;或者;

9、所述置换下拉晶体管,为所述下拉晶体管中不与所述接地电压直连的晶体管,且所述置换上拉晶体管,为所述上拉晶体管中与所述置换上拉晶体管的输入信号相同的晶体管。

10、在其中一些实施例中,所述标准上拉网络和所述标准下拉网络构成三输入标准逻辑门电路;其中,所述标准上拉网络包括三个上拉晶体管,且所述标准下拉网络包括三个下拉晶体管;

11、所述置换上拉晶体管,为所述上拉晶体管中的一个或两个晶体管,且所述置换下拉晶体管,为所述下拉晶体管中的一个或两个晶体管。

12、在其中一些实施例中,所述目标上拉网络包括所述置换下拉晶体管,所述置换下拉晶体管为nmos管;

13、所述目标下拉网络包括置换上拉晶体管,所述置换上拉晶体管为pmos管。

14、第二方面,本申请实施例提供了一种集成电路芯片,该集成电路芯片包括如上述第一方面所述的伪装电路。

15、第三方面,本申请实施例提供了一种伪装电路的设计方法,所述方法包括:

16、确定标准上拉网络中的至少一个置换上拉晶体管,以及标准下拉网络中的至少一个置换下拉晶体管;

17、其中,所述置换上拉晶体管的输入信号与所述置换下拉晶体管的输入信号相同;且所述置换上拉晶体管不与电源电压直连,或者所述置换下拉晶体管不与接地电压直连;

18、将所述置换上拉晶体管的位置与所述置换下拉晶体管的位置互换,形成目标上拉网络和目标下拉网络;所述伪装电路,包括所述目标上拉网络和所述目标下拉网络。

19、在其中一些实施例中,上述确定标准上拉网络中的至少一个置换上拉晶体管,以及标准下拉网络中的至少一个置换下拉晶体管,包括:

20、获取预设的电路逻辑需求;

21、基于所述电路逻辑需求,确定所述置换上拉晶体管和所述置换下拉晶体管。

22、相比于相关技术,本申请实施例提供的伪装电路、集成电路芯片和伪装电路的设计方法,其中,伪装电路包括:目标上拉网络和目标下拉网络;该目标上拉网络和该目标下拉网络,通过将标准上拉网络中的置换上拉晶体管的位置,与标准下拉网络中的置换下拉晶体管的位置互换形成;其中,该置换上拉晶体管的输入信号与该置换下拉晶体管的输入信号相同;且该置换上拉晶体管不与电源电压直连,或者该置换下拉晶体管不与接地电压直连,解决了集成电路伪装成本高的问题。

23、本申请的一个或多个实施例的细节在以下附图和描述中提出,以使本申请的其他特征、目的和优点更加简明易懂。

技术特征:

1.一种伪装电路,其特征在于,所述电路包括:目标上拉网络和目标下拉网络;

2.根据权利要求1所述的伪装电路,其特征在于,所述标准上拉网络还包括保持上拉晶体管,且所述标准下拉网络还包括保持下拉晶体管;所述保持上拉晶体管的输入信号与所述保持下拉晶体管的输入信号相同。

3.根据权利要求2所述的伪装电路,其特征在于,所述保持上拉晶体管与所述电源电压直连,或者所述保持下拉晶体管与所述接地电压直连。

4.根据权利要求1所述的伪装电路,其特征在于,所述标准上拉网络和所述标准下拉网络构成二输入标准逻辑门电路;其中,所述标准上拉网络包括两个上拉晶体管,且所述标准下拉网络包括两个下拉晶体管。

5.根据权利要求4所述的伪装电路,其特征在于,所述置换上拉晶体管,为所述上拉晶体管中不与所述电源电压直连的晶体管,且所述置换下拉晶体管,为所述下拉晶体管中与所述置换上拉晶体管的输入信号相同的晶体管;或者;

6.根据权利要求1所述的伪装电路,其特征在于,所述标准上拉网络和所述标准下拉网络构成三输入标准逻辑门电路;其中,所述标准上拉网络包括三个上拉晶体管,且所述标准下拉网络包括三个下拉晶体管;

7.根据权利要求1至6任一项所述的伪装电路,其特征在于,所述目标上拉网络包括所述置换下拉晶体管,所述置换下拉晶体管为nmos管;

8.一种集成电路芯片,其特征在于,所述集成电路芯片包括如权利要求1至7任一项所述的伪装电路。

9.一种伪装电路的设计方法,其特征在于,所述方法包括:

10.根据权利要求9所述的设计方法,其特征在于,所述确定标准上拉网络中的至少一个置换上拉晶体管,以及标准下拉网络中的至少一个置换下拉晶体管,包括:

技术总结

本申请涉及一种伪装电路、集成电路芯片和伪装电路的设计方法,其中,该伪装电路包括:目标上拉网络和目标下拉网络;该目标上拉网络和该目标下拉网络,通过将标准上拉网络中的置换上拉晶体管的位置,与标准下拉网络中的置换下拉晶体管的位置互换形成;其中,该置换上拉晶体管的输入信号与该置换下拉晶体管的输入信号相同;且该置换上拉晶体管不与电源电压直连,或者该置换下拉晶体管不与接地电压直连。通过本申请,解决了集成电路伪装成本高的问题。

技术研发人员:沈浩頲,周建文

受保护的技术使用者:浙江大学杭州国际科创中心

技术研发日:

技术公布日:2024/5/6

- 还没有人留言评论。精彩留言会获得点赞!